高计数率气体探测器读出电子学原型机研制

2021-08-02孙志朋佘乾顺赵红赟蒲天磊袁江月

孙志朋,佘乾顺,赵红赟,千 奕,*,孔 洁,蒲天磊,苏 弘,袁江月

(1.中国科学院 近代物理研究所,甘肃 兰州 730000;2.中国科学院大学 核科学与技术学院,北京 100049)

低温高密核物质测量谱仪(CEE)是适用于兰州重离子研究装置-冷却储存环(HIRFL-CSR)能区[1]重离子碰撞和质子-重离子碰撞测量的带电粒子谱仪,该谱仪由若干子探测器系统组成。高计数率(10 kHz)、高接受度的大型时间投影室(TPC)探测器是其中之一,包含有15 000个读出通道。该探测器被用来鉴别带电粒子,并测量轻带电粒子的三维径迹,其测量的主要反应产物包括π、p、d、t、3He、4He。由于探测器计数率高、通道多等特点,目前的读出电子学无法满足需求,因此迫切需研制适用于高计数率,且具有高集成度、低功耗、高分辨的新型读出电子学。本文引进前端读出专用集成电路(ASIC)芯片SAMPA[2-3],研制高计数率气体探测器读出电子学原型机,可解决HIRFL-CSR能区重离子碰撞和质子-重离子碰撞实验中的带电粒子谱仪计数率、功耗、串扰、堆积等问题,实现对高计数率TPC探测器信号的读出。

1 原型机系统设计与实现

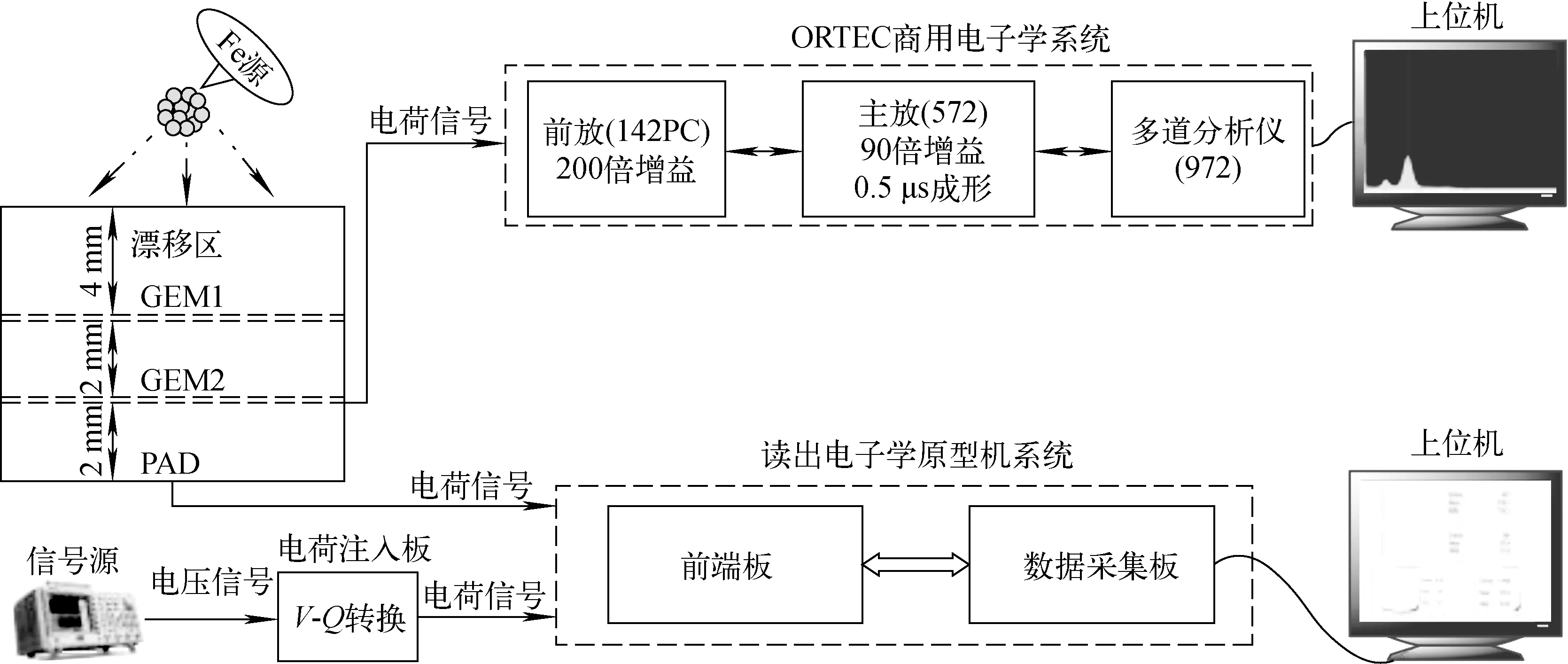

读出电子学原型机系统主要由前端板、数据采集(DAQ)板和上位机构成,如图1所示。

图1 读出电子学原型机系统Fig.1 Readout electronics prototype system

1.1 前端板设计

前端板负责接收来自探测器输出的微弱电荷信号,并实现对电荷信号的积分、整形、模数转换、数据压缩及打包等功能。本工作兼顾功能、功耗和集成度等需求,在前端板的设计中采用一款前端读出芯片SAMPA。前端板电路结构如图2所示,其主要包括SAMPA芯片、过压保护电路、电源管理模块、适配网络、芯片地址配置模块、内部时钟配置模块、外围滤波网络、输入高速连接器、输出高速连接器和JTAG测试接口。过压保护电路用来防止因TPC探测器打火而产生的大信号对前端电路造成破坏;电源管理模块由低压线性稳压器(LDO)及其外围电路组成,可提供前端板上各电路模块所需的低噪声的供电电压和参考电压;适配网络可实现低压差分信号(LVDS)到可扩展低压信号(SLVS)的电平转换并增强信号驱动能力,由于SAMPA芯片的输入输出信号均基于SLVS电平标准[4-5],而DAQ板上的Cyclone V型FPGA[6-8]的I/O管脚中,仅输入管脚支持基于SLVS电平的信号,输出管脚不支持基于SLVS电平的信号,因此从DAQ板上的FPGA输出给SAMPA芯片的控制、时钟、触发等信号均基于LVDS电平标准,需通过适配网络进行电平转换;芯片地址配置模块可实现对芯片硬件地址的配置;内部时钟配置模块用于配置片内时钟管理单元产生SAMPA芯片内部所需的各种时钟信号;外围滤波网络由滤波电容组成,实现对芯片各管脚的滤波,从而消除噪声干扰;JTAG测试接口用于实现SAMPA芯片自带的JTAG测试功能。

图2 前端板电路结构Fig.2 Circuit structure of front-end board

SAMPA芯片是专门为TPC读出研发的一款大规模的模拟数字混合芯片[9-12],具有高计数率、高集成度、低功耗等特点,其主要性能指标参数列于表1,SAMPA芯片内部结构如图3所示。单片SAMPA集成32路输入通道和11条输出链路,单通道内包含电荷灵敏前放(CSA)、成形电路(Shaper)、驱动电路(Non-Inverting stage)、10 bit精度的模数转换器(ADC)、功能复杂的数字信号处理器(DSP)、慢控模块和接口电路等。

图3 SAMPA芯片内部结构Fig.3 Internal structure of SAMPA chip

表1 SAMPA芯片参数Table 1 Parameter of SAMPA chip

前端板接收到探测器输出的电荷信号后,被SAMPA芯片中的CSA放大并转换为电压信号,然后通过Shaper整形为准高斯电压信号,再送入10 MHz采样率的ADC进行数字化。DSP包含3级基线修正,可对数字化后的信号进行实时处理,从而消除信号扰动、脉冲波形的畸变及由于温度变化带来的信号基线变化[13]。经过基线处理后,DSP中的压缩级对数据进行压缩,并将压缩后的数据送入数据打包级打包后暂存,最终通过11条链路输出到后端的DAQ板[14]。

1.2 DAQ板固件设计及上位机

DAQ板以Cyclone V SX型FPGA芯片为核心,搭载1片1 GB的DDR3芯片,并配置有USB慢控接口和千兆以太网接口。Cyclone V SX型FPGA的输入端口支持SLVS标准,可直接接收SAMPA芯片异步输出的速度高达320 Mbps的SLVS信号;FPGA带有片上处理器系统,其内部由可编程逻辑(PL)和内嵌硬核处理器(HPS)两部分构成,PL端和HPS端通过Avalon总线进行交互[15]。图4为DAQ板固件结构示意图,DAQ板的固件可划分为3大模块,分别为数据处理模块、指令控制模块和数据传输模块。其中,数据处理模块和指令控制模块在PL端实现,数据传输模块在HPS端实现。数据处理模块负责接收来自SAMPA芯片的数据,并进行一系列在线处理,然后将有效数据通过Avalon总线传输到HPS端;HPS端的数据传输模块通过千兆以太网将数据传输到上位机后进行存储;上位机通过USB-UART下发的控制指令到达DAQ固件后,指令控制模块根据指令完成前端板上各芯片的参数配置、触发处理、状态监测等操作。

图4 DAQ板固件结构示意图Fig.4 Scheme of DAQ system firmware

数据处理模块内部包括同步子模块、串并转换子模块、在线判选子模块、FIFO子模块和轮询子模块。同步子模块负责监测SAMPA的11条输出链路状态,并异步接收芯片输出的数据。串并转换子模块将接收到的串行数据转换为适合于后端操作系统处理的64 bit宽度的数据。在线判选子模块对接收到的数据包进行判选,丢弃无效包,将有效数据包写入FIFO进行缓存。轮询子模块将11条链路对应的11个缓存FIFO分为4组,分别以轮询的方式进行可靠读出,在读出的过程中监测并丢弃因FIFO溢出而导致的不完整包,之后通过4个Avalon总线端口将数据传输到HPS端,进行DDR缓存处理并最终上传。HPS端利用外挂DDR芯片进行内存映射,用于缓存数据并运行Linux操作系统,数据传输模块是1个运行在Linux操作系统下的代码模块,该模块建立基于TCP/IP传输协议的传输链路并监测以太网状态,将数据流进行可靠传输。

上位机通过USB-UART下发的指令流经过Avalon总线的桥接送到指令控制模块,该模块含有IIC驱动、触发处理和SAMPA管脚控制3个子模块。IIC驱动子模块根据收到的指令参数,产生满足IIC时序的信号,设置前端板上SAMPA芯片内部的寄存器参数;触发处理子模块接收来自外部的触发信号并处理为SAMPA芯片可识别的信号,输出给前端板并触发SAMPA芯片开始工作;管脚控制子模块通过控制SAMPA芯片的部分管脚,选择芯片的工作模式并对部分参数进行设置。

2 测试与讨论

2.1 实验室性能测试

电子学系统基线稳定性、通道积分非线性和通道能量分辨是判定系统性能的关键指标。本工作利用信号源注入信号对读出电子学原型机系统的性能指标进行了测试。在测试过程中,电子学原型机系统被置于屏蔽盒内,以屏蔽外部干扰。

1) 原型机系统基线稳定性

在无输入的情况下,采集原型机系统32个通道的基线噪声信号,在对共计超过35万个数据包进行分析后,得到的结果列于表2。可看出,系统所有通道的基线变化稳定,均方根(RMS)均小于0.95个ADC道(对应0.1 fC电荷量),满足CEE TPC系统对读出电子学提出的低噪声需求。

表2 基线噪声测试结果Table 2 Baseline noise test result

2) 原型机系统能量分辨及积分非线性

设定信号源输出频率为10 kHz的指数衰减信号,通过电荷注入板转换为电荷信号后输入到SAMPA芯片中,进行能量分辨及积分非线性测试。设置SAMPA芯片的CSA增益为20 mV/fC,整形级达峰时间为160 ns,给定输入电荷量为66 fC时,对输出信号采集超过10 000个数据包。经波形拟合和数据分析处理,得到信号的能谱如图5所示。其中系统的能量分辨为1.4个ADC道(对应电荷量为0.14 fC)。

图5 输出信号能谱Fig.5 Energy spectrum of output signal

改变信号幅度,在2.2~99 fC范围内,共给出10个输入电荷量,每个输入对应的输出波形被ADC采集超过10 000个数据包。对输出的波形进行拟合得到其对应的最大幅度信息并进行分析,进而得到系统在输入动态范围内的积分非线性。选取通道0的分析结果进行展示,该通道输出电压(ADC道值)的线性拟合结果如图6a所示,积分非线性好于0.24%;残差分布如图6b所示,其变化小于±2ADC道(对应电荷量为±0.2 fC)。

a——线性拟合结果;b——拟合残差分布图6 读出电子学原型机系统积分线性Fig.6 Linearity of readout electronics prototype system

2.2 与GEM-TPC探测器联合测试

本文利用55Fe放射源对原型机系统和商用电子学系统进行了能量分辨率、计数率等指标的对比测试,测试系统结构如图7所示,包括基于双层气体电子倍增器(GEM)的TPC探测器、读出电子学原型机系统、ORTEC商用电子学系统。

图7 测试系统结构Fig.7 Structure of test system

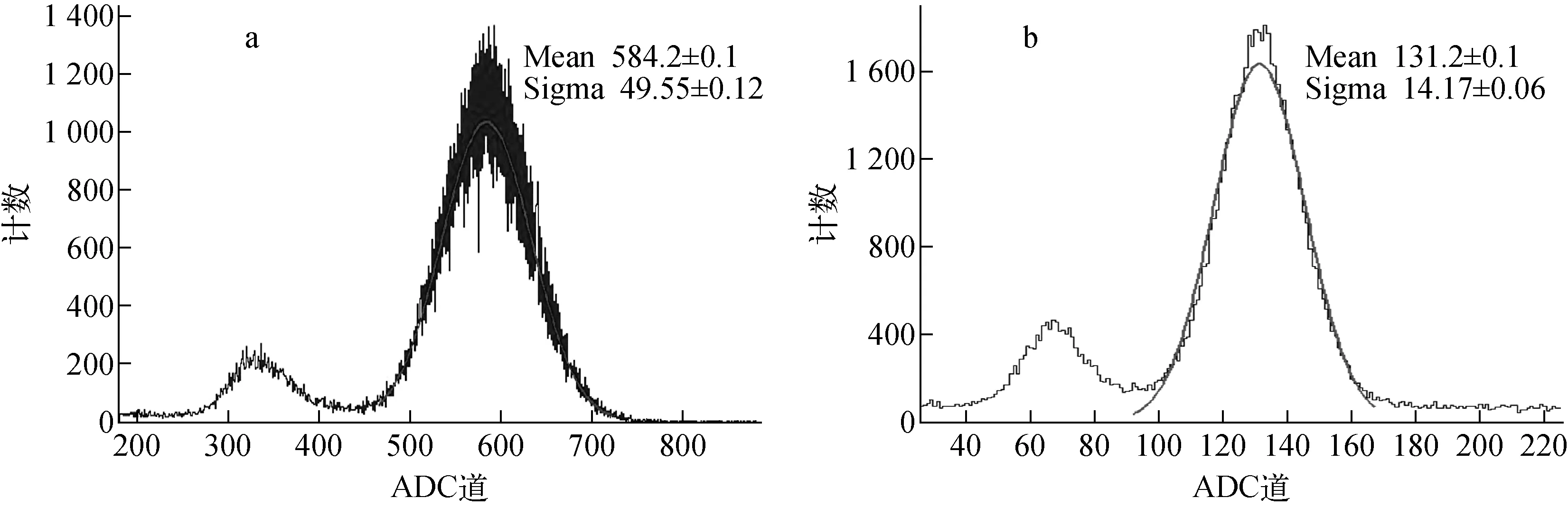

2.3 能量分辨率测试结果

测试前,利用定标器测得55Fe放射源事件率约为11 kHz。读出电子学原型机系统和ORTEC商用电子学系统同时测试,读出电子学原型机系统通道0的测试结果如图8a所示。利用式(1)计算得到电子学的能量分辨率R1为23.52%;在相同条件下商用电子学系统测试结果如图8b所示,由于商用电子学系统基线接近0,可忽略不计,利用式(2)求得ORTEC商用电子学系统的能量分辨率R2为25.49%。测试结果表明,在相同条件下,读出电子学原型机系统的能量分辨率优于商用电子学系统。

(1)

(2)

其中:Baseline为原型机系统基线噪声值;Mean为电子学测得的能谱经高斯拟合后得到的中心值。

a——读出电子学原型机系统;b——ORTEC商用电子学系统图8 55Fe放射源测试能谱Fig.8 Energy spectrum obtained by 55Fe source

调整55Fe放射源的位置,利用定标器测得事例率约为23 kHz,读出电子学原型机系统测得的能谱如图9所示。利用式(1)计算求得原型机系统的能量分辨率R3为22.79%,在计数率增加1倍的情况下,原型机系统的能量分辨率没有变差,说明系统可适用于计数率高于20 kHz的GEM-TPC探测器的读出。

图9 读出电子学原型机系统能谱Fig.9 Energy spectrum of readout electronics prototype system

3 结论

本文介绍了一套适用于高计数率TPC探测器的读出电子学原型机系统的设计与实现。利用构建的测试系统对原型机的基线噪声、积分非线性、能量分辨及高计数率下的工作性能进行了测试,结果表明系统具有良好的性能。通过与探测器进行联合测试,验证了电子学系统在实际工作中的性能指标良好,能满足CEE中TPC探测器的读出需求。该系统结构紧凑,通用灵活,指标先进,为后续CEE中TPC探测器前端电子学的设计提供了技术参考,也为CEE中TPC实验探测系统的建造提供了重要技术保障。

感谢挪威Bergen大学和法国IPN Orsay实验室对本工作提供的技术支持。