迎接移动SoC新世代

2021-07-13张平

张平

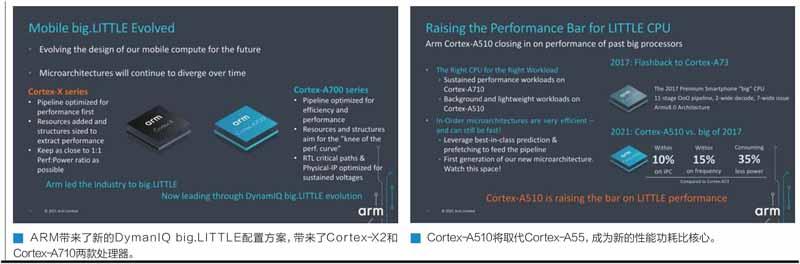

2021年堪称ARM的技术变革之年。继年初发布了全新的Armv9架构后,4月ARM又一并带来了NeoverseV1和NeoverseN2两个基础架构IP。5月底,ARM一口气发布了三款全新微架构—Cortex-X2、Cortex-A710和Cortex-A510,同时面世的还有全新的Mali-G710、Mali-G610、Mali-G510、Mali-G310系列移动GPU以及相关的总线架构等。这些架构是如此重要,以至于它们的设计和最终表现决定了Android用户在未来一年甚至数年的应用体验,因此我们有必要详细了解这些架构的功能和设计情况。不过由于内容较多,本文只介绍有关新的CPU微架构的情况,在之后本刊将继续介绍此次发布的移动GPU架构的情况。

新名称、新变化:ARM启用全新的三位数命名方式

之前ARM在产品命名一直使用的是2位数,比如Cortex-A76、Cortex-A55。从本代开始,ARM启用了三位数命名的方式,其中性能最强的大核心依旧是“Cortex-X”系列,接下來的性能核心采用了“Cortex-7XX”取代之前的“Cortex-7X”,小核心则用“Cortex-5XX”取代了“Cortex-5X”。

这次命名变化看起来只是在原来的两位数命名尾端多加了一个0,不过实际上三位数命名的优势在于可以区分出更多的分支型号。比如本次发布的Cortex-A710,未来可能出现改进版本的“Cortex-A715”,而全代演进产品可以使用“Cortex-A720”这样的命名,这样方便ARM进行版本区分和市场宣传。

本次发布的三款CPU微架构中,Cortex-X2是用于取代Cortex-X1的全新架构,ARM希望它能够使用在诸如笔记本电脑甚至台式机这样的设备中,属于性能优先的架构。Cortex-A710则是性能和功耗的平衡选择,用于取代目前的Cortex-A78。Cortex-A510则是用于取代2017年发布的经典小核心架构Cortex-A55,实现最好的性能功耗比。除了上述微架构外,ARM本次还发布了新的DSU-110、CI-700以及NI-700等功能性组件,本文也对其一并进行了介绍。

另外值得一提的是,随着Armv9.0指令集的发布,ARM引入包括SVE2SIMD矢量扩展、64位架构等功能,随之而来的就是对AArch32执行模式的全面弃用。与此同时,谷歌在2019年就宣布自己的应用商店GooglePlay只接受64位应用程序,并且即将在2021年中期停止向64位兼容设备提供32位应用程序,这意味着整个行业都在全面转向64位。与此相应的是,ARM目前提供的三款全新微架构全面实现了对AArch64的支持,Cortex-X2和Cortex-A510是“AArch64-only”的产品,这意味着这两款架构不再提供对32位应用的支持,也不再支持任何32位代码。唯一出现例外的是Cortex-A710,ARM明确指出,Cortex-A710依旧兼容AArch32,这样做的原因是考虑到中国市场依旧存在很多32位应用程序。不过这样就存在一些问题,假如某个SoC使用了Cortex-X2、Cortex-A710搭配Cortex-A510,那么这些32位应用程序将一直运行在Cortex-A710核心上,不会唤醒能耗比更高的Cortex-A510或者性能更强的Cortex-X2,是否会带来实际使用中功耗或者性能的问题呢?或者会更快的推动整个市场向64位转型?这些问题值得进一步观察。

继续提高性能上限:Cortex-X2解读

先来看定位高性能的Cortex-X2。从设计理念上来看,Cortex-X2延续了Cortex-X1的原始设计理念,也就是不再严格关注功耗,允许更大的核心面积和更高的功耗来实现更高的性能。相对应的,ARM给出的示意图显示Cortex-X2相比新的Cortex-A710的绝对性能增加值要远高于上代Cortex-X1对比Cortex-A78。这意味着Cortex-X2有望达到更高的性能,更适合相对更大屏幕的设备比如笔记本电脑等。

从架构角度来看,Cortex-X2并不是Cortex-X1的简单改变,它几乎是一个全新设计的架构,这主要是由于Cortex-X2采用了全新的Armv9指令集并带来了大量的诸如安全、计算方面的新功能。此外,ARM宣称Cortex-X2仅支持AArch64模式,并且为AArch64进行了优化,即使是在用户控制的PL0模式之下也是如此。从微架构的角度来看,只支持AArch64意味着在架构设计上不需要考虑之前的兼容性问题,这能够在很大程度上节约部分用于兼容性的资源,同样的设计也出现在Cortex-A510中,这个内核也放弃了对32位老旧架构的支持。

继续来看Cortex-X2的架构部分。先来看Cortex-X2的前端设计。这个部分,ARM在分支预测方面进行了大幅度的改进。ARM的官方资料显示,他们在三个方面改进了整个分支预测部分,一是对分支预测和拾取部分进行了分离,这样做使得前端部分在分支预测错误的情况下能够更快速地运行,并且能够掩蔽分支气泡(branchbubbles),此外ARM还为L1加入硬件预拾取功能以及由私有L2支持的更大尺寸的L1等。二则是改进条件转移预测的准确性,ARM在这里使用了更大的预测状态存储和备用的路径预测方案。三则是提升大型指令在负载状态下的工作性能,这里ARM使用了更大、更高效率的BTB。总的来看,ARM在分支预测方面的改进,有效减少MPKI(每千指令预测失败数量,Missesperkiloinstructions),能够在更广泛的指令运行中起到更好的效果。

在执行部分,ARM特别提到了加强的乱序执行能力(OoO),ARM通过降低流水线级数、扩大OoO窗口尺寸、增强指令融合三个方面来提升处理器的指令执行能力。另外,由于来自Armv9的新SVE指令集的加入,Cortex-X2还带来了更强的矢量计算和机器学习计算能力。这些内容我们详细解释如下:

首先是在指令分派阶段,ARM目前已经将这个阶段的时钟周期从2个降低至1个,因此Cortex-X2的整个流水线长度总体上从上代内核的11级降低至现在的10级。需要注意的是,在这里需要将流水线周期和预测失败惩罚进行区分,后者已经在Cortex-A77上实现了大多数情况下降低至10个周期。一般来说,较短的流水线在频率提升上相对较长的流水线存在一定的困难,并且ARM在Cortex-X2上希望保持较高的频率提升潜力,因此这里降低流水线级数的设计可能会导致功耗或者芯片面积的负面影响。不过ARM提到,如果单纯考虑性能优势的话,较短的流水线可能整体表现会更为出色,值得尝试。

其次,Cortex-X2增加了乱序执行的指令窗口。Cortex-X2的ROB(指令重排缓冲区,Re-OrderBuffer)的大小从之前的224个增加值目前的288+个,提升了高达30%,而实际数据还要高一些。因为在压缩和指令捆绑的情况下,实际存储数量都是高于288个的,因此ARM在这里是用了一个“+”号来指代实际的指令存储能力。

第三則是指令融合,ARM宣称Cortex-X2增加了更多的指令融合内容,不过这里没有更多的细节描述。

第四则是有关全新的SEV2指令集带来的整个Cortex-X2后端的大幅度加强。后端的SIMD管道提供了对SEV2指令集的支持,不过宽度依旧是128bit,这个部分和Cortex-X1的后端设计存在一定的相似性。在这里需要解释的是,目前后端SEV2选择128bit是考虑到在大小核心搭配和切换时需要保持同样的指令宽度,否则可能会存在无缝迁移的问题。另外,ARM还提到在Cortex-X2上机器学习的性能提升了2倍,还实现了对bfloat16和int8格式的兼容。

ARM给出了解码、重命名、指令交付和执行部分的细节图。经过前端解码、重命名和分派后,将有8个Mops(宏指令,Macro-Operation)会被分派至执行单元部分。这部分由整数和浮点两个部分组成,其中整数部分包含了6个执行端口,分别是2个分支(Branch)单元、2个ALU单元、1个ALU和MUL复合单元以及1个可以执行ALU、MAC以及DIV的复杂单元组成。浮点执行部分则包含了4个执行端口,分别是2个可以执行FMUL/FADD/FDVI/ALU/IMAC的复杂单元以及2个可以执行FMUL/FADD/ALU的计算单元组成,整体计算资源还是非常丰富和充裕的。

最后再来看看后端部分。ARM在后端部分带来了3个改变。其一是后端的加载存储窗口/结构增加了大约33%,这有助于提高整个架构的内存级并行性(MLP)。一般来说,ARM在这里使用了几种结构来增强并行性,但是一般不会具体说明,只有通过实际产品的测试来一探究竟。其二则是ARM将L1的d-TLB(数据TLB)增加了20%,目前的大小为48个条目。其三则是提高了数据预取的性能,增加了额外的步幅覆盖、提高了时间预取覆盖范围和准确性、加强了Tablewalk预取的覆盖面积等。

在这里值得注意的是时间预期器,这是目前业内首个商业化使用的此类预取器,这种预取器能够锁定任意重复的内存模式,同时智能识别内存访问中的新的迭代,因此最终可以巧妙地将整个预取覆盖至一定的深度(据估算是32MB~64MB的窗口)。有关时间预取器的详细内容,后续只有接触到实际芯片才能有进一步的消息了。

最后,ARM给出了新架构的相关IPC改进的内容。ARM给出的数据显示,在ISO频率下,Cortex-X2配备64kBL1、1MBL2以及8MBL3,对比Cortex-X1配置64kBL1、1MBL2以及4MBL3,Cortex-X2的性能提升了16%,ML也就是机器学习性能提升了2倍。这个数据是在SEPCint2006估计中得到的。值得注意的是,这里Cortex-X2的L3缓存配置高达8MB,是Cortex-X1的2倍,因此这里16%的性能提升一定程度上来自于翻倍的L3缓存。

在这里,ARM再次重申Cortex-X2的设计是附带8MBL3缓存的方案,因此最终可以实现16%IPC的提升。但是在实际产品中的情况要更为复杂一些,比如之前的Cortex-X1也要求配备8MBL3缓存,最终实际产品比如骁龙888和Exynos2100都仅采用了4MB的设计,毕竟更大的缓存需要占据大量的晶体管数量也推高了核心面积,厂商还需要进一步谨慎地衡量L3和成本、功耗和效费比之间的关系。最终在Cortex-X2上,L3的容量究竟是多少还有待观察。

ARM还给出了有关Cortex-X2和Cortex-X1的频率和功耗曲线。从ARM给出的表格可以看出,Cortex-X2的确可以达到更高的性能,但是在性能需求较低的情况下它的功耗表现会略高于Cortex-X1,ARM没有给出具体的坐标轴数据,因此不知道这两个曲线的具体交叉点的细节情况。

在本节的最后,我们再来聊聊有关功耗和工艺的问题。考虑到具体产品的成本等因素,高通和三星往往会选择比较便宜但效能较低的工艺,比如三星的5nmLPE,因此最终实际产品的效能表现可能达不到ARM的官方数据。在Cortex-X2上,考虑到三星和高通在市场竞争方面压力并不大,因此有可能继续维持现在的路线,比如说采用三星进行代工制造,从而耗费较低的成本并获取更多利润,因此估计下一代SoC即使使用Cortex-X2,其性能表现也应该很难达到16%IPC提升的要求,因此大家对新一代移动SoC的预期需要更为保守一些。

平衡功耗和性能的产品:Cortex-A710

Cortex-A710是ARM推出的综合平衡了功耗、面积和性能三个因素的产品,相比几乎不惜工本、追求更高性能的Cortex-X2,Cortex-A710更适合绝大部分用户选择。

虽然整个产品名称变化,但是Cortex-A710实际上是Cortex-A78的后续增强版本。它增加了大量Armv9指令集的功能,提供了类似于上一代Cortex-A78的配置选项,并且在微架构上为性能、功耗和面积做了特殊的优化。另外,正如前文所说,在指令集方面,Cortex-A710支持在EL0模式下运行AArch32应用程序,这是其他两款新架构都无法实现的。

从架构角度来看,Cortex-A710的部分增强和之前的Cortex-X2基本相同。比如前端方面,Cortex-A710在分支預测方面的改进和Cortex-X2类似,都带来了更高的分支预测精度、关键的分支预测结构容量翻倍,比如BTB分支目标缓冲区、GHB全局历史缓冲区都拥有更高的容量。L1TLB的容量也增加了50%,从之前的32条目增强至目前的48条目。其他的部分包括Mops缓存依旧是1.5K条目保持不变,但是远远小于Cortex-X2的3K条目容量。

在中核阶段,这里Cortex-A710有一个非常有趣的变化,就是相比Cortex-A78的6宽度,新的Cortex-A710采用了5宽度设计,ARM解释说这种改动是为了提高效率。另外和Cortex-X2相同的是,Cortex-A710目前也减少了指令拾取的周期数,目前只有1个周期,因此整体管道长度也降低至10级。此外,ARM还对重命名阶段进行了重新优化,减轻了性能瓶颈,另外还提升了拾取宏指令的性能。

此外,Cortex-A710的指令预取部分也实现了增强。具体的改变和在Cortex-X2上的类似,都是提高了准确性和覆盖率。另外,Cortex-A710还降低了搭配DSU的时候内核到L3的访问时间,并且更好的预取器和更大的L3还降低了低效的DRAM访问次数,提高了效率。

最后再来看看IPC方面的提升,ARM宣称Cortex-A710相比Cortex-A78提升了10%的IPC,但这里依旧是基于8MBL3对比4MBL3而来。因此具体到实际产品上的话,由于Cortex-A710适用范围更广泛,不但可以使用在高端处理器上,也可以使用在中端产品中,最终如何配置还取决于厂商对产品的市场定位,因此实际产品可能很难获得10%的IPC提升,除非它完全按照ARM的DSU尺寸进行配置。

另外有一个非常有趣的内容,那就是相比之前的Cortex-A78,Cortex-A710在频率稍微降低的时候,Cortex-A710能够实现比Cortex-A78更低的功耗,ARM的数据是这个数值最高可达30%,这意味着Cortex-A710有望在最佳工作区间实现极高的能耗比,当然这需要厂商精确的设计和控制才能实现。

总的来说,Cortex-A710实际上给出了近几年最低的架构代际性能提升。ARM的解释是由于迁移到Armv9带来了架构巨大的变化,因此对效率和性能的改进产生了影响。目前Cortex-A710和Cortex-X2都是来自ARM的奥斯汀团队,这已经是奥斯汀微体系架构的第四代产品了,因此遇到收益递减的边际效应也是可以理解的。实际上,ARM的另一个团队索菲亚团队一直在潜心研究新的架构,可能明年就会由索菲亚团队带来效能和性能飞跃的全新架构了,非常值得期待。

全面革新的小核心:Cortex-A510

Cortex-A510是ARM使用Armv9指令集推出的全新高性能功耗比小核心。ARM首先介绍了Cortex-A510的设计思路。宏观来看,Cortex-A510依旧是一个三发射的、顺序执行的CPU微架构,不过他加入了一些来自Cortex-X架构的技术来提高整体性能,比如分支预测和数据预取等。Cortex-A510另一个重要变化是全新的“mergedcore”微架构,也就是“合并核心”微架构,这会大大提升芯片区域的效能。最后,Cortex-A510是基于Armv9指令集的产物,不再支持AArch32的应用程序。

在这里需要说明的是,虽然目前工艺制程越来越先进,单位面积可以容纳的晶体管数量也越来越多,ARM是有条件或者有可能在此类目标为高性能功耗比场合的微架构上使用乱序执行架构的,但是ARM还是采用了顺序执行架构并提到这依旧是目前最高效率的设计方式,有关这一点业内还存在较多争议,本文也会就此在后文进行一些讨论。

首先还是来看颇为吸引眼球的“合并核心”微架构的设计。在这里ARM对其进行了比较详细的解释。根据ARM的描述,所谓合并核心实际上是指2个核心可以看作一个“复合体”,这个复合体内部的NENO、SVE2SIMD部分以及L2TLB、L2缓存都是可以共享的。ARM宣称这样设计可以提高芯片区域效率,并且带来可伸缩、广泛的配置方案以满足不同的需求,此外,这种设计还可以让一个复合体内部的一个核心占用所有的资源以提高单核心性能。

有关这种复合体的设计,与之比较相似的是AMD在之前的推土机微架构上使用的CMT架构,不过AMD的CMT模块本质上是一种介于两个独立的CPU核心和一个拥有超线程的独立CPU核心之间的设计,这种设计中,一个CMT模块包含2个X86整数单元,因此被认为是2个核心,每个整数运算调度单元各自拥有16KB的L1缓存,但是整个CMT又共有可以拆分为2个128bit的浮点SIMD单元(或者可以合并为1个256bit的SIMD单元),同时共享前端的指令解码、拾取、二级缓存和IO总线等部分。

Cortex-A510有两个完整的内核,各自拥有独立的前端、中核和整数后端单元以及L1缓存结构,“共享”的部分实际上是浮点SIMD(SVE2)单元和L2缓存部分。其中浮点单元可以配置为2x64bit或者2x128bit。L2缓存可以配置为不存在或最大512KB。

从比较微观的角度来看,ARM设计所谓“合并核心”的初衷是考虑到对Cortex-A510这种小核心来说,更常用的资源是整数执行部分,对浮点执行部分启用的机会较低,因此干脆两个核心共享一个浮点和L2部分,这样可以带来单位面积效能的提升,因此这样来看这种设计是有意义的。但是,从实际应用的角度来看,如果一组合并核心内的浮点单元被一个核心所占用,那么另一个核心则无法完成同样的工作,因此可能会被闲置,在这种情况下,合并核心中的共享资源实质上相当于被某个核心独占了,这又意味着单位面积效能的降低。

对于这种矛盾的情况,目前ARM没有给出太多解释。实际上,最终的效能表現在很大程度上应该取决于软件、系统如何使用这种合并核心或者如何调度资源,希望在实际产品上市前我们能得到更多的信息。

继续来看架构,Cortex-A510前端采用了128bit的拾取管道,每周期最多可以获取4个指令,可以应对分支气泡的情况。解码器宽度从之前Cortex-A55的2宽度提升至3宽度,这意味着它每周期能够提供3个指令解码。随后的分支预测方面,ARM宣称Cortex-A510使用了最先进的多级分支预测技术,ARM在这里没有透露太多细节。L1指令缓存可能是32KB或者64KB,这一点还有待ARM确认。

在执行端的矢量单元部分,ARM宣称矢量单元也就是浮点计算部分的共享设计对硬件来说是完全透明的,并且还提供细粒度的硬件调度机制。在同时使用了2个内核的实际多线程工作负载中,其性能影响相比传统的拥有专用管道的内核,实际性能损失应该据说只有几个百分点—这应该是ARM采用类似合并核心设计的论点来源,既然损失如此之小,那完全可以砍掉一整个浮点单元模块以节约面积。

另外,Cortex-A510在浮点单元部分可选2x64bit或者2x128bit的设计也带来了一定的自由性,如果厂商考虑性能则会考虑选择2x128bit的方案,这样一次可以执行2个128bit的SIMD指令,如果选择2x64bit的话,那么可以使用合并执行的方式一次执行1个128bit的SIMD指令,但无论如何,Cortex-A510所能执行的浮点指令最大位宽都是128bit。当厂商选择2x128bit方案时,其峰值性能将达到前代Cortex-A55的2倍。在这里,厂商又将在性能、功耗和面积上做出谨慎的平衡,是交由Cortex-A510的浮点单元执行还是挪去更高端的Cortex-A710,值得很好的研究。

继续来看后端,虽然Cortex-A510是一个顺序执行单元,但是ARM还是对其后端执行部分进行了扩充。目前,Cortex-A510的后端执行部分包含了3个ALU单元、1个分支单元和1个复杂的MAC/DIV单元。扩充的单元规模有助于在指令进入时快速地将其处理完成,降低指令执行周期数并提高性能。在这里,后端单元规模的扩充是和前端解码能力的扩充相适应的。

接下来的加载和存储系统是Cortex-A510的亮点之一。相比Cortex-A55,Cortex-A510的加载和存储部分得到了大幅度改进,Cortex-A510目前拥有1个加载单元和1个同时可以执行加载和存储的单元,相比上代产品仅有1个加载单元和1个存储单元而言,新的设计将加载和存储的峰值都提高了1倍,并且加载和存储单元的宽度从之前的64bit提升至128bit,再度翻倍。因此相比Cortex-A55,Cortex-A510在加载和存储部分的峰值效能实际上达到了前者的4倍。ARM给出的数据显示,Cortex-A510相比Cortex-A55,在L1、L2、L3的缓存带宽方面分别达到了后者的4倍、2倍和2倍,性能提升明显。

性能增幅方面,ARM也照例提供了官方数据。ARM在这里使用了拥有32KBL1、256KBL2和8MBL3的Cortex-A510对比拥有32KBL1、128KBL2和4MBL3的Cortex-A55,在两者频率相同的情况下,SEPCint2006中Cortex-A510拥有35%的性能优势,SPECfp2006中拥有50%的性能优势,LMbench中拥有62%的性能优势。总体来说,单纯对比Cortex-A510相比Cortex-A55的增长幅度是非常令人满意的,不过考虑到Cortex-A55发布于2017年,那么这样的增长幅度又让人觉得不那么惊艳了。

最后来看Cortex-A510对比Cortex-A55的性能和功耗曲线。从这个曲线可以看出,实际上Cortex-A510在很大幅度上和Cortex-A55完全重合,只有在Cortex-A55高频部分才展示出了明显的性能、功耗提升。比如ARM给出的数据是在Cortex-A55的极限频率处,Cortex-A510在同性能下可以降低20%的功耗,或者同功耗下提升10%的性能。

这里我们进一步讨论一下顺序执行核心和乱序执行核心的问题。实际上从Cortex-A510的性能来看,顺序执行架构似乎已经达到了它的极限点,对其架构的改进很难带来非常明显的性能提升。从ARM给出的曲线图也可以看出,Cortex-A510后期的性能提升基本上是和频率和功耗的增长挂钩,而不是架构本身,这说明Cortex-A510和Cortex-A55这样的架构设计已经基本没有太多潜力可挖了。

相反,对小核心设计而言,苹果给出了一个比较好的例证。根据anandtech的测试,苹果的高性能功耗比核心的性能比Cortex-A55高了大约4倍,因此即使是Cortex-A510登场,也基本上无法改变这种态势。其中的差别在于,苹果的高性能功耗比核心也就是小核心采用的是乱序执行架构。对于这一点,ARM依旧坚持在高性能功耗比核心上使用顺序执行架构,ARM设想一些非常轻量化的工作负载比如UI等运行在小核心上能够最大限度地带来能效的提升,并且还可以搭配其他核心进行操作。

目前对在高性能功耗比核心上采用何种架构依旧存在争论。不过仅从Cortex-A510的性能表现来看,ARM再次提高了小核心的性能上限,这使得更多的计算任务可以驻留在Cortex-A510这样拥有极高性能功耗比的小核心上,在完成任务的同时还消耗更少的能源,起到节约电能、延长续航的作用。

推开Armv9时代的大门

从ARMCortex-X2、Cortex-A710和Cortex-A510的架构和设计情况来看,ARM在发布了全新指令集之后,就迅速推出了面向消费者的全新架构,这显示了ARM强悍的研发能力和出色的执行力。具体到架构来看的话,Cortex-X2持续提高ARM处理器的性能巅峰,Cortex-A710带来了更好的性能和功耗平衡,Cortex-A510则进一步在保持较低功耗的情况下提升了性能上限,三个核心都很好地完成设定的目标,也为我们推开了Armv9时代的大门。接下来,这三款架构可能会在2021年底发布的全新一代处理器上现身,比如高通骁龙和三星Exynos,或者联发科的相关产品,届时本刊会再针对具体产品进行详细解读。