基于FPGA并行+拆分查找表分布式高阶FIR的设计与实现

2021-07-05柴乾隆

柴乾隆

(航空工业兰州万里航空机电有限责任公司 航空机电研究院,甘肃 兰州 730070)

滤波器主要用于频率选择和运算处理,以起到滤除噪声和分离信号的作用。根据滤波器系统输入、输出信号的处理方式,可分为模拟滤波器和数字滤波器两种。模拟滤波器在设计时可通过查询大量图表予以实现,简捷明了,但因相位的非线性,其应用受到了很大的限制。而数字滤波器因其相位线性度高,幅度特性[1-3]任意可变,而被广泛应用于语音和图像处理、HDTV、模式识别、谱分析等领域。单位抽样响应的长度直接影响着有限长单位冲激响应(Finite Impulse Response,FIR)数字滤波器的稳定性,当抽样响应的长度有限时,系统的极点均在原点处,因此FIR滤波器是一个稳定的线性系统。同时,快速傅里叶变换(Fast Fourier Transfor,FFT)能够在很大程度上提高FIR滤波器的运算速率[4],以有助于FIR滤波器对信号的有效过滤。

大多数传统的FIR滤波器都是采用TI公司的TMS320CXX系列数字信号处理器(DSP)芯片[5]来实现系统设计。根据输入序列的乘累加[6]编写软件,以硬件为平台,结合软件算法,实现滤波器的设计。但DSP芯片的冯·诺依曼体系架构使得数据的处理速度和容量都受到了限制,而FPGA因其丰富的连线资源和庞大的逻辑阵列,为实现并行度极高的FIR滤波器搭建了高效的运作平台,同时具有优良的可扩展性。通过采用分布式算法,FIR滤波器可以克服滤波器阶数对运算速率的影响,使两者不呈正相关性。因此,分布式算法可广泛应用于高阶FIR滤波器的设计。

传统分布式算法大多数采用串行处理输入序列的数据,获取输出序列值。采用传统分布式算法易于实现低阶滤波器,而高阶滤波器的实现则较为困难。目前,利用分布式算法实现的高阶FIR滤波器,大多数都采用串行分布式结构、并行分布式结构或拆分查找表结构。3种分布式结构在存储器占用和时钟周期利用方面都各有优缺点,因此对3种结构的算法进行整合,可有效提高存储占用和时钟周期利用,有效化解了两者之间的矛盾。

本文以国产FPGA为硬件平台,综合利用各算法的优势,提出了一种基于FPGA并行+拆分查找表分布式结构高阶FIR的设计与实现,以中国电科58所的JS1032系列FPGA为核心器件,利用100%国产化元器件搭建硬件电路,比较研究了3种分布式算法,对FIR滤波器进行了硬件实现和软件仿真,同时利用惠普网络分析仪对所设计的FIR滤波器进行了幅频特性的测试,验证了该算法的有效性和实时性。

1 FIR滤波器传统算法及其改进

1.1 FIR滤波器概念与方法介绍

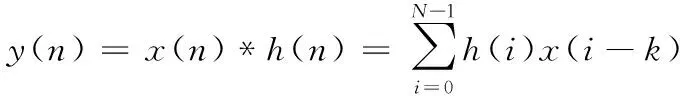

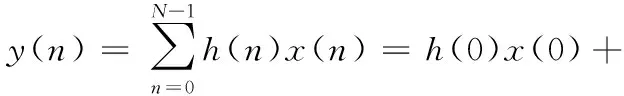

线性时不变性[7]是FIR滤波器最大的系统特征,N阶FIR数字滤波器的输入序列x(n)与单位冲激响应h(n)经卷积运算可得输出序列y(n):

(1)

FIR滤波器典型的设计结构主要由延时单元、乘法器、抽头系数、加法器等部分组成,FIR滤波器典型的设计结构如图1所示。输入样本x(n)通过缓冲区实现Z-1延时,并在数据寄存器中,开设n个用于存放最新输入样本的滑窗。最新的数据采样乘以抽头系数,得到的乘积再与上一次的加法器结果进行求和,依次递进运算,改变抽头数目和抽头系数可获得不同幅频特性的FIR滤波器。

图1 FIR滤波器典型的设计结构

庞大的乘法和加法运算非常消耗FPGA的资源,同时FPGA的设计效率和逻辑单元的占用量都非常高,因而使用传统方法实现FIR滤波器,滤波器的阶数很难提高,因此必须对经典实现方法进行优化改进。

1.2 分布式算法

分布式算法[8]是Croisier于1973年提出的,但由于计算资源的客观限制,发展较为缓慢,直到FPGA的出现,才使得分布式算法得到了广泛应用。

分布式算法通过将n个数据的相同序号的位在移位寄存器中进行操作,在查找表中获取相应的部分积,然后通过二次幂加权对已获取的部分积进行累加,完成加法运算后,获得最终结果。而传统经典算法的乘法运算和加法运算是分离的,是在完成所有乘积之后,再对乘积结果进行累加。分布式算法与传统算法相比,实现滤波器设计的硬件电路规模大为减小,并以流水线式的处理模式,使得计算速度大幅提高。FPGA因其能高速完成移位和加法运算使得分布式算法的应用更为广泛[9],也拓宽了FPGA芯片的应用领域。为了便于分析,将滤波器输出序列的表达式改为

(2)

假设h(n)均为常数,x(n)是变量,无符号数x(n)的表达式为

(3)

式中,n为第n个采样值;b为x(n)的第b位。则y(n)可以表示为

(4)

变换求和次序,重新求和得:

y(n)=h(0)[xB-1(0)×2B-1+xB-2(0)×2B-2+

x0(0)×20]+h(1)[xB-1(1)×2B-1+xB-2(1)×2B-2+

x0(1)×20]+…+h(N-1)[xB-1(N-1)×2B-1+

xB-2(N-1)×2B-2+x0(N-1)×20]

=h(0)xB-1(0)+h(1)xB-1(1)+…+

h(N-1)xB-1(N-1)]2B-1+…+[h(0)x0(0)+

h(1)x0(1)+…+h(N-1)x0(N-1)]20

(5)

化简成如下形式:

(6)

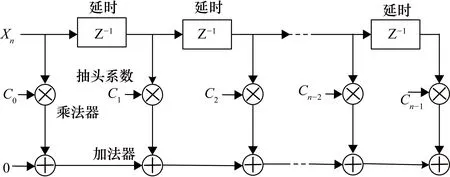

式中,xb(n)为第n个数据的第b位。x(n)为取值[0,1]的有限位数据。分布式算法的原理框图如图2所示。

图2 分布式算法原理框图

求得滤波器系数后,根据滤波器输入数据位宽,对系数进行合适的放大,在实现过程中对累加值进行右移,得到系统的输出结果。

1.3 并行+拆分查找表分布式结构

分布式算法以序列运算处理的方式划分,可分为串行分布式结构、并行分布式结构和拆分查找表结构。

串行分布式结构需要大量的ROM进行寻址,同时一次运算需要多个时钟周期,使得成本和存储时间都急剧增加。当FIR滤波器的阶数很高时,使用串行分布式结构很难实现。例如,设计一个阶数为64、位宽12的FIR滤波器,需要12×264bit的存储空间,而FPGA根本没法提供高达12 Gbit的内部存储空间。

拆分查找表结构相较串行分布式结构而言,很大程度上减小了存储器的数量,但拆分查找表结构和串行分布式结构同样需要很多个时钟周期来实现乘加运算。输入数据的位宽决定了串行分布式结构和拆分查找表结构两种算法实现FIR滤波器输出速率的快慢,每输入一个数据,输出一定要延迟相应位宽个数的周期,才能输出一个数据,极大地影响了数据处理速度。

并行分布式结构在同一周期内同时寻址已存入ROM表的输入数据,占用的存储器资源也较多,但与串行分布式结构相比较,其占用的存储器资源个数少之又少,同时在处理高速信号时,并行分布式结构以其较高的数据吞吐率显现出很大的优势。

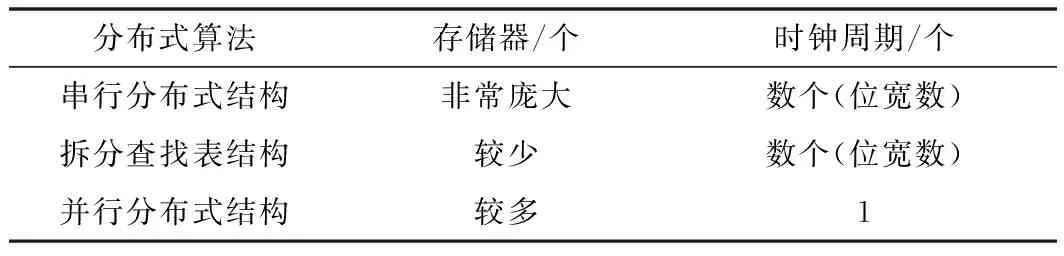

根据以上对3种分布式算法优缺点的分析说明,串行分布式结构、拆分查找表结构和并行分布式结构在占用存储器资源和时钟周期方面的对比如表1所示。

表1 3种分布式算法的对比

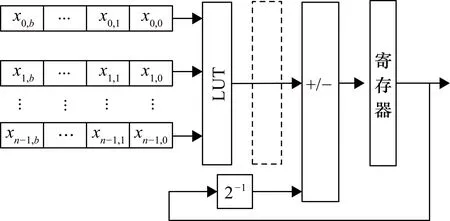

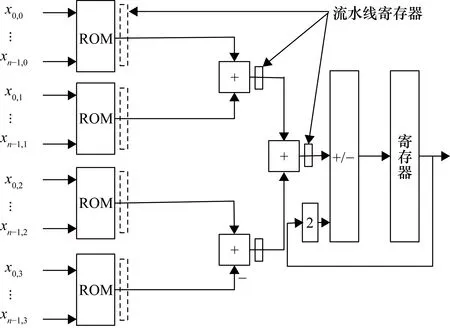

为了克服3种分布式结构在存储器占用和时钟周期利用方面的矛盾,对并行结构和拆分查找表结构进行了整合,使得输入数据在同一周期同时进行取值,提高运算速率,并将查找表拆分成若干个小的查找表,减小存储器的占用,提出并行+拆分查找表结构的分布式算法。并行+拆分查找表分布式结构如图3所示。下面举例说明并行+拆分查找表结构的分布式算法在计算规模和时钟周期数两个方面的优势。例如本文256阶的FIR滤波器使用传统模式查找表,位宽达2256,通过拆分查找表,其规模可降为16×216=1048576,并在一周期内对输入数据同时进行寻址,一方面提升了系统的运算效率,另一方面减小了系统的设计规模。

图3 并行+拆分查找表分布式结构

2 并行+拆分查找表分布式算法的实现

2.1 硬件设计

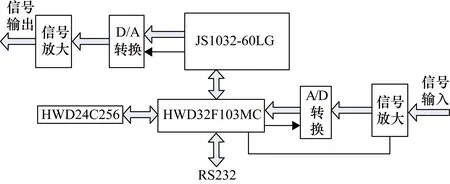

FIR滤波器的实现需建立在一定的硬件平台基础上,其硬件电路系统框图如图4所示。在本文的硬件电路中,时序信号和控制信号是由FPGA来完成,同时FPGA处理FIR滤波器系统的输入数据,是实现系统要求的核心器件。FPGA的配置是通过STM32来完成的。每次系统通电后,STM32将事先存入到只读存储器HWD24C256中的配置文件下载到FPGA 中,下载完毕后,FPGA便开始工作。若需要修改滤波器的参数,只需存入不同的配置文件,而无须改动硬件电路,增强了硬件电路的通用性。采用STM32芯片自身的A/D口,其转化精度为12位,分辨率高,转换速率最大可达1 MHz。

图4 硬件电路系统框图

信号输入后,根据信号幅度的控制要求,对信号进行适应性放大,并传输给A/D转换器进行采样转换,之后送到FPGA进行运算处理;FPGA完成对数据的处理之后,将结果进行D/A变换,转换成模拟信号后,再经过运放调整,最后输出系统信号。

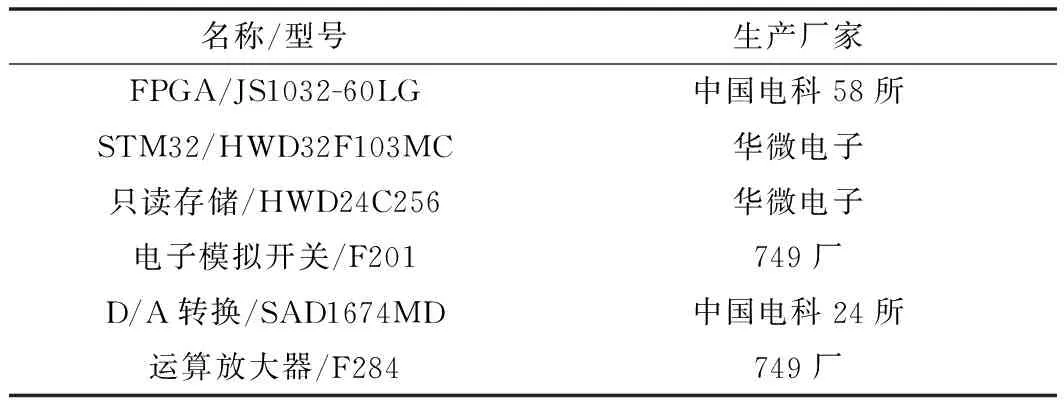

因美国对华大规模的芯片禁购,很多进口原器件已无法使用。本系统所选器件均为国产,元器件国产化数量比、规格比、费用比均为100%,系统主要元器件如表2所示。

表2 主要元器件表

2.2 FPGA程序架构

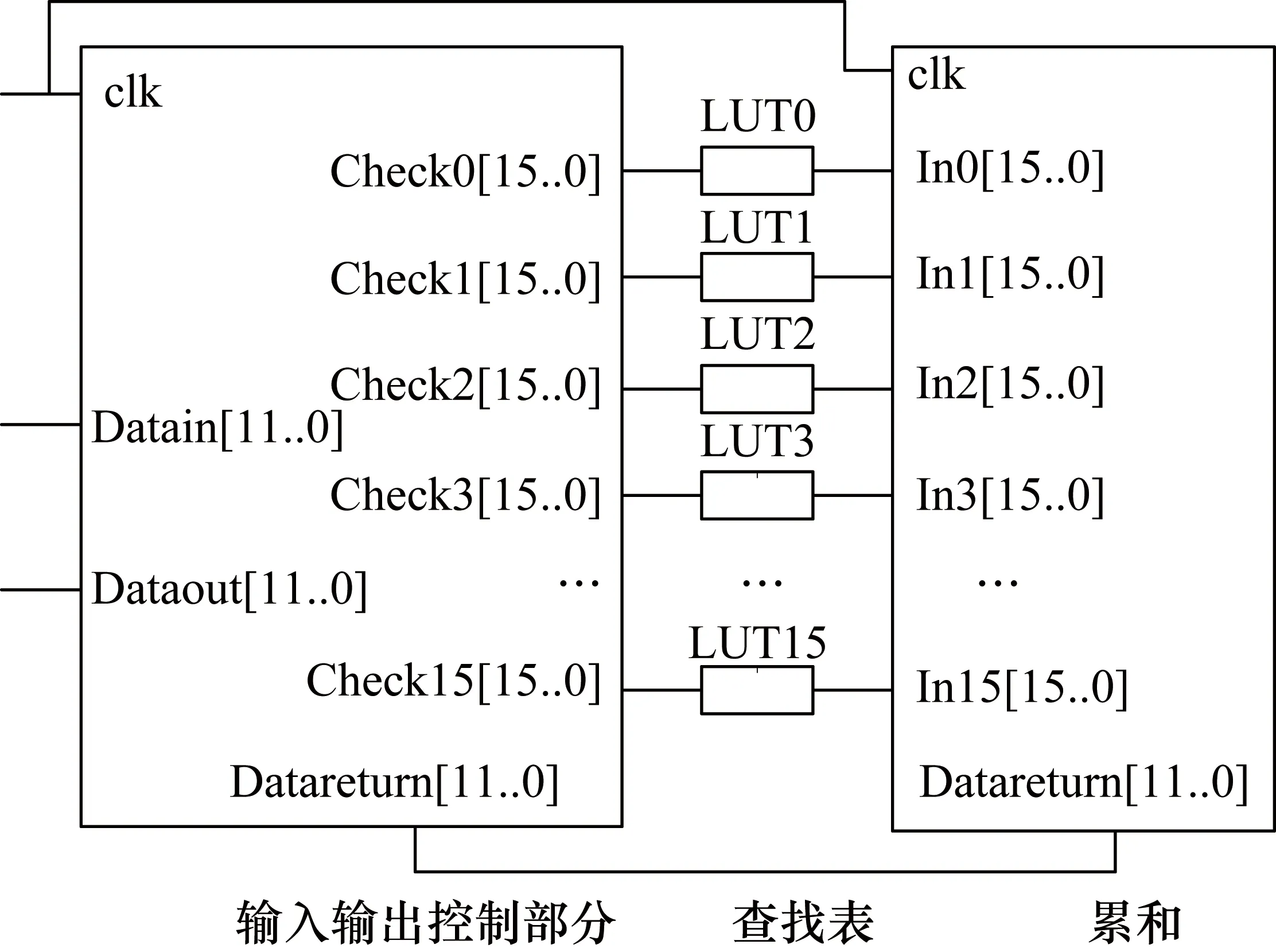

并行+拆分查找表分布式算法在FPGA上的实现基本可以划分为三大功能模块:输入输出控制部分、查找表(Look-Up-Table)部分和累和部分。FPGA程序的系统架构如图5所示。

图5 FPGA程序的系统架构

其中,输入输出控制部分负责完成系统数据的采集并将滤波运算处理的数据输出给后级数模转换电路;查找表(Look-Up-Table)部分用于获取计算输出序列过程中的部分积;累和部分是对通过查找表所得的部分积进行加法运算。完成以上三部分的内容后,即可进行后续电路的处理,最终得到系统的输出信号。

2.3 确定滤波器系数

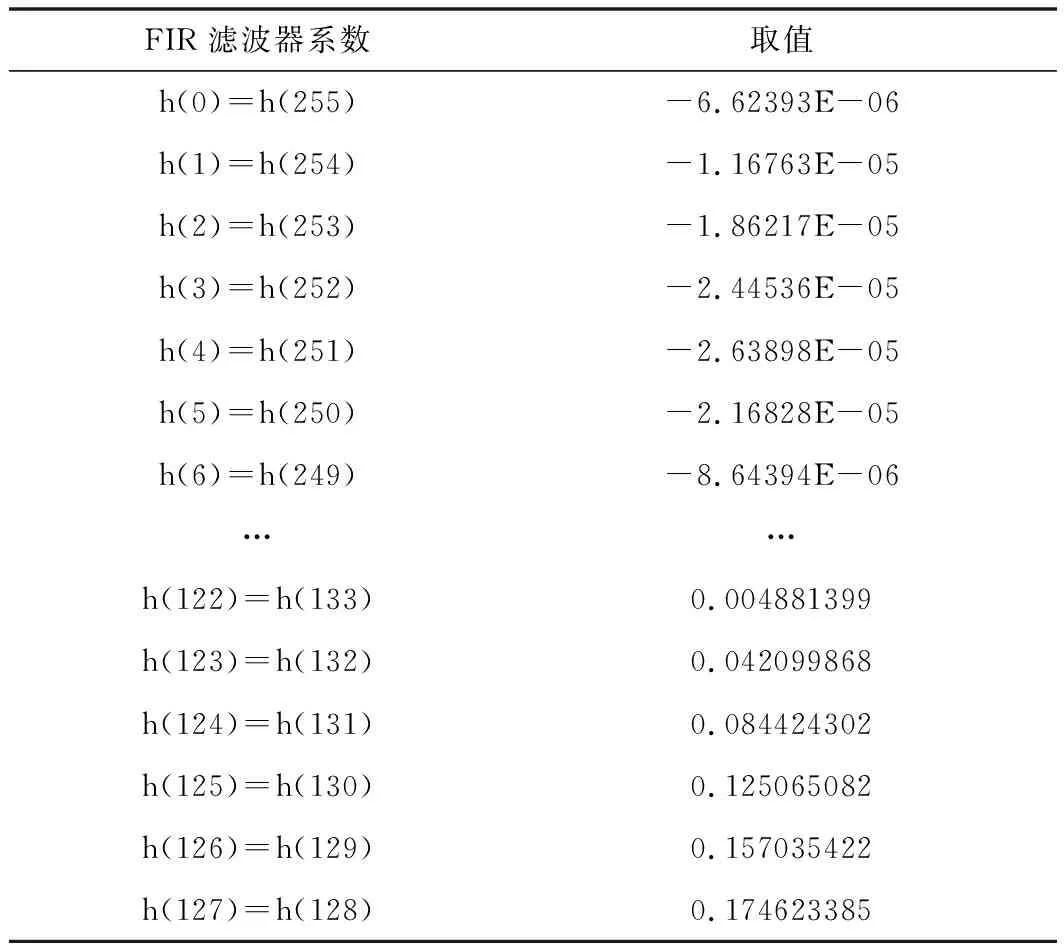

利用Matlab软件中的可视化仿真工具Simulink可以求得FIR滤波器的抽头系数[10],本文FIR滤波器所需系数如表3所示。因FPGA只能处理定点数的乘法,而Matlab生成的系数是分布在[-1,1]区间的浮点数,因此需要将所得的滤波器系数同乘以1024,才能在FPGA中参与运算处理。

表3 FIR滤波器系数

2.4 输入与输出

输入输出控制部分主要用于模拟信号的采集,完成运算处理后,输出处理信号用于后级进行D/A转换。另一方面,系统所需的时序信号也是由输入输出控制部分来实现的,通过时序控制输入数据,依次存入数据缓存区,以待进行查表。

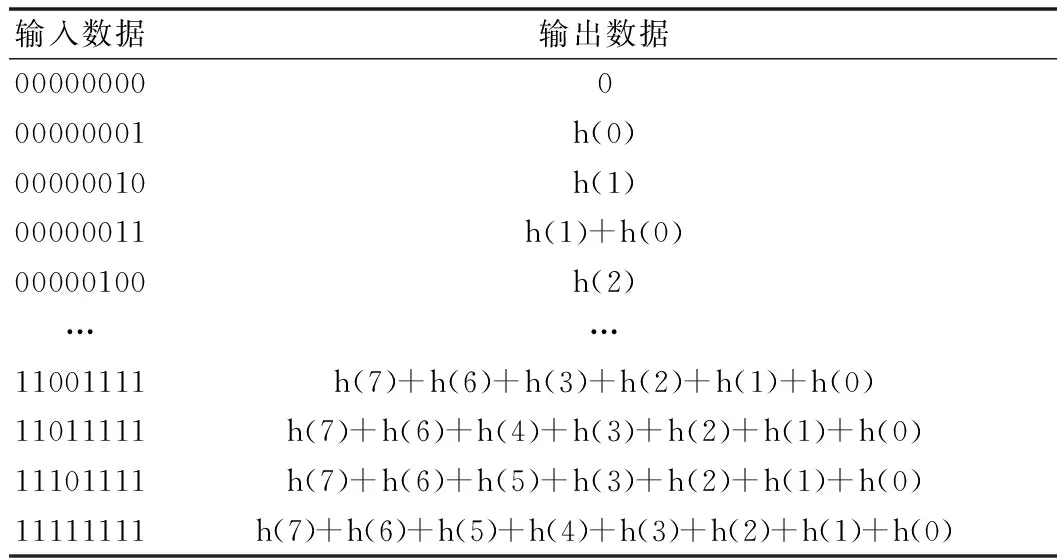

2.5 查找表(Look-Up-Table)

查找表部分主要用于对处理后的输入数据通过查表快速获得部分积结果。其中一个查找表的具体内容如表4所示,其他查找表可根据表4同理推出。

2.6 累和

累和部分对通过查找表获得的部分积进行相加,相加时一定要根据式(6)进行二次幂加权,才能得到系统的内积结果y(n)。获取内积y(n)后,就可以输出到后级电路进行D/A转换,进一步获取系统输出信号。

表4 查找表

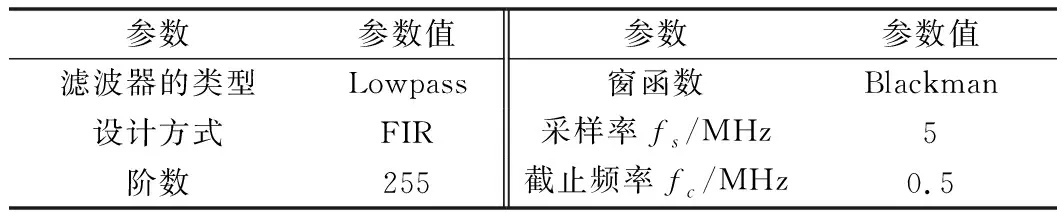

3 FIR滤波器的理论仿真

FDATOOL[11](Filter Design & Analysis Tool)是Matlab软件的Simulink中各种滤波器的专用设计与分析工具。FDATOOL可以设计实现各种常规滤波器,并可将各种算法体现在设计过程中。FDATOOL操作简单,方便灵活。在使用FDATOOL工具设计FIR滤波器时,滤波器类型、阶数、截止频率、窗函数的选择是其关键所在。其中,窗函数可根据设计需求实现对信号的截断,减少系统能量的泄露,其中Hamming窗、Blackman窗和Hanning窗最为常见。本文FIR滤波器在FDATOOL中的设计参数如表5所示。

表5 参数表

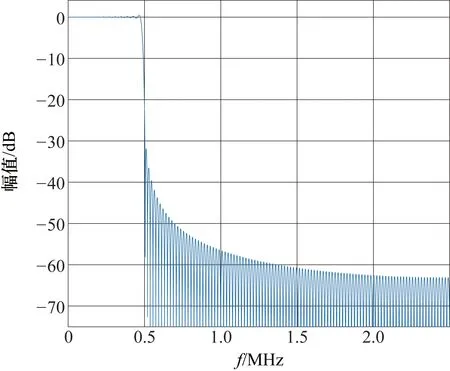

本设计中FIR滤波器的输入数据为12位有符号二进制数,在Matlab中利用Blackman窗计算FIR滤波器的滤波系数,设置采样率和截止频率分别为5 MHz和0.5 MHz。根据既定参数要求,通过Matlab的理论仿真,实现所需的高阶FIR滤波器,其幅频特性如图6所示。

图6 幅频特性(Matlab)

4 实测结果

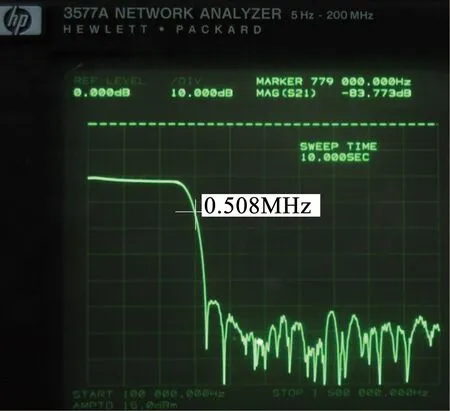

采用中国电科58所JS1032系列FPGA器件,在QuartusⅡ开发软件下完成并行+拆分查找表分布式FIR滤波器的仿真,其过程包括软件编程、程序的编译、调试,并利用网络分析仪HP3577A对FIR滤波器进行幅频特性的测试。网络分析仪测试所得的幅频特性如图7所示,可知高阶FIR滤波器的截止频率为0.508 MHz,与原定的设计要求0.5 MHz相比,误差很小。通过比较Matlab理论仿真与硬件电路实现的结果可知,利用硬件所设计的高阶FIR滤波器的幅频响应与Matlab理论仿真的结果高度吻合,误差仅为0.008 MHz。

图7 幅频特性(网络分析仪)

5 结束语

由于FIR滤波器传统实现方法存在局限性,通过对3种分布式算法进行比较,提出了一种基于FPGA并行+拆分查找表分布式结构高阶FIR滤波器的实现方法,并且利用中国电科58所JS1032系列FPGA及其他所选国产元器件设计实现了高阶FIR滤波器的硬件电路。通过软件Matlab仿真和硬件实测,表明基于FPGA并行+拆分查找表分布式结构实现的高阶FIR滤波器误差极小,运算速率快,硬件资源占用少,并可根据实际情况调整FIR滤波器的阶数,可使其广泛应用于很多领域。