功率DMOS器件加固技术的工艺设计

2021-06-16郑莹王浩

郑莹 王浩

(沈阳理工大学 辽宁省沈阳市 110159)

1 引言

随着空间技术、核技术等的快速发展,越来越多的功率器件DMOS 不可避免要受到各种辐射的作用,导致器件的电性能参数变化,主要表现为阈值电压漂移等[1],严重时会使得器件功能失效,从而影响整个半导体电子设备的正常运作,因此,有必要对功率器件的抗辐射加固技术进行研究。按照器件损伤机理,抗辐射效应通常分为抗总剂量和抗单粒子两种[2],目前报道的加固措施主要有Si3N4/SiO2 叠层栅结构[3]或者多晶硅部分剥离技术[4]等。本文在常规器件结构参数的基础上,引入厚氧结构,同时在工艺上采用后栅氧工艺,加大高能粒子入射器件难度且避免了高温过程,大大提高器件抗辐射的能力。在新的器件结构参数基础上,利用半导体仿真软件进行工艺模拟,得到最终的工艺设计流程。

2 器件原理与结构

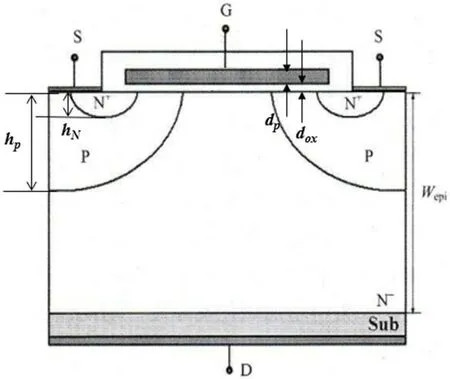

图1 是常规功率DMOS 器件的单胞结构与原理图, S、G 和D分别为功率DMOS 器件的源、栅、漏三个电极,外延层采用N 型Si 材料,外延层的厚度为Wepi,在外延层N-中形成了两个彼此对称的P 区和N+区,结深分别为hp和hN,为了避免寄生三极管导通,源极S 将N+区和P 区短接。在外延层上方分别是栅氧和多晶硅电极,在纵向构成MOS 结构,栅氧厚度为dox,多晶硅厚度为dp,经重掺杂后的多晶硅形成栅极G。当栅源电压VGS达到阈值电压Vth时,p 区表面形成强反型,形成导电沟道,在正的漏源电压VDS的作用下形成电流ID,经源电极、N+区、沟道和外延层垂直流向衬底漏电极;当栅源电压VGS小于阈值电压Vth时,无法形成导电通路,此时,P 区与外延层形成的PN 结反偏,耗尽层主要在外延层一侧,可以维持较高的阻断电压[5]。在常规器件结构基础上,在两个P 区之间上方多晶硅下方的氧化层厚度增加,就形成了新的功率DMOS器件结构,如图2 所示,tOx是厚氧化层的厚度。根据器件的电性能参数的要求:BVdss≥500V,Vth:2-4V,前期设计后得到的厚氧化层tox=400nm。同时,在工艺实现上还将采用后栅氧工艺,即在P区和N+区形成后再生长栅氧化层,这样可以有效避免高温过程对界面态等的损坏,进一步提高器件的抗辐射能力。

图1:常规DMOS 器件结构与原理示意图

图2:抗辐射功率DMOS 器件结构示意图

3 工艺设计

依据现有的工艺线加工水平,利用半导体工艺仿真软件对功率DMOS 器件加工单步工艺进行了模拟仿真,结合抗辐射功率DMOS器件的结构设计要求,分别对厚氧结构和后栅氧工艺进行的研究。

3.1 厚氧工艺

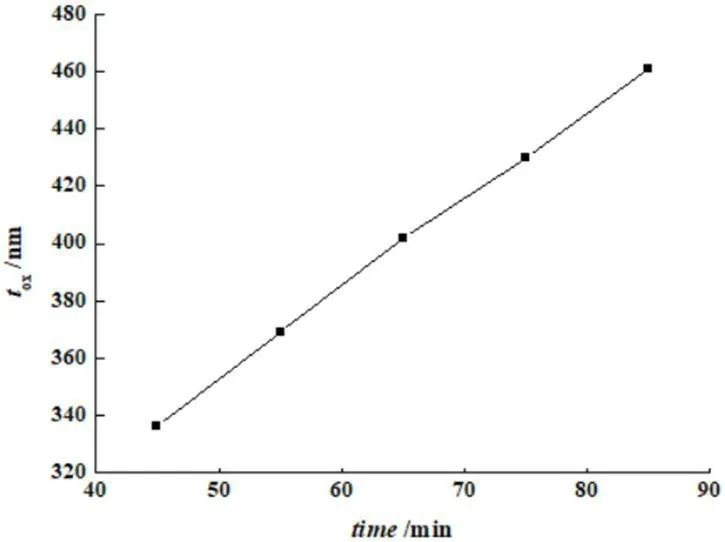

通过对整个工艺流程的分析,厚氧结构的形成主要通过场氧来实现,而厚氧化层的厚度由场氧的生长条件和栅氧厚度来决定,由于栅氧在场氧后面生成,此时在形成厚氧的位置,已经形成了一定厚度的氧化层,隔绝了硅外延层与环境气氛的接触,因此在生长栅氧的过程中,无论是干氧氧化、湿氧氧化或者干湿结合,厚氧化层的厚度将增长缓慢,也就是说,厚氧的最终厚度并不是场氧厚度和栅氧厚度的几何相加。通过调节场氧的生长时间和温度,可以得到不同的厚氧化层厚度,如图3 所示,可以看出,在生长温度T=1000℃时,场氧生长时间越长,厚氧化层越厚;在生长时间(65min)一定时,场氧生长温度越高,厚氧化层越厚,结果表明,在场氧的生长时间为65min,生长温度T 为1000℃时,测得厚氧化层的厚度为399nm,与结构设计时要求的厚氧化层厚度基本吻合。

3.2 后栅氧工艺

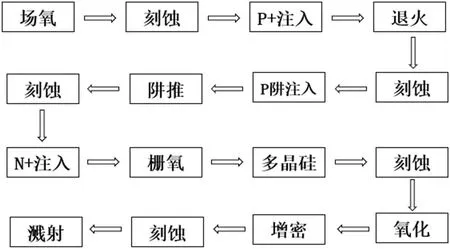

传统功率DMOS 器件的工艺流程多采用多晶硅栅极自对准双扩散工艺,即先生长栅氧化层,再淀积和刻蚀多晶硅,然后利用多晶硅的隔离作用进行离子自对准注入P 区,之后再对P 区进行高温阱推[6]。这种自对准工艺较简单且要求精度不高,由于自对准技术的应用,在关键光刻版之间的套刻误差较小,工艺精度良好,器件的良率和性能更高。但是,在栅氧形成之前,工艺流程中存在的高温热过程,不可避免地会给栅氧化层引入较多的界面态和缺陷[7],导致功率DMOS 器件在抗辐射方面的能力下降,严重影响器件的抗辐射性能。因此为了避免这个高温过程,调整工艺流程,将栅氧工艺安排在P 区注入、高温阱推及N+注入之后,即后栅氧工艺,如图5 所示。相对于自对准工艺,后栅氧工艺对生产线光刻工序的要求较高,这与工艺线精度与工艺成熟度紧密相关。

图3:场氧生长时间与厚氧厚度的关系(T=1000℃)

图4:场氧生长时间与厚氧厚度的关系(time=65min)

图5:工艺流程图

图6:击穿电压曲线

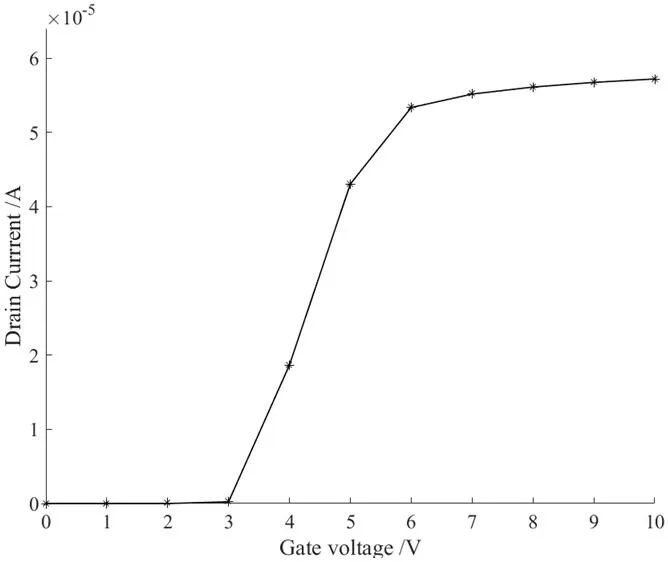

图7:阈值电压曲线

3.3 电性能参数

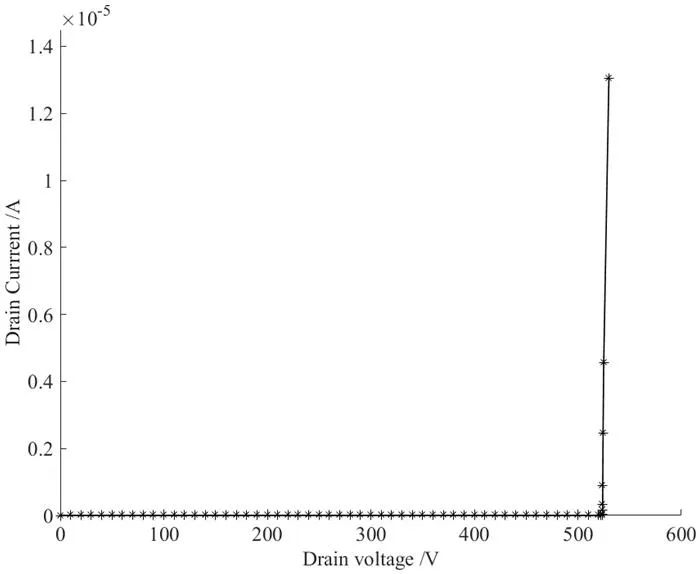

根据前期抗辐射功率DMOS 器件的结构设计要求,在上述的后栅氧工艺流程中对各个单步工艺进行了设计和仿真,特别是厚氧结构的工艺设计,最终得到的器件电性能参数曲线如图所示,图6 是抗辐射功率DMOS 器件的击穿电压曲线,图7 是抗辐射功率DMOS 器件的阈值电压曲线。可以看出,击穿电压达到524V,阈值电压达到3V,满足器件设计要求。

4 结论

功率DMOS 器件的加固技术研究对抗辐射性能的提高具有重要的意义,本文在已知器件结构参数基础上,利用半导体仿真软件对器件的各个结构进行了工艺模拟和器件电参数仿真,满足了器件的结构设计以及电参数要求,确定了N 型功率DMOS 器件的整个工艺流程,为器件的工艺流片奠定基础,也为类似功率DMOS 器件的工艺流程制定提供了参考。