一种多通道高速高精度PXIe 数据采集模块设计*

2021-04-20唐新懿解立坤黄锡汝

唐新懿 ,曹 平 ,解立坤 ,李 超 ,黄锡汝 ,安 琪

(1.中国科学技术大学 核探测与核电子学国家重点实验室,安徽 合肥230026;2.中国科学技术大学 近代物理系,安徽 合肥230026)

0 引言

数据采集技术是信息技术的重要内容,它研究数据的采集、存储、处理和控制问题[1]。 现如今,多通道数据采集系统已经被广泛应用于诸如核物理、高能物理、航空航天、医疗卫生、通信等各个领域中。 随着数据采集需求的日趋复杂[2],人们对采集系统性能指标的要求也越来越高, 例如高采样率、高精度等[3]。 IC 工艺的飞速发展使得ADC 芯片的性能不断提升[4],这让数据采集系统同时具备高采样率与高精度成为可能。 本文设计了一种基于FPGA 的 八 通 道、500 MS/s 采 样 率、14 bit 采 样 精 度的数据采集模块,该模块为标准的PXIe 插卡模块,通过PXIe 机箱背板总线以及机箱控制器与上位机进行通信,最终实现了上位机与FPGA 协同完成数据采集与性能测试。

1 采集卡总体设计

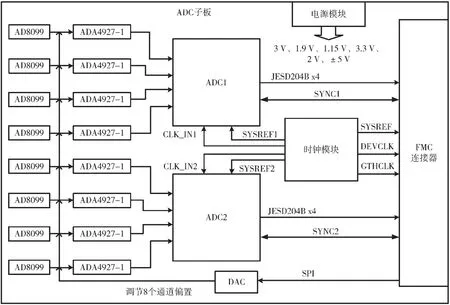

数据采集卡采用子母板的结构:ADC 子板和数据读出母板,子板主要负责对模拟信号进行调理和采集,母板负责将数据传输到上位机,两块板通过FPGA Mezzanine Card(FMC)连 接 器 相 连。 FMC 标 准是一种针对FPGA 的夹层卡标准,通过它可以使设计更具模块化与可拓展性[5]。 模拟信号从子板输入,首先会经过模拟调理电路,对信号进行放大、偏置调整、单端转差分、滤波后进入ADC 进行模数转换,采集下来的数据通过高速串行接口JEDEC Standard No.204B(JESD204B)经由FMC 连接器传输到母板的FPGA,再通过Peripheral Component Interconnect Express(PCIe)总线传输至PXIe 机箱控制器,最后可通过控制器网口传输到上位机。 采集卡的参数配置与数据上传可通过上位机进行灵活控制。 采集系统总体结构如图1 所示。

图1 采集系统总体结构

2 ADC 子板设计

子板电路结构如图2 所示,主要包含两级放大电路、时钟模块、电源模块、ADC 和DAC。 其中,两级放大电路包含一级单端放大器(AD8099)和一级单端转差分放大器(ADA4927-1),DAC 产生的模拟电平输送到差分放大器的反相输入端,可调节信号的直流偏置。 单片ADC 为四通道差分输入,因此共有2 片ADC,对应8 通道模拟信号输入。 时钟模块为2 片ADC 提供必要的采样时钟(CLK_IN1、CLK_IN2)和参考时钟(SYSREF1、SYSREF2),同时为母板的FPGA提供系统时钟(DEVCLK)、参考时钟(SYSREF)和数据传输时钟(GTHCLK)。 电源模块需要为子板所有的芯片供电,提 供了3 V、1.9 V、1.15 V、3.3 V、±5 V 等多种供电电压,此外,还为单端转差分放大器提供了2 V 的共模电压,以适配ADC 的输入要求。

为了实现8 个采集通道的同步,需要满足2 片ADC 接收到的采样时钟、参考时钟、SYNC 信号各自都对齐[6]。 因此,在设计中让2 片ADC 的时钟来源于同一个时钟芯片,并且在PCB 布线时通过等长处理来保证时钟模块输出到2 片ADC 的采样时钟、参考时钟各自的相位对齐。 由FPGA 给到ADC 的SYNC 信号,可在逻辑设计时由同一个核产生,以保证相位的对齐。

2.1 两级放大电路

模拟信号从子板输入后,需要经过两级放大电路的模拟调理,调理包含线性放大、直流偏置调节、单端转差分、滤波,两级放大电路的具体结构如图3所示(NC 表示不连接)。 所选用的单端放大器(AD8099)和差分放大器(ADA4927-1)均为极低噪声的放大器,AD8099 输入噪声密度为输入噪声密度为除此之外,两款放大器还拥有较好的谐波失真性能[7-8]。

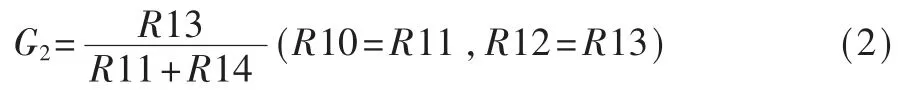

两级放大的电路结构让增益选择更加灵活,可以通过更换电阻的阻值来适应不同的增益需求。 第一级放大器AD8099 的增益为:

第二级放大器ADA4927-1 的增益约为:

图2 子板结构框图

图3 两级放大电路

图3 电路中第一级放大增益为3,第二级放大增益为2。 在只需要一级放大或需要小于1 的增益时,也可通过调整电阻阻值将第一级放大器旁路掉。 在只使用ADA4927-1 时,需要增加匹配电阻R18,以保证输入阻抗为50 Ω。 差分放大器输入阻抗为:

为了达到50 Ω 的输入阻抗匹配,需满足:

同时,反相输入端的匹配电阻也需做相应的更改:

DAC 产生的模拟电平从差分放大器反相端输入,它与差分放大器增益乘积的相反数即为对最终信号的直流偏置调节。 在此模拟电平接入处设置了一个下拉电阻R15,当它存在时,可大大减小DAC接入所造成的信号谐波失真。 选用此下拉电阻是对比测试后的结果,具体可见4.1.1 小节。

R16、R17、C4 组成了低通滤波网络,其传递函数为[9]:

由于高精度的采集系统对前端模拟电路的噪声非常敏感,因此需要尽可能地降低噪声。 除了选用极低噪声的放大器之外,放大器周围的电阻取值在保证环路稳定的前提下需要尽可能小,以减少电阻热噪声,此外,在保证信号能够正常通过的前提下,可尽量减小模拟带宽,以进一步减小噪声。模拟带宽主要通过调整放大器反馈电阻与RC 滤波网络来实现。

2.2 DAC 输出电路

DAC 选型为LTC2666-12,精度为12 bit,通过Serial Peripheral Interface(SPI)接口进行配置,支持8 通道独立配置、独立输出。 DAC 输出电路如图4 所示(仅画出了一个输出通道),其中ADA4004-4 为一款4 通道运算放大器, 可提高模拟电平的驱动能力,R19的设置可进一步减小噪声的引入。DAC 输出电路的设计也是对比测试的结果,具体可见4.1.2 小节。

图4 DAC 输出电路

2.3 时钟模块

ADC 自身的信噪比主要被三个因素制约:量化噪声、热噪声、时钟抖动。 对于流水线ADC,量化噪声通常可忽略;热噪声主要在低频时限制信噪比,而当频率升高时,时钟抖动就成了限制ADC 信噪比的主要因素。 因此对于高速高精度的数据采集系统来说,时钟的质量尤为重要,低抖动的时钟信号才能保证ADC 的分辨率。 采样时钟抖动对ADC 信噪比(Signal-to-Noise Ratio,SNR)的影响可用如下关系表示[10]:

其中,总的时钟抖动(TJitter)包含两部分:内部孔径抖动(TAperture_ADC)和外部时钟抖动(TJitter,Ext_Clock_Input)。 总的时钟抖动可用下式计算:

设计所选ADC 的内部孔径抖动约为120 fs,在信号频率为10 MHz 时信噪比典型值为70.8 dB,根据式(8)、(9)推算,外部时钟的抖动至少应小于4.6 ps。由于ADC 前端还包含模拟调理电路,会额外引入一部分噪声,为保证信噪比,需使用较高质量的时钟源和抖动清除器。 设计选用了支持JESD204B、具有双环路Phase Locked Loop(PLL)的超低抖动合成器和抖动清除器——LMK04821,在12 kHz ~20 MHz范围内,抖动的均方根值可低至88 fs。LMK04821 包含14 路可配置的差分时钟输出,2 片ADC 所需的采样时钟(500 MHz)、参考时钟(7.812 5 MHz),FPGA所需的数据传输时钟(250 MHz)、系统时钟(250 MHz)、参考时钟(7.812 5 MHz)共8 路时钟均由LMK04821提供。

3 数据读出母板设计

母板的主要功能是接收来自ADC 子板采集的数据, 并将其通过PCIe 总线传输到上位机。 FPGA是母板的核心器件, 也是整个采集卡的控制单元。FPGA 内部的逻辑框图如图5 所示。

其中,Xilinx DMA/Bridge Subsystem for PCI Express(XDMA)是Xilinx 公司的一款IP 核[11],它实现了高性能、可配置的离散聚合式存储器直接访问(Direct Memory Access,DMA),并且具有PCIe 协议中物理层、数据链路层和事务层的逻辑功能。 此IP 提供了可选的AXI4 Memory Mapped 或者AXI4-Stream 两种用户接口,实现了与用户逻辑的直接连接,每种接口均可提供PCIe 地址空间和Advanced eXtensible Interface(AXI)地址空间之间的高性能数据传输。 此外,XDMA 还提供了配置管理接口、中断控制信号、时钟信号(AXI_CLK)等可供用户配置使用[12]。 AXI4-Lite 是AXI4 的简化版,是一种简单的、低吞吐量的内存映射总线,主要用于内核和外设寄存器之间的通信。 AXI4-Stream 总线不包含地址项,因此可以允许无限制的数据突发传输规模,主要用于高速数据流传输。 XDMA 的运用使得用户可以通过上位机软件进行在线参数配置与数据上传控制。

数据接收模块用到了Xilinx 公司的IP 核——JESD204,用于接收ADC 通过JESD204B 发送的采集数据, 此IP 包含JESD204B 协议中的物理层和链路层,物理层用于以比特速率接收经过编码的数据,链路层负责处理链路的同步、建立和保持,并对数据进行8B/10B 译码[13]。 紧随其后的解码模块负责对数据进行顺序调整、补码/原码转换等处理,使得处理后的数据便于重建为原始波形。 触发判选模块用于对采集到的信号进行“筛选”,筛选依据为用户配置的通道使能、触发阈值、采集长度等参数,最终将各个使能后的采集通道超过一定阈值的、一定长度的信号“筛选”出来,送入数据打包模块,按照用户自定义的格式进行打包处理,数据包中可包含用户感兴趣的数据类型、通道号、时间、数据包长度等信息。 系统配置模块主要负责通过SPI 接口对各个芯片进行参数的配置,也可对JESD204B 链路进行重置。 ADC 间的同步通过FPGA 分发相位对齐的ADC_SYNC 信号实现。

图5 FPGA 逻辑框图

4 采集卡测试

采集卡的测试主要包括两大部分:偏置调节电路测试与采集卡性能测试。

4.1 偏置调节电路测试

偏置调节电路包括差分放大器反相输入端电路与DAC 输出电路。 传统的单端转差分电路,反相输入端的参考平面通常为地平面,为了实现对信号直流偏置的调节,本设计用DAC 输出的模拟电平来代替地平面。 然而,DAC 的使用会引入额外的噪声并且会增大信号的谐波失真。 为了尽可能减小DAC 对采集卡性能的影响,通过一系列对比测试来确定电路结构。

4.1.1 差分放大器反相输入端电路测试

在差分放大器反相输入端、DAC 输出的模拟电平接入处设置了一个下拉电阻(见图3 中的R15),对比测试了此下拉电阻取不同阻值时采集信号的谐波失真。 测试方法为:用信号发生器产生一个频率为8 MHz、幅度接近ADC 满量程(约-0.5 dB)的正弦波输入采集卡进行采集,DAC 输出模拟电平为0 V,用Fast Fourier Transform(FFT)做出采集信号的频谱图,并计算其谐波失真[14]。在同等条件下,仅改变下拉电阻R15 的阻值,测得相应的谐波失真参数,见表1。

表1 下拉电阻对谐波失真的影响

从对比结果来看,下拉电阻的阻值越小,信号的谐波失真性能越好。 因此,在电路结构中保留了下拉电阻R15 的设置。 与此同时,下拉电阻的存在对DAC 的驱动能力是一个考验。 经过测试,当R15为22 Ω 时,DAC 能 够 为 放 大 器 提 供±479 mV 的 模拟电平,能够满足使用需求。

4.1.2 DAC 输出电路测试

在图4 的DAC 输出电路中,模拟电平输出的方式可以有三种:(1)DAC 直接输出(R19 取0 Ω、无电压跟随器);(2)DAC 经由电压跟随器输出(无R19);(3)DAC 与电压跟随器“同时输出”(R19 取0 Ω)。 对比测试了三种输出方式下采集信号的信噪比。 测试方法与4.1.1 小节类似,在同等条件下,仅改变模拟电平的输出方式,用FFT 测得相应的信噪比参数,如表2 所示。

从对比结果来看,当模拟电平采用方式(3)输出时,有更好的信噪比。

表2 模拟电平输出方式对信噪比的影响

4.2 采集卡性能测试

采集卡性能测试主要包含:模拟带宽测试、噪声测试、ADC 动态性能测试。 测试时采集卡模拟调理电路的增益设置为1,直流偏置为0 V。

4.2.1 模拟带宽测试

带宽描述的是模拟前端可精确测量的频率范围。 带宽定义为正弦波输入信号的幅度衰减到原幅度的0.707 时的频率,也称为-3 dB 带宽。 采集卡模拟前端带宽的测试方法为:用信号发生器(R&S SMA100A)产生一个幅度为Vi(不超过ADC 满量程1.9 Vpp)的正弦波输入到采集卡,逐渐增加输入信号的频率,同时记录每一个频点下ADC 采集到的信号的幅度Vo,Vo/Vi即为模拟前端电路的增益,将其转换为对数,并取初始频点的增益为0 dB,当增益衰减到-3 dB 时输入信号的频率即为采集卡的模拟带宽[15]。 作出增益与输入信号频率的关系曲线如图6 所示。

图6 增益-频率变化曲线

模拟带宽的实测结果为136 MHz,已能满足众多直流耦合的应用场景。

4.2.2 噪声测试

由于采集卡所测信号均为电压信号,因此所测噪声为输入端接地时的电压噪声。 由于采集卡信号输入端有对地的端接电阻R3(见图3),因此无需额外做接地措施。 测试方法为:将采集卡输入端悬空, 用ADC 采集此时的波形, 对所有采样点的码值取其标准差,即为采集卡的噪声。 具体计算公式如式(10)、(11)所示:

其中,Vi为每一个采样点的码值,为所有码值的平均值,n为采样点个数,Vδ为所有采样点的标准差。ADC 能识别的最小刻度表示为最低有效位(Least Significant Bit,LSB),其码值的单位通常用LSB 表示。一共测量了122 880 个采样点,计算得到其标准差为2.172 LSB。 由于14 位ADC 总 共包含16 384 LSB,满量程为1.9 Vpp, 因此2.172 LSB 对应为0.252 mV。因此,采集卡的噪声为0.252 mV。

4.2.3 ADC 动态性能测试

ADC 的动态性能参数主要包含:无伪峰动态范围(Spurious Free Dynamic Range,SFDR)、信噪比(Signalto-Noise Ratio,SNR)、总谐波失真(Total Harmonic Distortion,THD)、信纳比(Signal-to-Noise and Distortion Ratio,SINAD)、有效位(Effective Number of Bits,ENOB)[16]。目前通常采用FFT 频谱分析法来测试ADC 的动态性能,它可以将ADC 采样结果中各个频率成分的幅度计算出来,然后依据ADC 各个动态性能参数的定义进行计算。

具体测试方法为:用信号发生器(R&S SMA100A)产生一个幅度接近ADC 满量程的正弦波(约-1 dB),经过对应频率的带通滤波器后输入到采集卡,将ADC 采集到的数据用FFT 进行分析,得到各个动态性能参数。 选取了采集卡模拟带宽内的9 个频点,选取动态性能参数中的4 个进行了测试,测试结果如表3 所示。 其中10 MHz 的时域波形如图7 所示,频谱图如图8 所示。

所测得的ADC 有效位接近11 bit,略低于手册的参考值,考虑到性能测试时包含了前端模拟调理电路,因此测试结果符合预期。

表3 ADC 动态性能参数测试结果

图7 ADC 采集信号典型时域波形(10 MHz)

图8 ADC 采集信号典型频谱图(10 MHz)

5 结论

本文设计了一种8 通道14 位500 MS/s 的数据采集卡,使用时可调整模拟调理电路以适应不同信号特征,在其模拟调理电路增益设置为1、直流偏置为0 V 时进行测试,ADC 动态性能良好,有效位约为11 bit,接近芯片指标。 对于经过测试验证的ADC,后续设计可在本文所提框架不变的前提下,将其直接放在母板上,子板上仅放置模拟调理电路,根据不同的信号特征准备相应的子板即可,不需要频繁更换电阻,使用起来更方便。 本文所设计的采集卡为标准的PXIe 模块,通过PXIe 机箱扩展及同步授时,可进一步构建规模更大的多通道高精度的信号采集仪器,在实验物理、信号采集、通信、电子信息等领域有着广泛的应用。