层次化设计方式下的电子自动化设计

2021-03-16天门职业学院彭丽君

天门职业学院 彭丽君

电子自动化技术在现代数据系统开发中发挥了非常重要的作用,在进行该技术设计过程中,第一步要明确需要实现的具体功能,再利用时序仿真进行验证,确认无问题后将这些模块划入到基础元件中,最终实现总的设计任务。电气自动化设计的输入类型包含了原理图模式以及硬件描述语言模式,其中VHDL以及Verilog HDL是现阶段常用的硬件描述语言模式.为了进一步探究层次化设计方法在电子自动化设计中的应用,以VHDL输入类型为载体,探究了秒表的设计方法,在显示屏上以“X:XX.XX”的形式显示7位数字。各个信号插孔通过ds1~ds7引出来,同时将段选信号连接起来,设置两个按钮,分别实现清零功能与启停功能,实现了秒表的层次化设计与开发。

伴随着现代电子技术的快速发展,电子自动化技术依托于硬件扫描语言实现了FPGA以及CPLD芯片的编程工作,从本质上解决了数字系统开发过程中存在的问题。在我国许多高等院校规划了电子自动化技术学科,但是在教学活动开展中显现出了较多的问题,比如说课堂教学内容与实践需求不吻合、教学内容较为抽象,难以理解、教学体系不成熟等。电子自动化技术的编程目标主要是FPGA以及CPLD芯片,并基于Quartus软件运用环境,通过层次化设计模式进行数字系统开发。为了进一步探究层次化设计方法在电子自动化设计中的运用,本文以Quartus软件为载体,系统的阐述了层次化设计流程以及使用方式,同时选取秒表开发为示例,探究了层次化设计模式的具体运用。

1 电子自动化设计中层次化设计方法应用

1.1 层次化设计思路

在正常的硬件设计过程中,一般是先进行元件类型与型号的选取,然后将这些元件组装起来,从而实现某些特定的功能,这样的设计思路也可以应用到电子自动化设计中,只是在使用方法上具有更强的灵活性与变化性。在进行层次化设计过程中,首先要明确需要实现的功能,然后依照功能的不同将其划分为若干个相互独立的子模块,保证各个子模块功能的正常运行,再利用时序仿真进行验证,确认无问题后将这些模块划入到基础元件中,最终实现总的设计任务。伴随着设计任务完成的越来越多,不仅帮助设计人员积累了大量的经验,同时也会有效的提高元件库的规模,能够为设计者接来下的工作提供便利,可以有效的提高开发速度。

层次化设计模式在设计过程中,是采用从上往下的方式开展分析设计工作的,并将总任务分类为相互独立的各个子模块,但是在功能实现上却采用从下往上的方式逐个实现的。

1.2 电子自动化设计的输入类型

电子自动化设计的输入类型包含了两个方面,分别是原理图模式以及硬件描述语言模式。首先,原理图模式主要指将元件放置到画布上,紧接着通过导向使得各个元件的引脚连接起来,再规划输入引脚与输出引脚,从而实现电子自动化设计。这种输入方法具有操作简单、较为直观的优点,但是也存在Quartus软件库中可供其运用的元件数量较少的缺陷。其次,硬件描述语言模式的应用,帮助设计人员解决了硬件开发细节上的难题,设计人员不需要全面掌握每个硬件的开发标准,通过程序指令进行元件的逻辑功能叙述就可以实现相应的功能。通过该模式的应用为硬件设计带来了极大的便利,也是电子自动化设计中普遍应用的方法。现阶段常用的硬件描述语言模式有VHDL以及Verilog HDL等,下文中秒表的开发就是基于VHDL开展的。

2 基于层次化设计方式的秒表开发研究

为了进一步探究层次化设计方法在电子自动化设计中的应用,本文以较为简单的秒表为例进行实证分析,系统并详细的说明该设计方法的思路与流程。秒表具有开始计时、结束计时、暂停与继续计时、清零等功能,在显示屏上以“X:XX.XX”的形式显示7位数字。各个信号插孔通过ds1~ds7引出来,同时将段选信号连接起来,设置两个按钮,分别实现清零功能与启停功能。

2.1 秒表的层次化设计与开发

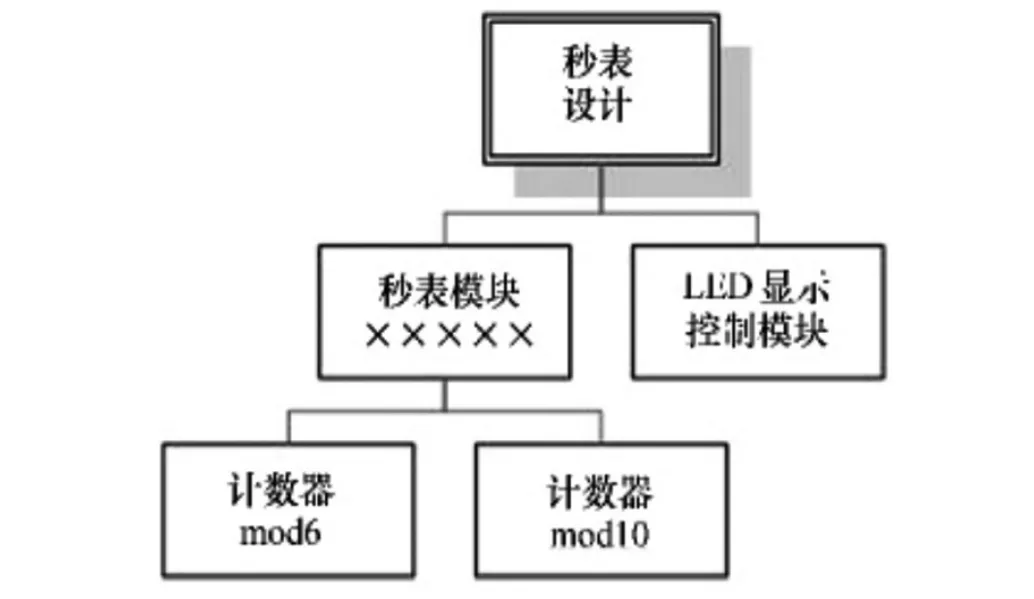

第一步要明确设计任务,并根据任务将其分解为若干个相互独立的子模块。在秒表开发中可以分为秒表模块以及LED显示控制模块。其中秒表模块中涵盖的时、分以及秒均为计数器,为了更好的在LED显示屏中显示,对分与秒的十位数进行单独处理,通过这样的设置完整实现秒表功能所需要的计数器规格与数量为3个计数值为0~9以及2个计数值为0~5的计数器,图1所示为层次设计框架示意图。

图1 层次设计框架示意图

2.2 秒表的层次化开发实现

在进行秒表层次化设计时,在完成相关功能是要依照从下往上的原则进行,首先要完成下层模块设计,之后基于完成的下层模块进行上层模块设计,确保各个功能都能够顺利实现。

(1)最下层的计数器设计

基于VHDL输入类型,根据秒表要实现的功能,完成mod6以及mod10计时器的开发工作,同时将设计完成的文件取名为mod6.vhd以及mod10.vhd.

(2)第二层秒表模块开发

用原理图输入模式完成秒表模块开发工作,第一步双击mod6.vhd文件,通过选单新建symbol文件;第二步双击mod10.vhd文件,并在里面新建symbol文件;第三步建立新的原理图文档timer.bdf,使用鼠标左键点击画布空白地方,打开symbol文件窗口,这是会在Project文件里面自动生成mod6以及mod10元件,见图2所示。

通过硬件描述语言VHDL实现秒表开发任务,首先建立新的HNDL文件,并将文件名称设置为timer.bhd,紧接着在系统框架中设立mod6以及mod10的元件注释,最后依照实际状况规划mod6以及mod10的实例,参考程序如下。

图2 Project文件 生成mod6与mod10元件

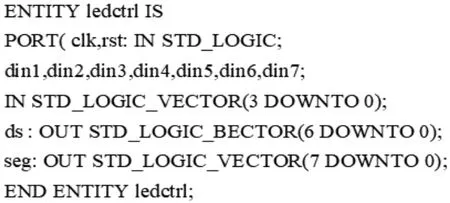

该环节主要进行LED控制器的设计与开发。首先通过硬件描述语言VHDL实现LED控制模块功能,并将该文件命名为ldectrl.vhd,于此同时还需要对LED控制器进行实体定义,具体代码程序如下。

层次设计方式在电子自动化设计中具有非常广泛的应用,在进行硬件设计时先明确硬件的类型与信号,之后以灵活的方式将各个硬件连接起来,在输入类型上包含了原理图模式以及硬件描述语言模式,为了进一步探究电子自动化设计中层次化设计方法的应用,以秒表为例进行了实证研究,为不断提升电子自动化的设计水平提供支持。