基于FPGA的PCIe转光纤数据注入式仿真装置

2020-12-08吴亚军

吴亚军

(海军装备部,陕西 西安 710000)

实时信号处理设备通常运用在雷达、声呐等含有特殊传感器的装备上,这些装备制造成本高昂,在信号处理设备的处理算法研制过程中不可能每次都搭载传感器进行处理验证。如在鱼雷上装备信号处理设备,只有在整条雷下水航行时才能采集到实际的航行数据,实验成本极其高昂。为了解决这些问题,通常采用仿真方式模拟某些场景,但是仿真场景与实际航行的情况仍存在很大差别,无法全面验证算法的有效性,并且场景模拟仿真的成本仍较高,无法满足复杂算法调试过程中需要频繁运用实际数据的要求。数字信号的注入式仿真则是一种有效的解决方案。该方案将某次实际运行的数据通过特殊方式注入信号处理设备,信号处理设备就能在实验室环境下实时处理实际工作的数据,并且可以反复处理,如数据量足够大,则能够对算法的性能进行较为充分的验证。

随着处理器技术的不断发展,在互联领域,高速差分总线技术代替并行总线技术是大势所趋。PCIe于2001年正式发布,是Intel公司开发的第三代IO总线标准。PCIe总线是串行技术,可以在很高的频率上传输数据,所以在保证数据完整性的同时有很高的带宽。其中,PCIe Gen1标准X1通道单向传输速率为2.5 GB/s,PCIe Gen2标准X1通道传输速率为5 GB/s,PCie Gen3在传输通道速率为8 GB/s。光纤也常用于高速差分总线数据的传输,在FPGA中通过光纤传输数据传输速率可超达10 GB/s,并且光纤传输数据具有传输速率高、传输距离远以及传输安全性高等特点,在各个领域应用已越来越广泛。

本文设计的基于FPGA的PCIe光纤数字信号处理设备注入式仿真装置利用FPGA将上位机通过PCIe发送到板卡DDR3的数据输出到高速收发接口GTP经光纤发送到数字信号处理设备,GTP设置传输速率为4 GB/s,因而整个系统有效数据传输带宽可达400 MB/s,满足数字信号处理系统对实时仿真数据输入带宽的要求。

1 系统设计

实现PCIe接口系统设计主要有两种方式:一种为桥接芯片,将PCIe总线转接到本地总线,如很多商用计算机的PCIe设备的连接方式,该方式由于受到本地总线传输速度和总线转换的影响,数据传输带宽不会很高;另一种为基于FPGA的实现,目前主流FPGA厂商都将PCIe核集成到FPGA产品中,可以快速开发基于PCIe的设备。

本系统设计了基于FPGA的信号处理设备注入式仿真装置,主要由FPGA处理核心、DDR3数据缓存单元、光纤模块、PCIe接口、数据发送计算机以及信号处理单元接端FPGA组成。系统组成框图如图1所示。

图1 系统组成框图

核心处理FPGA采用Xilinx公司的ZYNQ7000系列中的XC7Z015-CLG485芯片,该芯片采用ARM+FPGA SOC技术,芯片将双核ARM Cortex-A9和FPGA集成在一颗芯片上,同时芯片内部集成了AMBA、内部存储器、外部存储器接口和外设。PS端采用双核ARMCortex-A9处理器,采用ARM-v7架构主频最高可达766 MHz;每个CPU有32 KB一级指令和数据缓存,512 KB二级缓存2个CPU共享;集成片上boot ROM和256 KB片内RAM;在外部存储接口方面,支持16/32 bit DDR2、DDR3接口。PL端逻辑资源丰富,含有4路高速GTP收发器,最高支持PCIe Gen2 X4,由于本设计用到了PCIe和SFP光纤接口,因而,PCIe占用2路GTP高速收发器实现PCIe Gen2 X2模式,光纤占用1路GTP高速收发器。

本文设计的数据转换装置DDR3存储芯片直接挂载在ZYNQ芯片的PS端,由ARM核心操作访问,在本系统中,上位机将待注入数据直接通过PCIe接口写入到DDR3缓存中,ARM从DDR3缓存中将数据读出,通过DMA发送到PL端。PS端挂载2片DDR3芯片,位宽32,内存读写时钟533.33 MHz,数据读写速度可达1 066 MHz,这里设读写效率DDR3为70%,那么,系统的外部数据存储带宽可达2.9 GB/s,完全满足常用数字信号处理系统的注入式仿真数据要求。

由于采用的ZYNQ7000芯片只有一个GTP Bank,含有2组4路GTP高速收发器。本设计中,由于要采用PCIe接口和SFP光纤接口,二者只能共同连接到同一个GTP Bank上,该Bank上包含两组差分输入时钟,分别分配给PCIe的100MHz输入时钟和SFP光纤的125 MHz输入时钟。通常在设计硬件程序时,通过高速收发模块gtwizard核和PCIe核同时配置各自的输入时钟即可,但是由于每配置一次高速收发模块的时钟,均需要一个共用逻辑GT_COMMON模块,在该款ZYNQ芯片中只包含一个共用逻辑GT_COMMON模块,但是一个GT_COMMON有2个QPLL输入输出,因而需要将两组高速收发模块的时钟在同一个GT_COMMON中进行独立区分,GT_COMMON的PLL0OUT必须连接到GT_CHANNEL的PLL0上,PLL1OUT必须连接到GT_CHANNEL的PLL1上,如此可满足在同一个GTP Bank实现PCIe和SFP光纤。

ZYNQ作为系统的核心处理单元承担了所有的数据处理部分。上位机由板卡的PCIe接口直接通过PCIe DMA操作访问PS内存区域,将需注入信号处理设备的数据写入DDR3中。PCIe核采用Vivado中的XDMA核,该核包含PCIe核和DMA模块两部分,主要用来发送、接收数据,发送引擎主要负责将待发送的数据按照PCIe协议组成不同类型的TLP数据包,并发送给PCIe IP核;发送DMA控制模块主要负责把DDR3中读取的数据转换成TLP格式,并传送给发送引擎;接收引擎用于从PCIe IP核接收不同类型的TLP数据,接收DMA控制模块用于实现存储器读请求包的发送流量控制及接收数据位宽的转换;DMA状态控制寄存器模块主要用来解析PC对模块内部寄存器的命令和配置,并通知发送引擎模块、接收引擎模块及其他模块做出相应执行。

PS端通过AXI_DMA模块将数据从DDR3中读取输出到PL端。上位机将数据写入DDR3的特定地址。当PL端向PS端产生请求数据中断时,PS端启动DMA数据传输,AXI_DMA核从DDR3中读取数据并输出到PL端。在PL端,按照AXI协议将数据接收到FIFO缓存等待写入下一级数据发送缓存。当AXI_DMA传输完成一批数据后,该IP核向PS端发起中断,通知PS端本批次数据传输完成。

AXI_GPIO核用于PS端到PL端状态的传输。当上位机向DDR3中写入板卡复位或者PS端向PL端DMA数据发送完成时,PS端通过GPIO核将复位状态发送完成状态输出到PL端,从而PL端可以做出相应的操作。另外,PL端还可以通过GPIO将状态输出到PS端。

PS端使能了两组从AXI高性能数据传输通道,数据位宽64位,分别用于AXI_DMA模块和XDMA模块的数据传输。本设计中,数据时钟为200 MHz,该接口可提供1 600 MB/s的数据传输带宽。该通道为包含高带宽数据通路的PL总线设备提供了到DDR3和片上内存(OCM)的存储器通道,每个接口内部包含两个FIFO缓冲区,分别用于读和写流量。同时使能了一个通用目的AXI主接口,将IP核的配置信息通过PS状态写入AXI_GPIO、AXI_DMA及其他AXI核,用于各个IP核工作模式的配置及核的启停。同时,PS端使用3路外部中断输入:一路接入AXI_DMA数据传输中断,另外2路接入PL端的其他输入,分别用于传输启动和请求数据,该两组信号在上升沿分别向PS端发起中断,PS端接收到中断后立刻启动相应的数据传输工作。各个AXI模块传输时钟由PS端产生一个200 MHz的时钟,所有AXI模块均在该时钟下工作。

在PL端,SFP数据发送模块采用双缓存乒乓操作实现数据连续发送。在本系统中,每次发送的数据量为104 KB/5.12 ms,在逻辑中例化了2个128 KB的双口RAM,双口RAM输入端连接到从AXI数据接收到的数据缓存FIFO输出端,每104 KB数据通过200 MHz时钟分别写入两个双口RAM进行缓存。在数据发送端,按照数据发送节奏将数据从双口RAM输出端读出,通过GTP高速收发器发送到信号处理设备的SFP接收单元。数据发送模块与信号处理设备通过光纤存在数据交互,当数字信号处理设备需要数据时,向本系统发送使能请求,本系统立即启动数据发送状态机开始发送,每发送一次数据均在头部添加包头,用于信号处理设备解析并排列数据。数据发送状态机如图2所示。

图2 数据发送状态机

2 软件设计

本文设计的信号处理注入式仿真设备的核心芯片ZYNQ包括硬件逻辑设计和ARM软件设计两部分。系统硬件逻辑上面已经进行了介绍。系统的核心控制和数据交互工作由ARM核心来完成,该芯片的ARM为双核Cortex-A9处理器,运行主频为667 MHz。本系统只运行了一个Cortex-A9处理器核心。该处理器控制整个软件系统的初始化、数据由DDR3向PL端的DMA传输以及各个中断的初始化及响应。程序初始化后,首先是初始化PL端产生的中断,本软件设计了2个PL端中断。第一个是发送使能中断,仿真系统启动后,当PL端接收到信号处理设备发送过来的发送启动信号后,PL端向PS端产生一个上升沿中断,PS端立即开始向PL端发送一批次的数据;第二个中断是PL端每发送完一批数据到信号处理设备后,产生下一批数据的要数中断,PS端接收到要数中断后,将程序中的对应标记置位。初始化中断后,程序开始初始化AXI_DMA模块,首先初始化DMA传输完成中断,使DMA每发送完成一批数据都由DMA模块产生一个中断信号到PS端;然后初始化AXI数据解析模块,使设计的AXI数据解析模块开始工作,等待DMA通过AXI总线传输过来的数据;然后创建多描述子数据连续传输机制,每个描述子对应的缓存空间最大可支持8 233 607字节,由于本系统使用的芯片PL端逻辑资源有限,AXI数据解析模块中的缓存FIFO设计为4 KB,这样也有利于AXI解析模块接收数据的缓存,本设计中每次传输数据大小为104 KB,这里将104 KB数据分成52次,每次传输2 KB,如此后端的缓冲单元不会溢出,同时也满足仿真系统对数据传输带宽的要求。

程序初始化完成后,就开始等待上位机的操作指令及PL端的中断信号。当上位机按下初始化按钮后,上位机通过PCIe将DDR3中的标记位置为特定值;然后上位机选择要发送的数据文件,文件选择完成后系统即启动一次DMA传输,将数据缓存在PL端的一个双口RAM中,等待信号处理设备的启动信号;上位机按下开始按钮后,就开始等待板卡DDR3的对应位置是否被PS端设置成特定值,同时等待上一次DMA操作是否完成,是否由要数中断产生,如都是,则上位机再将一批数据写入板卡的DDR3。软件流程图如图3所示。

图3 软件流程图

3 实验及讨论

这里设计的基于FPGA的信号处理设备注入式仿真装置对外接口只有光纤和PCIe接口,主要功能均在FPGA内部实现,因而设计过程中的结果验证能够影响系统设计的效率。Xilinx的Vivado对于硬件逻辑的设计过程提供了良好的解决方案,Vivado的集成逻辑分析仪(ILA)IP核能够实时监测硬件逻辑程序中的任意信号的波形,可根据实际需求设定波形采集的深度,是硬件逻辑设计过程中验证各个功能模块逻辑功能的有力工具。

在本系统设计过程中,从PS端将数据从DDR3读出,通过DMA写入PL端和PL端通过光纤接口与信号处理设备的数据收发交换是调试过程中需要监测的关键数据。图4为PS端通过DMA向PL端写入双口RAM的时序图。当数据写入有效时,开始向两个双口RAM中的一个写入数据。本设计采用两个双口RAM做乒乓操作实现数据的连续传输。DMA模块将数据写入AXI数据接收模块,写入时钟为200 MHz,该模块将有效数据缓存到FIFO中,同时PL端将数据从FIFO中读出,写入双口RAM中进行乒乓操作。当一批数据写入完成后,等待一批数据完成后,程序中的乒乓标记翻转,同时向PS端发送请求中断,数据发送到PL端后,写入另外一个双口RAM中。

图4 PS端向PL端的RAM写入数据时序图

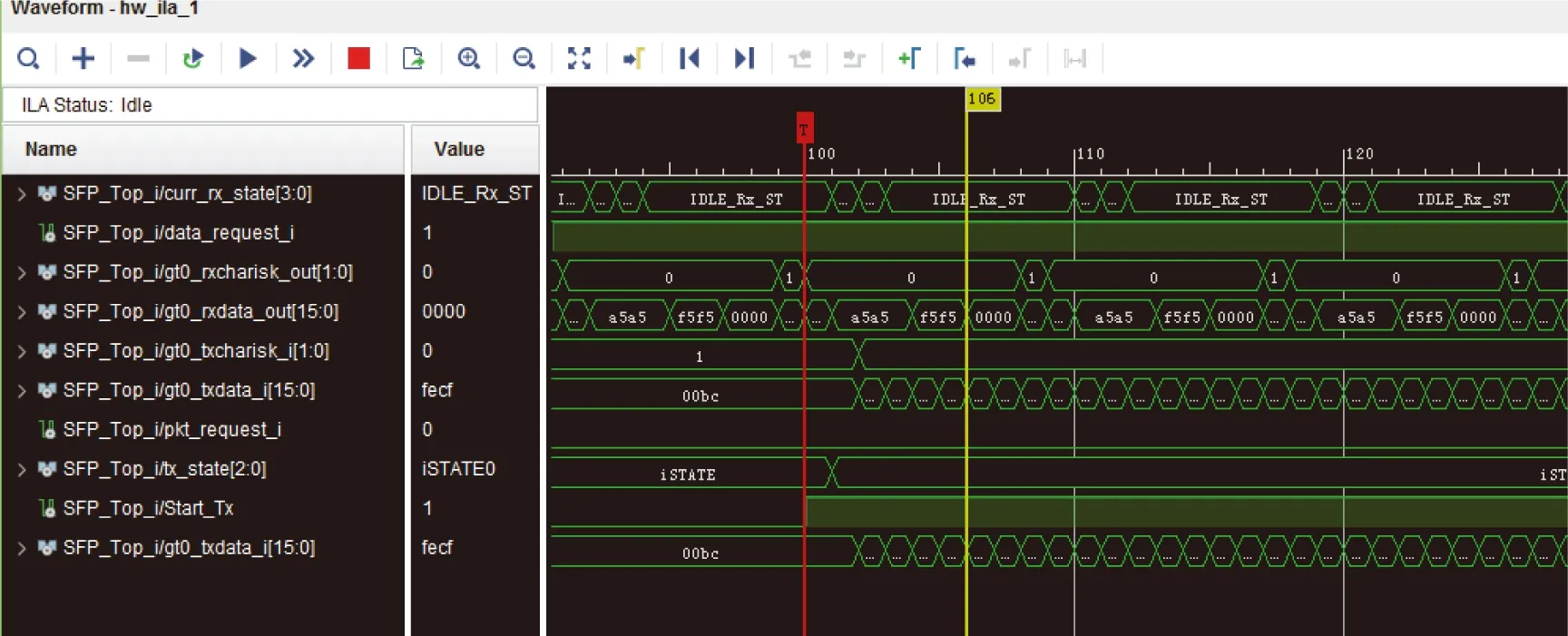

图5为光纤模块的数据收发时序图,图中接收到信号处理设备发送过来的数据发送使能信号,将data_request_i置高,当PS端向PL端发送完成一批数据后,PS端向PL端写一个GPIO变化信号,这里为Start_Tx信号,当GPIO发生翻转后该信号即被拉高,信号被拉高后即可触发数据发送状态机向信号处理设备发送双口RAM中的数据。

图5 PL端与信号处理设备数据收发时序图

4 结束语

本文设计了一种基于FPGA的PCIe光纤信号处理设备注入式仿真装置。系统采用了ZYNQ 7000 FPGA为核心处理芯片,上位机通过PCIe将数据写入FPGA的DDR3缓存,FPGA的PS将数据通过DMA写入PL端,PL端用两个双口RAM对数据进行乒乓操作,通过光纤与信号处理设备进行数据交互,按信号处理设备的实际节奏需求将数据发送给信号处理设备,使信号处理设备可以通过光纤接收到的数据进行原始信号处理实时仿真,使信号处理设备能够完美复现实际工作时的数据状态,对信号处理设备中算法的调试开发具有重要意义,可在实验室环境下对信号处理设备的算法性能进行充分验证,降低实验成本和装备开发周期。