一种基于二阶广义积分器和延时信号消除算子的改进型锁相环研究

2020-11-13王庭康

王庭康,龚 杰

(强电磁工程与新技术国家重点实验室(华中科技大学),湖北 武汉 430074)

0 引言

随着可再生能源的发展,并网逆变器作为分布式电源和电网接口,在向电网输送电能方面发挥着重要作用[1-6]。并网逆变器的安全稳定运行需要锁相环(phase-locked loop, PLL)来提供相位同步。当电网电压发生畸变或不平衡时,如何保证精确、快速的锁相对并网逆变器的控制性能起着至关重要的作用[7-10]。

在三相系统中,锁相环的目标是快速准确地获得三相电网电压的基波序分量。一种广泛应用的方法是同步旋转坐标系锁相环(synchronous reference frame PLL, SRF-PLL),它可以在理想的电网电压下快速、准确地获得锁相结果,但当电力信号发生畸变时,会产生锁相误差[11-17]。虽然可以通过减小控制系统的环路带宽来抑制它,但在稳态性能和动态性能之间存在一个折衷。文献[4-5]提出了双同步旋转坐标系解耦锁相环(decoupled double synchronous reference frame PLL, DDSRF-PLL),它通过双同步旋转坐标系分离正负序分量,对三相不平衡电网具有良好的锁相性能。同样,畸变电压也很难实现快速相位同步。文献[6-7]提出了双二阶广义积分器锁相环(PLL based on double second-order generalized integrator, DSOGI-PLL),它首先用带通滤波器滤除谐波,然后用对称分量法分解基波正序分量,实现不平衡电压的相位同步。然而,如何在保证快速响应和良好滤波效果的同时设计出一个滤波效果好的带通滤波器值得研究。文献[8-9]中提出一种消除所有次谐波的延迟信号抵消(delay signal cancelation,DSC)算子,但对于许多次谐波,实现起来更为复杂。针对电网电压不平衡和畸变的情况,提出了一种基于DSOGI和DSC的锁相环。对于DSOGI,增加了带宽,只对高次谐波进行滤波,提取正序分量,保证了不平衡量的精确相位同步。DSC算子用于滤波低次谐波,与低通滤波器(low pass filter, LPF)相比,可以大大缩短延迟时间,提高动态响应性能。仿真结果表明,该方法在电网电压幅值和频率变化的情况下具有快速、准确的特点,能够对电网电压不平衡和畸变做出快速响应。

1 同步信号算法的锁相环结构

1.1 二阶广义积分器及其改进

对于常规的二阶广义积分器正交信号发生器(SOGI-quadrature signals generator, SOGI-QSG)而言,如图1(a)所示,二阶广义积分器传递函数[11]:

(1)

根据SOGI-QSG的框图,整个系统的传递函数为

(2)

式(2)中,2个传递函数分别表示经过SOGI滤波后电压与实际电压之比,经过SOGI正交滤波之后电压与实际电压之比。它本质上是一个二阶带通滤波器,其幅频特性和相频特性可由式(2)推导出:

(3)

(4)

图2 D(s)和D′(s)的伯德图Fig.2 Bode diagram of D(s) and D′(s)

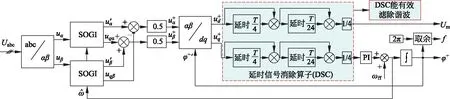

1.2 改进型锁相环结构设计

为了解决电网电压不平衡和畸变情况下的精确快速锁相问题,图3提出了快速相位同步方法。该锁相环由DSOGI-QSG、正序分量计算模块、延时信号对消模块和PI调节器组成。

图3 锁相环控制结构框图Fig.3 Control structure block diagram of the proposed PLL

对于正序分量计算模块,基于对称分量法[18],正序分量可以表示为公式(5)所示:

(5)

(6)

2 延迟信号消除算法

延迟消除算子的基本思想是:对于直流分量叠加在交流分量上的信号,在特定的时延之后,将信号加到原始信号中,然后除以2,消除其中的交流信号,而不影响直流分量。在图4中可以清楚地看到。DSC运算符可以表示为式(7)所示(其中Dn是DSC运算符)。

图4 DSC滤波的原理示意图Fig.4 Principle of DSC operator

(7)

假设具有特定频率的交流量可以表示为

(8)

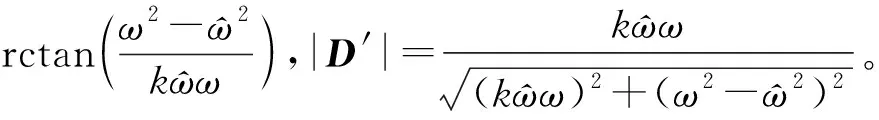

将式(8)代入式(7)计算,得:

(9)

为了消除特定次数的谐波,需要满足Dn(f(t))=0,很明显,继而需要满足cos(hπ/n)=0,即

(10)

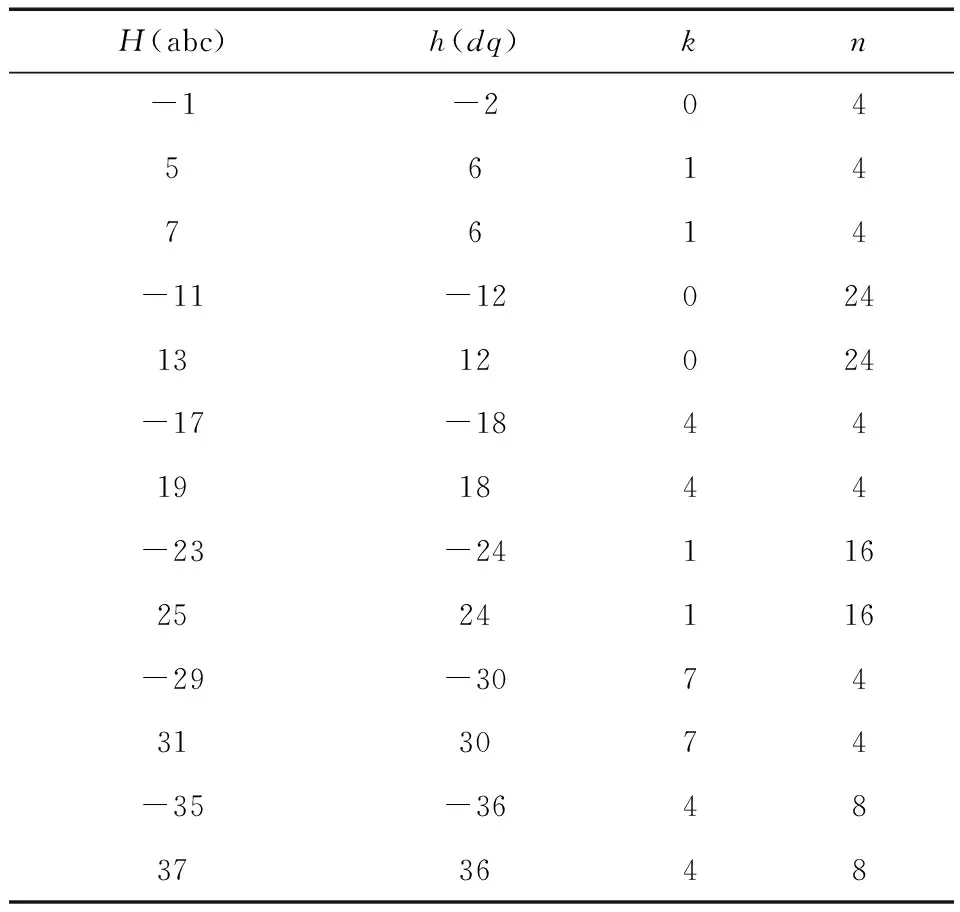

对于式(10),通过选择适当的延迟系数n,算子可以消除n次谐波。对于三相电网,谐波次数一般为6k±1(k=0,1,2,…n)。表1显示了每个谐波所需的延迟系数n,h(abc)表示abc坐标系中的调和阶;h(dq)表示相应转换为dq坐标系的谐波阶数。一个DSCn运算器可以同时消除多个谐波,不需要为每一个谐波都配备DSCn运算器,从而缩短了延时时间。

如表1所示,当电网电压发生畸变,用DSC滤除所有特定次谐波时,DSC运算子的延迟时间为分别为D4,D8,D16,D24。显然,延迟时间如下:

表1 DSC运算可消除的谐波分布规律Table 1 DSC operators needed to eliminate harmonics

(11)

另外,D4的s域传递函数为

(12)

GD4(s)的幅频特性和相频特性如图5(a)和(b)所示。通过对伯德图的分析可知,DSC运算子能完全滤除以上所分析的特定阶次的谐波,并能准确跟踪电网电压中含有直流分量、负序分量和谐波分量时的频率和相位。

图5 GD4(s)的伯德图Fig.5 Bode diagram of GD4(s)

3 仿真验证与结果分析

为了验证所提出的锁相环快速相位同步在电网电压不平衡和畸变等情况下的有效性,在Matlab/Simulink软件中建立了仿真模型。为了更加突出本文提出基于二阶广义积分器和延时信号消除算子DSC锁相环的有效性,在图6、7和8中,分别与当前广泛应用的单同步坐标系软件锁相环(single synchronization reference frame-software phase lock loop, SSRF-SPLL)进行了对比,表现了电网电压幅值变化、三相不平衡电网电压和电网电压频率变化时的同步性能。

如图6(a)和(b)所示分别为本文所提PLL和SSRF-PLL在电网电压幅值发生变化时的锁相过程。其中,对比图6(b)中SSRF-PLL锁相过程,由图6(a)可知当电网三相电压在0.1 s和0.16 s分别发生突降30%和突升30%的情况下,相位的获取过程几乎不受任何影响,同时频率可以在15 ms之内准确得到。因此,除了在幅值变化时频率有小幅波动(PI控制器参数的影响)外,可以取得和当前使用广泛的SSRF-PLL锁相一致的效果。

图6 电网电压幅值变化时锁相过程Fig.6 Phase-locked process for grid voltage jumping

如图7(a)和(b)所示,当电网bc两相电压幅值在0.1 s和0.16 s分别发生跌落20%和上升20%时,提出的锁相环相位同步、频率信息获取整个过程本文PLL和SSRF-SPLL的仿真波形。根据该仿真图7(a)可知,如果电网电压三相不对称,由于DSOGI可以提取出三相不平衡电压中的正序分量,通过对正序分量进行Park变换后对q轴分量进行PI调节器的调节,保证在三相不平衡时锁相。而对于图7(b)在三相不平衡时SSRF-SPLL锁相过程,电压幅值一直有波动,且频率不能够准确得到,同时锁相的角度也发生很大偏差。因此,本文锁相环可以在三相不平衡情况下,15ms内准确地完成锁相并获得电压频率信息。

图7 电网电压三相不平衡时锁相过程Fig.7 Phase-locked process for three-phase unbalance

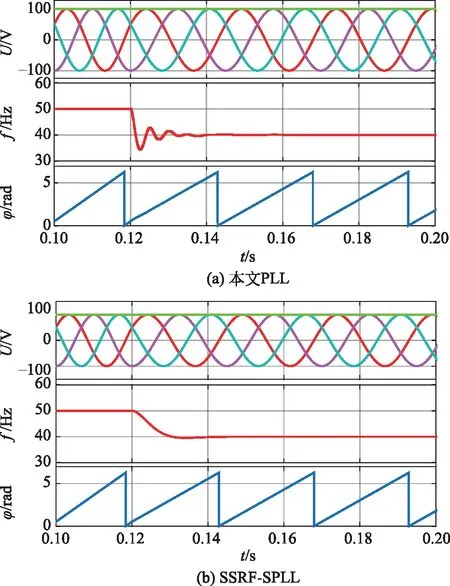

如图8(a)和(b)所示为电网频率变化时的本文PLL和SSRF-SPLL的锁相过程。当三相电网电压频率在0.12 s时由50 Hz变为40 Hz时,由于双二阶积分器的频率自适应性的作用,会随着大电网频率的变化自动调整,结合图8(a)所示的仿真结果可知,本文提出的信号同步算法方案在频率发生大幅度波动的情况下,也能保证相位同步几乎不受影响,频率自适应在一个周期内完成,可以取得如图8(b)中SSRF-SPLL锁相几乎一致的效果。

图8 电网电压频率变化时锁相过程Fig.8 Phase-locked process for frequency changing

为了验证DSC在电网电压畸变情况下的滤波性能,如图9所示,将SSRF-SPLL,DSOGI-PLL和本文提出的信号同步锁相环方案进行了对比仿真分析。在0.1~0.16 s的时间内,电网电压发生畸变,加入了含量为30%的5次谐波。通过图9(a)本文PLL、图9(b)DSOGI-PLL以及图9(c)SSRF-SPLL仿真结果图形比较发现,本文提出的锁相环几乎不受谐波的影响,电压幅值可以准确检测,畸变时刻频率几乎没有波动,锁相快速准确;当DSOGI-PLL的电压幅值受DSOGI的影响时,很难滤除系统的带宽限制,频率波动,同时由于DSOGI的带宽限制,DSOGI-PLL的电压幅值很难完全滤除,频率也会波动;而对于如图9(c)中SSRF-SPLL锁相过程而言,不能够有效抑制谐波所带来的影响,在含有背景谐波情况下,频率一直处于非常大的波动状态,且锁相得到的实时角度发生畸变,十分不准确。因此,本文PLL在电网电压含有背景谐波情况下,相对于SSRF-SPLL和DSOGI-PLL方案,能够利用DSC算子消除谐波所带来的锁相困扰,准确且快速完成锁相过程。

图9 电网电压畸变时锁相过程Fig. 9 Phase-locked process for Voltage distortion

因此,通过在Matlab/Simulink软件中建立了仿真模型,模拟了上面4种情况(电压幅值跌落或上升、三相不平衡、频率发生变化、含有谐波),与广泛使用的SSRF-SPLL进行了对比分析,本文所提方案都能够很好地完成锁相过程,在电压幅值跌落或上升和频率发生变化情况下,能够取得和SSRF-SPLL几乎一致的锁相效果;在三相不平衡情况下,较SSRF-SPLL而言,具有更好的锁相效果。特别地,相对于传统的DSOGI-PLL而言,在电压发生畸变情况下,SOGI-QSG设置的参数一致,本文方案能够滤除完全含有谐波,且具有更好的动态响应速度,锁相效果更好。

4 结论

在电网电压不平衡和畸变的情况下,对于整个电力电子装置稳定运行而言,一个快速且准确的信号同步算法的锁相环是基本且重要的一个环节。

本文提出了一种利用DSOGI和DSC算子提高滤波性能以及应对三相不平衡的锁相环。首先,分析了DSOGI的基本原理及其改进方法,改进方法中系统频带宽度与系统增益参数相关,其值的设置需要折衷考虑动态响应速度与滤波效果,而本文中该环节仅滤除高次谐波即可,达到了减小响应时间的目的。然后,当三相不平衡时,通过DSOGI-QSG环节,利用对称分量法提取正序分量,经过Park变换,通过PI调节器控制dq同步旋转坐标系中q轴分量为零,实现锁相。特别地,尽管DSOGI中滤除了高次谐波,但考虑到还有电网畸变条件下可能存在低次谐波,采用延时信号消除算子DSC滤除低次谐波,相对于传统低通滤波器而言,其延时时间可以大大缩短,提高了动态响应速度。

最后,在Matlab/Simulink软件中建立仿真模型,将广泛使用的SSRF-SPLL和本文PLL在电网电压幅值跌落或上升、三相不平衡、频率发生变化、含有谐波4种情况下进行了仿真,在电压幅值跌落或上升和频率发生变化情况下,能够取得和SSRF-SPLL几乎一致的锁相效果;在三相不平衡情况下,较SSRF-SPLL而言,具有更好的锁相效果。且相对于传统的DSOGI-PLL而言,在电压发生畸变情况下,本文方案能够滤除完全含有谐波,具有更好锁相效果。因此,本文所提基于DSOGI和DSC算子的PLL除了完成SSFR-SPLL的锁相效果外,能够在电网不平衡和存在谐波污染的情况下实现快速锁相。