Ka波段BiCMOS低功耗驱动放大器设计

2020-11-06王绍权廖余立王鑫

王绍权 廖余立 王鑫

摘 要:该文介绍了一款Ka波段(33.0 GHz~37.0 GHz)低功耗驱动放大器。此放大器使用SiGe BiCMOS工艺设计,其采用了Cascade级联结构,提高了放大器的电源电压和工作频率带宽,通过实现共射极与共基极的级间匹配,可以有效地提高放大器的增益。测试结果表明:在33.0 GHz~37.0 GHz频率范围内,放大器增益大于15.0 dB,OP-1dB为-6.0 dBm。此放大器采用5.0 V供电,工作电流为8 mA,面积为0.7 mm2。

关键词:Ka波段;放大器;SiGe BiCMOS;有源相控阵雷达

中图分类号:TN722.3 文献标识码:A 文章编号:2096-4706(2020)12-0047-04

Abstract:In this paper,a Ka-band(33.0 GHz~37.0 GHz) low power driver amplifier is presented. This amplifier tapes out with SiGe BiCMOS process. To improve its power supply and the bandwidth,cascade structure is used. For effectively obtain high power gain of amplifier,the inter-stage matching network between common emitter circuits and common base circuits is used. The measurements indicate that the power gain is larger than 15 dB,the OP-1dB is -6.0 dBm from 33.0 GHz to 37.0 GHz. The power supply is 5.0 V and the static current is 8 mA and the area is 0.7 mm2.

Keywords:Ka-band;amplifier;SiGe BiCMOS;active phased array radar

0 引 言

現代有源相控阵由成千上万个天线和收发多功能(T/R)模块构成。它们通过雷达电扫描技术控制阵列天线的每个阵元或子阵的相位,改变波束方向,从而实现波束扫描[1]。目前Ka波段,商用的T/R多功能芯片大多采用GaAs或者InP等性能优异的工艺设计。然而这种Ⅲ-Ⅴ族化合物工艺成本昂贵、芯片面积大,不易将基带功能集成在其中,难以满足T/R多功能小型化的需求。

20世纪80年代以来,SiGe BiCMOS得到了迅猛发展,其SiGe HBT的截止频率(fT)已达到120.0 GHz以上,性能接近或与GaAs器件及其电路相当。这使得SiGe BiCMOS工艺成为了实现低成本小型化T/R多功能芯片替代工艺的最佳选择。

SiGe BiCMOS工艺提供了浅槽(STI)和深槽(DTI)两种隔离方式,能有效降低数字模块与射频模块之间的噪声干扰。由于衬底损耗、趋肤效应、邻道效应加剧,导致硅基无源器件损耗比较大,但是成本低廉、集成度高等优势依然使得SiGe BiCMOS工艺在微波毫米波电路中应用广泛。

基于上述考虑,本文采用SiGe BiCMOS工艺设计了一款工作在Ka波段的驱动放大器,放大器采用Cascade结构,使用CPWG结构参与电路匹配,并采用温度补偿偏置电路,放大器测试增益大于15.0 dB,OP-1dB为-6.0 dBm,工作电流仅为8 mA,芯片面积仅为0.7 mm2。

1 SiGe BiCMOS工艺介绍

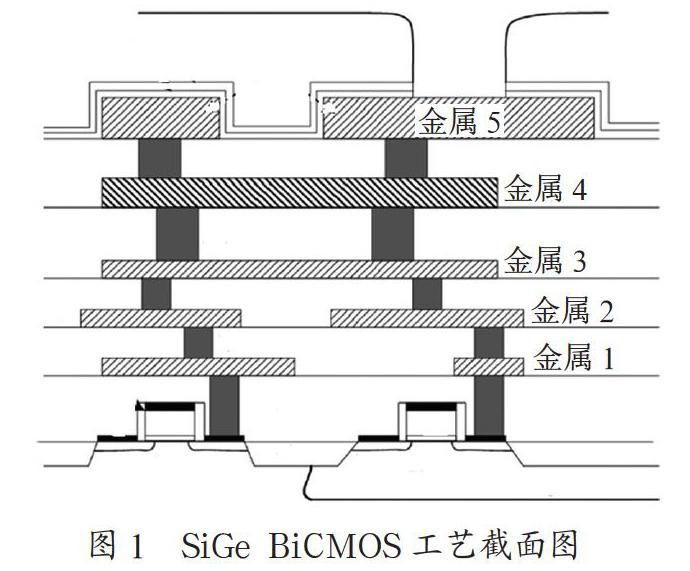

本设计采用SiGe BiCMOS工艺,此工艺中NPN晶体管的类型有高击穿型和高性能型;高击穿NPN晶体管的BVCEO为8.0 V,截止频率为40.0 GHz;高性能NPN晶体管的BVCEO为5.5 V,截止频率为120.0 GHz;本文设计的放大管选择选择高性能NPN晶体管,其标称截止频率fT大于120.0 GHz,满足设计频率要求,和电压要求。此工艺提供MIM电容和MOM电容选择,MIM电容为金属-介质-金属电容,适合高频应用;MOM电容有金属-氧化物-金属叉指电容,其单位容值高,适合低频模拟应用。本设计选用单位容值为1 fF/μm2的MIM电容。此工艺提供多种类型电阻,Poly电阻、扩散电阻和膜电阻。

设计中,射频通路电路选择膜电阻,提高精度,模拟偏置部分选择Poly电阻,增加阻值。此工艺提供5层可选金属,包括,金属1、金属2、金属3、金属4和金属5(如图1所示)。金属5为厚金属层,其厚度为3.4 μm,射频走线与电感选择金属5层,以增大电感的Q值,提高放大器功率输出能力。模拟偏置电路选择金属1和金属2层,金属3层用作地隔离层,将射频电路与模拟电路隔离开,减小射频电路与模拟电路间的耦合。

2 驱动放大器设计

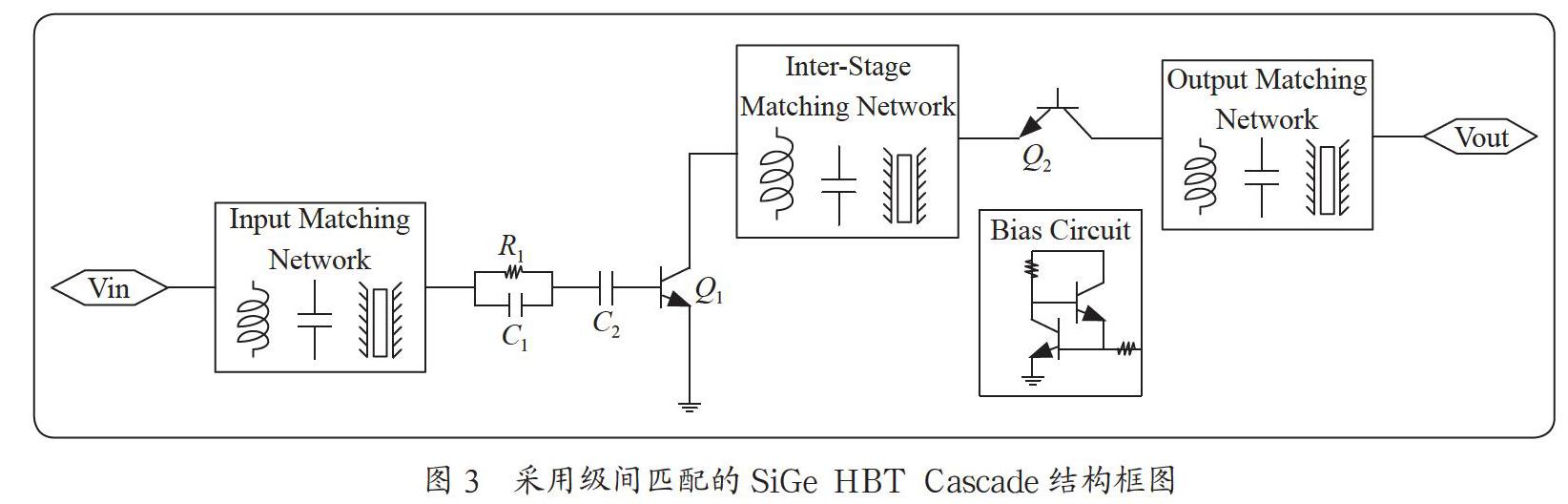

如图2所示给出了传统SiGe HBT Cascade结构框图。其中晶体管Q1和Q2分别构成了共射极放大器和共基极放大器。Cascade结构中Q2晶体管级的增益约为1,能有效地降低晶体管Q1的密勒电容,增大了由密勒电容产生的极点频率,从而极大地提高放大器的带宽,此外还能提高输入端口与输出端口之间的隔离和产生更高的增益,同时提高放大器的工作电源电压。然而如图3所示,Cascade放大器在几个GHz范围内能提供大概12.0 dB~16.0 dB的增益,如果直接将这种结构应用于Ka频段,由于晶体管Q1和晶体管Q2单管在Ka频段提供的最高增益严重降低,两者间存在巨大的反射以及较大的无源器件损耗,会严重恶化放大器的增益。如图3所示,本文在传统Cascade放大器的基础上加入了CPWG传输线和MIM电容作为两级放大器的级间匹配,有效提高了放大器的增益。

本文采用CPWG传输线结构,而未采用应用范围较广的微带线结构和CPW结构,主要考虑到CPWG传输线结构具有更好的信号屏蔽能力,能极大地降低衬底损耗,同时能轻易达到各层金属的工艺密度要求,提高芯片成品率。

如图4所示,给出了Ka驱动放大器的详细原理图。Q1为主放大管,Q2为共基极放大管,TL1和TL2为CPWG输入匹配电路,C2为隔直匹配电路,TL3为CPWG级间匹配电路,C3为级间匹配电路,TL4和TL5为CPWG输出匹配电路,C4为输出隔直电容。电阻R1和MIM电容C1能提高放大器低频段稳定性。大尺寸电容C2能提高放大器的高频段稳定性。

Cbp为电源线上的旁路电容,Q3、Q5、Q6为偏置电路晶体管。

在图4原理图中,电源VCC与A点、A点,B点、B点、B点,C点、C点具有相同的直流电压,同时都是射频地。如图5所示,放大器的版图设计中Q1晶体管的偏置电路供电端、Q2晶体管的偏置电路供电端以及放大器的电源电压VCC的版图位置并不相同,为降低三者间的共模干扰,在每个电路的版图供电处各加入旁路电容,从而保证供电端的交流地较为理想。

3 偏置电路设计

本设计主放大级的放大器偏置采用温度补偿偏置电路,温度补偿偏置电路由温度相关电流产生电路和电流镜偏置电路组成[2]。温度相关电流产生电路如图6所示。

图6中,PMOS1和PMOS2构成带隙基准电流镜,QB1和QB2构成带隙基准核心电路,QB2和QB1的面积比例为n,PMOS3、PMOS4、PMOS5和PMOS6构成偏置电流镜,PMOS3和PMOS4构成比例关系。基准电流IREF为温度相关变量。NPN三极管的I-V特性为:

电流镜偏置电路由图7给出,它由电流镜和扼流电路组成。PMOS3、PMOS4、PMOS5和PMOS6构成偏置电流镜电路,它能将基准电流IREF放大N倍。

RB为放大器偏置扼流电阻,CB为偏置端滤波电容,它可以过滤掉偏置电路的耦合信号。三极管Q4與放大管Q1同为电流镜结构。它将Q4集电极电流放大M倍为放大器提供直流偏置。

本设计共基极放大器偏置如图8所示,Q5和Q6构成偏置管,产生偏置电压CB2为偏置端滤波电容,为射频信号提供良好的交流地。

4 测试结果

如图9所示,给出了Ka驱动放大器芯片实物照片,芯片面积仅为0.7 mm2。

如图10所示,驱动放大器的在片测试方案采用了矢量网络分析仪PNA-X N5244A,直流电源电压为5.0 V,其工作电流为8 mA。

如图11所示,给出了Ka驱动放大器的S11和S22的实测曲线,可以看出S11的仿真曲线与测试曲线在34.0 GHz以上几乎重合,而S22的测试结果优于仿真结果。如图12所示,给出Ka驱动放大器的增益曲线和隔离度曲线,可以看出在35.0 GHz以下,放大器的隔离度小于-40.0 dB。而放大器的增益测试结构比仿真结果小了大约1.0 dB。可以看出实测数据的S21的平坦度控制在±0.4 dB以内。

此外,经测试,此放大器在33.0 GHz~37.0 GHz内的OP-1dB约为-6.0 dBm。

表1给出了本文的驱动放大器与其他基于SiGe工艺设计的相关放大器的性能比较。可以看出相比于同类设计,此驱动放大器有较高的综合性能。

5 结 论

本文设计了一款用于Ka有源相控阵T/R模块的驱动放大器,对以后Ka放大器的设计有着指导性作用。本文放大器是基于SiGe BiCMOS工艺设计,放大器采用Cascade结构,使用CPWG结构参与电路匹配,并采用温度补偿偏置电路。测试结果表明:在33.0 GHz~37.0 GHz频率范围内,放大器增益大于15.0 dB,OP-1dB为-6.0 dBm。此放大器采用5.0 V供电,工作电流为8 mA,芯片面积小于0.7 mm2。下一步工作主要是针对提高仿真与测试的拟合度和放大器的驻波及OP-1dB等性能做进一步的优化。

参考文献:

[1] 石星.毫米波相控阵雷达及其应用发展 [J].电讯技术,2008,48(1):6-12.

[2] 刘德志,王绍权,王鑫,等.用于相控阵雷达的X波段SiGe低噪声放大器 [J].半导体技术,2019,44(2):104-109.

[3] GATHMAN T D,BUCKWALTER J F. A Ka-band high-pass distributed amplifier in 120nm SiGe BiCMOS [C]//2010 IEEE MTT-S International Microwave Symposium.Anaheim:IEEE,2010:952-955.

[4] RIEMER P J,BUHROW B R,COKER J D,et al. Ka-band (35 GHz)3-stage SiGe HBT low noise amplifier [C]//IEEE MTT-S International Microwave Symposium Digest,2005.Long Beach:IEEE,2005:1037-1040.

[5] MA Q,LEENAERTS D,MAHMOUDI R. A 30GHz 2dB NF low noise amplifier for Ka-band applications [C]//2012 IEEE Radio Frequency Integrated Circuits Symposium.Montreal:IEEE,2012:25-28.

[6] LI Y H,GOH W L,XIONG Y Z. A Cascaded Distributed Amplifier Operating Up to 110 GHz Using SiGe HBTs [J].IEEE Microwave and Wireless Components Letters,2014,24(10):713-715.

[7] RIEMER P J,HUMBLE J S,PRAIRIE J F,et al. Ka-Band SiGe HBT Power Amplifier for Single-Chip T/R Module Applications [C]//2007 IEEE/MTT-S International Microwave Symposium.Honolulu:IEEE,2007:1071-1074.

[8] BYUNG W M,REBEIZ G M. Ka-Band SiGe HBT Low Noise Amplifier Design for Simultaneous Noise and Input Power Matching [J].IEEE Microwave and Wireless Components Letters,2007,17(12):891-893.

作者简介:王绍权(1987—),男,汉族,河北石家庄人,硕士,工程师,研究方向:射频集成电路。