基于Proteus的数字钟的设计与实现

2020-10-22雷佳鑫李娜

雷佳鑫 李娜

摘 要:本系统采用小规模集成电路构成数字钟的硬件电路。利用多谐振荡器产生时间标准信號,三个计数器(分别为60进制,60进制,24进制)用来设定“时”、“分”、“秒”信号,并输出分,小时,天的进位信号。译码显示电路则用来将“时”“分”“秒”显示出来。由于计数的起始时间不可能与标准时间一致,故需要在电路上加个校时电路可以对分和时进行校时。另外,计时过程要具有报时功能,当时间到达整点前10秒开始,蜂鸣器有间隔地地响5秒钟。

关键词:数字钟;振荡;计数;校正;报时

0 引言

数字电子钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。数字电子钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

1.硬件电路设计

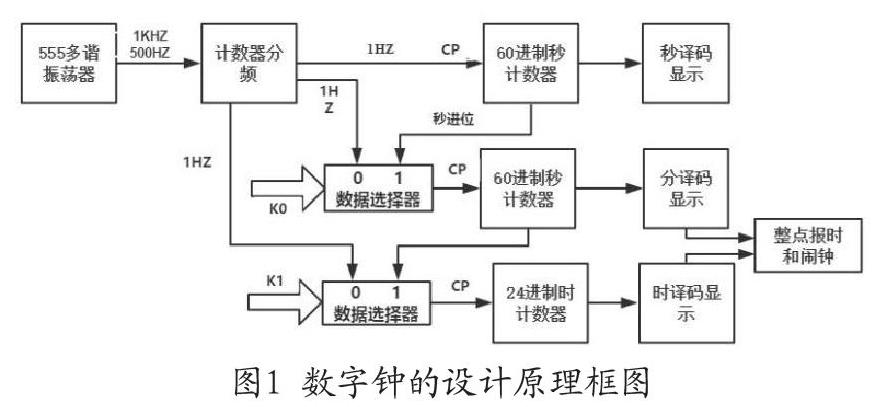

数字钟的设计框图与原理如图1所示。首先,用555多谐振荡器产生的方波脉冲信号,再用计数器分频得到1HZ的方波脉冲信号,作为时钟脉冲信号CP。其次,设计出1个24进制计数器和2个60进制计数器分别连接7段数码管,用来显示时、分、秒。接着,用2个数据选择器控制小时计数器和分钟计数器的时钟脉冲频率,完成快速校时校分的功能。最后,用数据选择器选择整点报时和闹钟时间,控制扬声器振动发声。

1KHZ信号可通过555定时器的多谐振荡器来产生。依据,取,可得。取,取滑动变阻器。有关分频,我选取3个异步清零同步置数的十进制计数器74ls160来完成分频功能。

时分秒数字显示电路需用两片74ls160组成60进制计数器,采取异步清零方式,则60作为清零状态。即权重为40、20的通过与非门接清零端,即Q6和Q5通过与非门接清零端。同理可得,24可作为24进制计数器的清零状态,即将输出端的Q5和Q2通过与非门接清零端。

校时校分电路即用数据选择器来选择计数器的低位片频率。数据选择器的使能端由手动开关控制,开关断开则数字钟正常运行,闭合则用来校时校分。即开关的断开闭合可以控制0、1信号的转换。

整点报时电路即分计数电路计至59分,时计数电路计数51、53、55、57、59时扬声器电路通。由下图的真值表,当扬声器发声时,,。而若,必定为0,因此不必考虑的值。

闹钟电路即在时计数器计至8,分计数器计0,秒计数器计0-9扬声器振动发声。时计数器的接或非门得。由于低位片为8时,和必为0。有关分计数器,低位片和高位片的四个输出端均接或非门,得和。秒计数器则使高位片输出端接或非门即可。

2 软件仿真结果

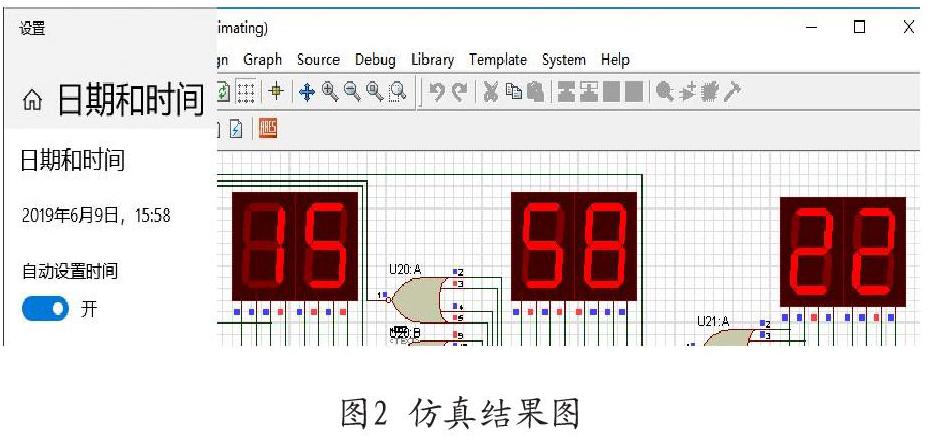

经过proteus仿真软件和实际实验室接线验证,该设计能满足以下功能:用数字显示时、分、秒(23h59m59s);具有快速校时、校分的功能;具有整点报时功能(从59分51秒开始鸣叫5响,四低一高);具有闹钟功能(每天六点起床闹铃一分钟)。

3 结论

设计的数字钟电路能够满足市场上所用数字钟的所有要求,例如快速校时校分,整点报时以及闹钟功能等。本次设计仅利用了数电的相关知识进行应用,原理简单,容易实现,应用广泛。

参考文献

[1]王迎勋,王香,黄家平,臧红岩。基于Multisim13的数字钟的设计与仿真[J].科技创新与应用,2017,09:63-64.

[2]黄文锋。基于74LS192的可倒计时数字钟设计--以Multisim10为例[J].湖州职业技术学院学报,2017,01:73-76.

[3]庞宇擎,李仲男。多功能数字钟的设计与实现[J].电子制作,2016,01:13+12.

[4]许雪成。计数器在数字电路中的应用[J].科技创新与应用,2016,04:299.

作者简介:

第一作者:雷佳鑫,1999.06,女,蒙古族,江苏金湖,南京师范大学本科在读,

通讯作者:李娜,南京师范大学,副教授,研究方向:微滴喷射、导电 材料打印成型、三维打印