基于Zynq-7100数据存储模块的设计

2020-09-27郑骏徐海纳

郑骏 徐海纳

摘要:数据存储模块广泛地用于雷达、医疗、通信等行业。随着雷达系统高数据率、小型化的要求,对数据存储模块带来了更大的挑战。针对相关要求,设计了一款基于Zynq-7100的数据存储模块。该数据存储模块一方面采用Zynq-7100内的PL实现raid0方式完成对多路mSATA盘的控制,以及高速采集数据的收发;另一方面采用Zynq的PS实现自定义文件,完成了对mSATA盘的管理。模块测试结果表明,设计的数据储存模块速度高,性能稳定,并有效地减少了设备的体积。

关键词:Zynq-7100;raid0;mSATA;文件系统

中图分类号:TP311 文献标识码:A

文章编号:1009-3044(2020)23-0045-02

数据存储模块是用来对系统运行、系统测试或科学试验等过程中产生的数据流或信号进行记录,后期向用户提供获得的原始数据的设备。其广泛应用于军工、安全、控制、航天航空等领域。随着雷达系统的发展,高速多通道采集技术的成熟,对相应的数据存储模块提出了更大的要求:1)高存储速率,可以实时连续记录高速的原始数据;2)大存储容量,满足采集设备下发的海量数据的存储;3)存储可靠性,保证存储设备稳定的工作,以及存储数据的正确性;4)小型化设计,在保证存储容量的同时,需要减少系统的体积,有一定的扩展性。

Xilinx公司的全可编程Zynq-7100系列芯片成功将高大1GHz的Cortex-A9 MPCore双核处理器与低功耗可编程逻辑紧密集成在一起;并在ARM处理器与FPGA之间采用AXI4通信总线,在器件内部提供了高可靠性,高带宽的通道。结合该器件的优势,设计实现的数据存储模块相对于其他架构的存储模块具有存储速率高,存储空间灵活的特点。

1 数据存储模块总体设计

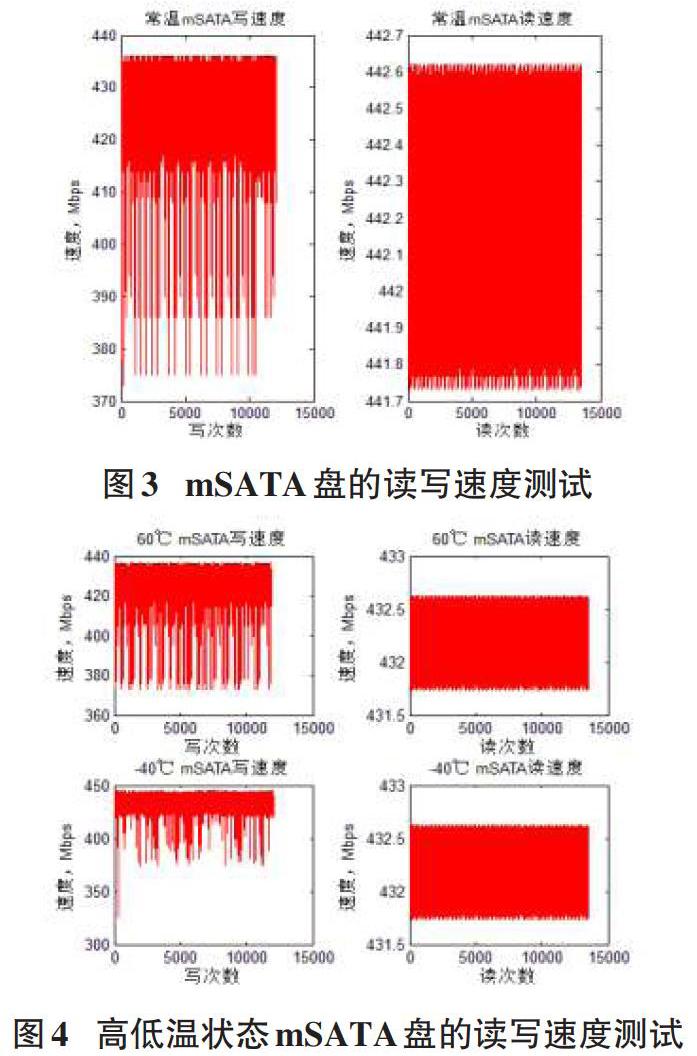

基于Zynq-7100数据存储模块由数据处理单元和数据存储单元两部分组成,数据存储模块总体框图如图1所示。

数据处理单元完成高速数据的接收,存储自定系统的数据打包,数据写入读取,以及外部通信、调试的工作。

数据存储单元由mSATA固态硬盘阵列构成,提供1TB~8TB的存储空间的扩展,以及410MB/s~3.2GB/s的数据读写速率。

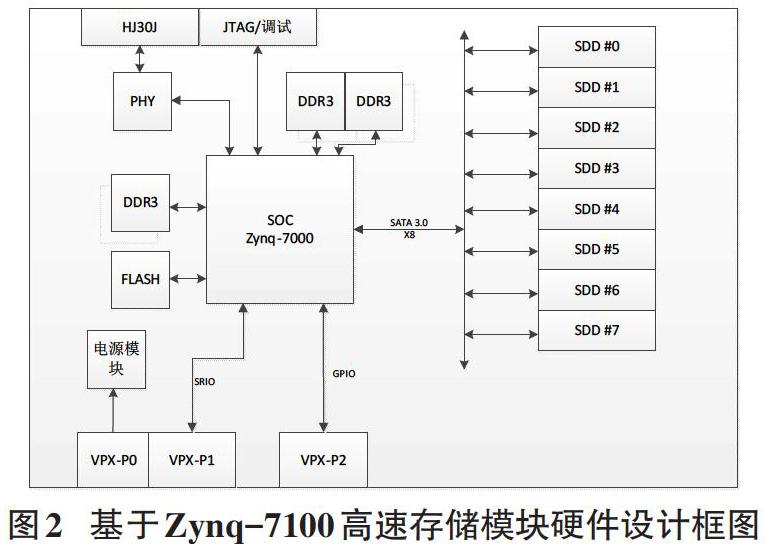

2 硬件构成与设计

基于Zynq-7100数据存储模块硬件设计框图如图2所示。模块为标准的6U VPX结构,其主要由Zynq-7100处理平台,数据存储单元DDR3、FlASH,文件存储单元,以及通信外设组成。

2.1 Zynq-7100处理平台

Zynq-7100处理平台主要实现高速数据的接收,存储文件的生成,存储,转储,以及系统状态检测的功能。

XC7Z100芯片为Xilinx公司Zynq-7000系列的全可编程Soc,PL单元提供1组X4的SRIO接口;提供8组SATA接口;提供多个交互接口。PS单元则提供以太网接口,以及串行接口。

借助AXI(高级扩展总线)互联技术,实现芯片内部PL与PS之间的高性能的数据交换。为自定义文件系统的生成,文件数据管理方面提供了片内高速可靠的途径。

2.2 数据存储单元

数据存储单元分为3个部分:数据缓存、内存以及配置存储部分。

数据缓存单元采用两组MT29F系列芯片,构建容量为4GB存储数据的缓存。

内存单元采用2片MT41K系列芯片以及1GB的数据空间,完成系统的运行。

配置存储单元采用256Mb的QSPI FLASH芯片,用于系统的上电配置以及引导。

2.3 外部通信单元

外部通信单元主要有以太网通信单元,串口通信单元,以及GPIO接口单元。

以太网通信单元,选用100/1000M传输速率自适应功能的以太网物理层芯片88E1116。配合XC7Z100芯片PS单元的MAC层控制器,实现以太网通信功能。

串口通信單元,选用电平转换芯片MAX3232。配合XC7Z100芯片PS单元的串口控制器,实现串口通信功能。

GPIO接口单元,由XC7Z100芯片PL单元直接提供,采用电平转换芯片进行信号的保护。

2.4 文件存储单元

文件存储单元由mSATA固态硬盘构成。其读写速率可达到410MB/s,物理接口为mSATA接口。

设计中固态硬盘通过接插件安装在电路板上。可实现多达8块固态硬盘的安装。可以根据需要安装灵活安装所需的固态硬盘。

3软件系统架构与设计

本设计采用Vivado2017.4设计套件完成软件系统的架构与调试工作。按照存储的功能,将整个系统分为五个功能模块,分别为高速数据接口管理模块、数据缓存管理模块、文件系统管理模块、RAID控制管理模块,状态显示模块。

3.1 高速数据接口管理模块设计

高速数据接口管理模块主要通过Zynq-7100的高速串行数据收发控制器实现的控制功能,提供存储系统对外的数据交互控制。

接收数据经过高速数据接口管理模块。如果是模块的控制指令,将被分发到文件系统管理模块;反之将分发到数据缓存管理模块。

发送数据经过高速数据接口管理模块,区分模块的状态数据、转储数据,供外部系统使用。

3.2 数据缓存管理模块设计

由于数据存储单元(mSATA)在数据存储时会有短暂性的带宽下滑,以及数据偶发的数据传输错误出现,采用DDR3存储芯片实现输入数据的缓存。

数据存储模块对外的数据输入接口为X4 SRIO,最大数据速率为5Gb/s×4×0.8=2GB/s(即每秒有2GB的数据需要写入)。而模块的数据存储单元最大为8个固态硬盘,最大数据速率为410MB/s×8=3.2GB/s(即出现最坏的带宽下滑情况,抑或数据传输错误情况下的数据量为3.2GB)。

此外数据存储模块可实现对DDR3芯片组的控制,其读写最大数据速率为1600Mb/s×16×1/8=3.125GB/s(即每秒可满足3.125GB的数据要求)。可以在数据缓存的容量以及数据率的两个方面满足系统需求。

3.3 文件系统管理模块设计

文件系统管理模块实现在Zynq-7100的PS端。使用自定义的文件系统,该系统支持文件的建立、命名、信息备注等功能。对每个文件的扇区地址进行了管理,用户只需指定文件ID号。当需要对存储数据进行读写操作时,文件系统管理模块将获取文件对应的扇区地址,并完成相关操作。

3.4 RAID控制管理模块设计

设计中通過Zynq-7100 PL端的数字逻辑实现mSATA盘的控制和管理。SATA控制管理模块遵循SATA协议。使用Zynq-7100集成的高速串行数据收发控制器实现SATA数据的解码、同步以及RAID工作。

3.5 状态显示模块设计

本板指示灯显示模块主要将本模块中各个电源轨的反馈信号,mSATA盘在位信号,工作状态等信息,通过板载的LED灯反馈工作状态。

状态信息上报模块将mSATA盘的工作状态,电源轨工作状态,系统周期自检信息等通过以太网形式进行发送给上位机,实时观测。

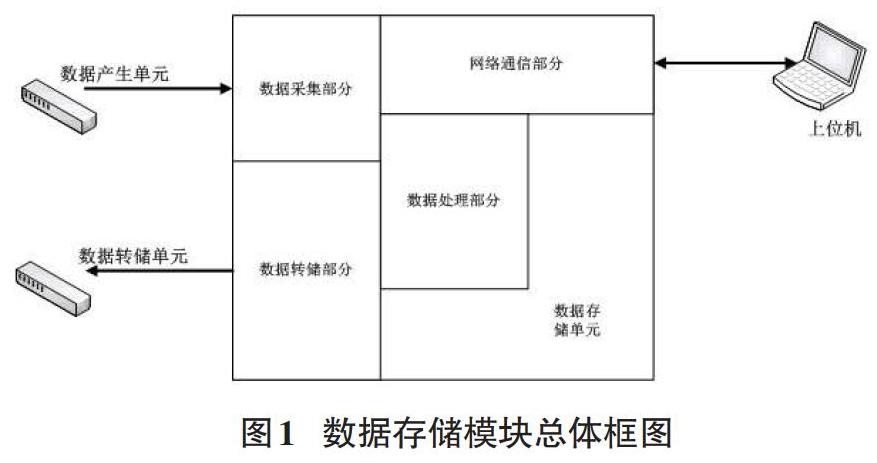

4模块测试与分析

对数据存储模块性能进行测试,将模块通过母板与数据产生板相连接。模块采用8个mSATA盘(容量1TB)做为存储介质,内部的缓存区设置为1Mb。对连续的数据进行写入操作,每个mSATA盘的测试结果如图3所示。在高温60℃,低温-40℃的环境中进行相同测试。每个mSATA盘测试结果如图4所示。

满足对于模块具有1TB~8TB的存储空间的扩展,以及410MB/s~3.2GB/s的数据读写速率的设计要求。

5 结论

基于Zynq-7100数据存储模块软硬件相结合的设计,以及相关的测试结果表明,使用该平台进行存储模块的设计方法,为高速存储模块的设计提供了可行的设计方案。基于Zynq-7100处理平台的设计,即具备了FPGA硬件可编程的优势,又将文件系统有效的移植到Cortex-A9处理器上完成,满足了高速率、大容量以及小型化的需求。

参考文献:

[1] 杨佳朋.SATA控制器的设计与FPGA验证[D].太原:太原理工大学,2013.

[2] 李晔.基于FPGA的嵌入式高速SATA接口主机控制系统研究与设计[D].北京:北京邮电大学,2011.

[3] 刘文国,李广军,林水生.基于FPGA的SATA硬盘加解密控制器设计[J].电子与封装,2009,9(6):25-28.

[4] 朱琛,崔镭,邵春伟,等.基于FPGA的高速光纤传输卡[J].电子与封装,2018,18(3):22-25.

[5] 范国浩,张艳兵,李新娥.基于FPGA抗高冲击机载雷达回波存储系统设计[J].电子技术应用,2016,42(4):78-80,84.

【通联编辑:李雅琪】