一种基于FPGA的低信噪比测距方法

2020-09-03施蕾

施蕾

摘 要:测距稳定性是影响激光测距仪性能的重要指标,信噪比是影响测距稳定性的重要因素。本文基于现场可编程门阵列(FPGA)提出一种低信噪比下的测距方法,可有效提高反射率低或远距离目标测距的稳定性。该方法在FPGA上集成冒泡排序、数据分析提取、取平均等模块,其中冒泡排序采用乒乓缓存比较的方法,数据分析提取通过分段、标识、反推方法实现。本文对1200米处建筑物进行测试,可实现小于±1m的测距波动。算法可实现低信噪比下距离的稳定测量,在强噪声或弱信号情况下均可得到较好稳定效果,可广泛用于激光测距。

关键词:低信噪比;测距;冒泡排序;数据分析提取;平均;现场可编程门阵列

1 引言

在激光测距应用中,低信噪比下微弱信号的检测是影响最远有效测程及测距稳定性的关键问题。造成信噪比低的原因,一方面目标返回信号本身就已特别微弱;另一方面由于强噪声干扰,比如背景噪声,使得信噪比降低。目前,基于TDC专用芯片和FPGA是实现高分辨率测距的主流研究方向。闫菲菲等人利用FPGA控制AMS公司的TDC-GPX2芯片,实现了一款4通道同时测量,测量精度达到60ps[1];张彬彬等采用两片时间-数字转换芯片TDC-GP2,将脉冲计数法和数字内插法相结合,使测量精确度能够达到1ns,分辨率可以达到100ps[2];王巍等利用Virtex-5中专用进位链CARRY4构造的延迟链,对时钟周期进行内插以得到更高精度的测量,精度约为25ps[3];雷琳君等采用数字计数法结合数字延迟线插入法的技术,时间分辨率为500ps,标准偏差小于270ps[4]。以上文献虽然都已经实现了较高的时间分辨率,但是都没有对低信噪比下测距的处理方法进行研究和说明。在实际测距应用中,低信噪比情况下,由于噪声的影响,鉴别出的回波stop数字信号的位置会出现较大抖动;噪声过大时,非目标位置也会出现stop,这样会导致测距结果有较大波动,甚至出现错误的值。现场可编程门阵列(FPGA)以其灵活可编程性、低延迟和低功耗等特性目前已成为电子系统的重要组成部分。本文基于Altera CycloneII系列FPGA,设计并实现了一种适合低信噪比情况下使用的测距算法,可有效提高测距稳定性,无需改动硬件,可直接应用于激光测距中。

2 算法原理

实际测距应用中,一般情况下,噪声是随机的,而信号的位置相对固定。所以,在低信噪比情况下,即使多次测距存在较大波动,但多数测距结果还是围绕在实际测距结果周围的,算法可以提取出这些有效数据,通过平均计算得到相对稳定的测距结果;即使出现测距结果大概率都是错误的情况,算法也可以进行分析处理,使当前测距结果无效。算法首先对N个距离结果进行从大到小的排序;然后按照允许最大偏差进行分段处理并对段内数据进行标记;对分段后数据分析得到最小有效距离;再根据最小有效距离反推并提取出接近实际距离的有效数据及个数,剔除掉偏离实际距离过大的数据;接下来判断有效数据个数是否大于阈值,若大于阈值则对挑选出来的有效数据进行平均运算,得到最终测距结果;如果有效数据个数不大于阈值,则测距结果无效。这里设置阈值,是防止信噪比过低时,噪声的个数可能大于信号的个数,如果阈值过低,则测距会出现错值。

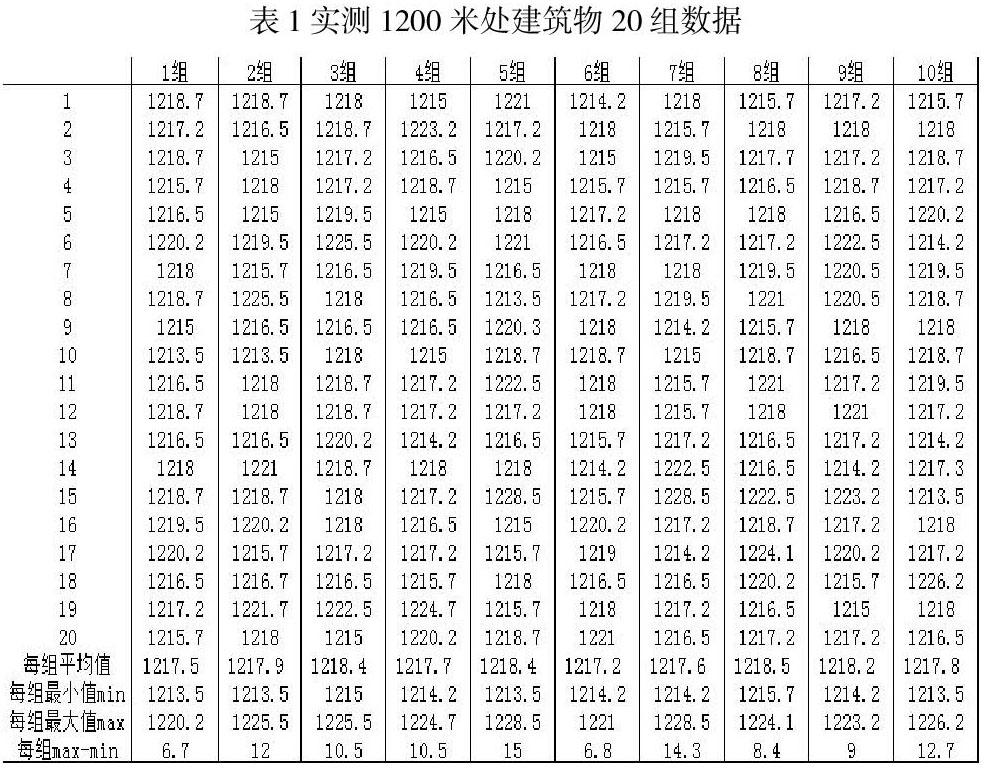

为了验证本文算法,对1200米处建筑物进行测试,共测试10组,每组测量20次。由表1看到,每组内数据波动较大,最大最小差值在15m;将20个数据取平均后,再比较10组的平均结果,最大1218.5m和最小1217.2m,差值仅为1.3米。由此可见,本算法可有效提高测距稳定性,减小距离波动。

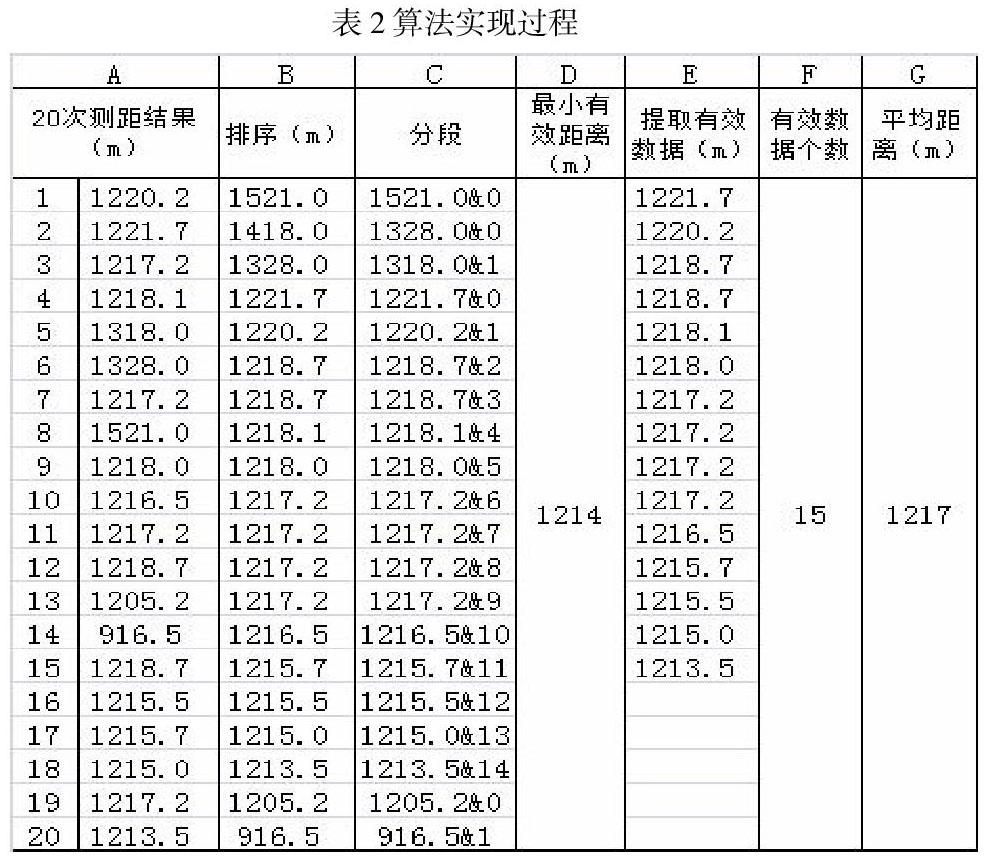

3 算法实现

本文选用Altera公司CycloneII系列的EP4CE22E22I7芯片来实现测距算法,基于QuartusII13.0平台进行开发,采用VHDL语言结合电路图输入法完成最终设计。外部输入时钟采用40MHz晶振,通过PLL得到200MHz时钟,供算法单元使用。下面结合表2阐述算法的实现。

冒泡排序是本算法的核心和基础,必须对N个随机且大小不等的结果进行排序,才能准确找到实际距离对应的有效数据。本部分实现表2中A列到B列的转换。如图2,该模块通过两个FIFO、两个最大值检测模块、FIFO1控制模块、排序数据输出模块完成排序功能。这部分重点在于冒泡排序的逻辑关系控制,包括数据、FIFO的读写信号、比较结束标志信号等。整体上看,FIFO1控制模块输出测距结果给FIFO1,FIFO1的输出给到最大值检测模块1,最大值检测模块1将最大值maxout1输出给排序数据输出模块,其余数据elsedata1传给FIFO2,完成一次最大值检测;同样,FIFO2的输出给到最大值检测模块2,再将最大值检测模块2的最大值maxout2输出给排序数据输出模块,其余数据elsedata2通过FIFO1控制模块传给FIFO1,如此反复,直到所有距离数据比较完成。

FIFO1控制模块负责输出数据和写信号给FIFO1。该模块有两个数据输入,一个是N次全部测距数据,一个是最大值检测2模块的输出elsedata2。该模块只在首次循环比较输出N次测距结果,同时输出FIFO1的写信号,其余循环全部选择输出elsedata2及相应的FIFO1写信号。FIFO1和FIFO2为缓存模块,虽然比较的数据不定长,但由于最大值为N,FIFO的深度可以取定值。本文N為20,FIFO深度均设置为32。

最大值检测模块,与FIFO配合,得到当前FIFO缓存中最大的数据,其余数据输出传给另一个FIFO,同时输出另一个FIFO的写信号以及比较结束标志信号。以最大值检测1模块为例,其需要输出读控制信号fiford1给FIFO1,当前读出的数据与上一个数据进行比较,若当前数据较大,则认为其为最大值(相等时本文算法仍认为当前数据为最大),将上一个数据输出给FIFO2;若当前数据较小,将上一个数据认为是最大值,将当前数据输出给FIFO2。这里需要注意,在输出数据给FIFO2的同时,要同时输出FIFO2的写控制信号fifowr2,保证数据能够有效缓存到FIFO2中。另外,最大值检测模块1还需输出数据比较结束标志信号maxend1,只要FIFO1的空标志信号empty1有效,则maxend1拉高,该标志信号提供给排序数据输出模块。

排序数据输出模块,负责将两个最大值检测模块的数据整合,由大到小顺序输出。数据整合的时序是依靠两个最大值检测模块的比较完成标志信号maxend判断的,只要maxend1或maxend2任意一个有效,则存储对应的数据。该模塊内部也是需要一个FIFO配合的,即maxend1或maxend2有效,则FIFO进行写操作,直至N个数据全部写完。

分段模块,对排序结果以允许最大偏差为依据进行分段处理,并对段内数据进行位置标记。本部分实现表2中B列到C列的转换。如图3为分段模块的流程图,dataout是分段输出,segbegin是当前段的首位数据,datain是FIFO当前输出,cnt为段位置。若接收到开始分段信号,则开始FIFO读操作,此时cnt、segbegin初始值全部为0,dataout为当前FIFO输出并上cnt;接下来判断empty信号是否为0,是则再读FIFO,读出的数据datain与segbegin做差,并判断差值是否小于最大偏差,是则将segbegin仍作为当前段段首,cnt加1,dataout为datain并上cnt;若差值小于最大偏差,则datain作为当前段段首,cnt为0,dataout为datain并上cnt。反复比较输出,直到FIFO为空,即empty为1。如表2,假设允许最大偏差为10m,B列中1521后面的数是1328,差值大于10,则分别为1段,所在段位置均为0;又如1221.7为当前段首位数据,与1220.2之差小于最大偏差,段位置分别为0和1;直到第19个数据1205.2,其与段首位数据1221.7差值大于最大偏差,则将1205.2归为下一段,段位置为0。

最小有效距离模块,就是将最大的段位置对应的数据找出来,如表2,C列中最大位置为14,对应的数据为1213.5,则D列最小有效距离为1213.5m。本文算法将cnt取8位,则比较时比较数据的低八位即可。

提取有效距离数据模块,根据最小有效距离数据,反推出冒泡排序后的有效数据并得到其个数。即所有数据依次与最小有效数据比较,若差值小于允许最大偏差,则将数据输出,否则剔除。本部分实现表2中B列到E列和F列的转换。如图4,为该模块实现流程图,data1s到data20s为20个数据的中间变量,data1到data20为输出的20个数据,cntout为有效数据个数。首先判断是否接收到开始提取信号,若收到,则判断empty是否为0,是则继续读FIFO,若FIFO输出当前数据datain大于最小有效距离,且差值小于允许最大偏差,则cnt加1,data20s到data1s移位1次,将datain赋值给data1s,这样能保证满足条件的datain循环移位输出;若datain不符合判断条件,则data20s到data1s保持不变。如此循环,直至empty为1,所有有效数据提取完成,最后将变量data1s到data20s的数据给到20个输出端,同时将cnt+1赋值给cntout。如表2,将B列数据与D中1213.5比较,B列中大于1213.5且差值小于最大偏差的,即为有效距离数据,见E列;F列为有效数据个数。

平均模块,首先判断个数是否大于阈值,是则认为本次测距有效,进行平均运算;否则认为本次测距无效。平均运算实现相对简单,本文利用FPGA内部的加法和除法IP核实现。本文阈值设置为10,如 F列中数据为15大于10,则本次测距有效。将E列中的15个数据取和,然后除以F列个数即可得到平均结果G列的数据。

4 测试结果及分析

基于本公司研制的激光测距仪,对本文算法程序进行验证测试。对1200米处建筑物目标进行测试,图5为示波器采集的激光器触发信号(1通道)和回波信号(2通道),延迟约为8us,上面为取样结果,下面为平均16次结果。由图5可看到,取样时基本无法辨别信号位置,而平均后信号位置则相对明显,进一步验证了平均算法的有效性。图6为改算法前后对1200米处建筑物的20次测距结果对比,可看到,改算法后距离波动由改算法前的约±7m减小到约±1m。

5 结论

基于现场可编程门阵列,设计并实现了提高低信噪比情况下测距稳定性的算法,可有效提高反射率低或远距离目标测距的稳定性。经测试,1200米处建筑物目标波动可控制在±1m。算法完全在一片FPGA上实现,可根据应用场合灵活增加或修改功能,促进测距单元的小型化,适合激光测距的应用。目前测距波动通过平均法可控制在±1m内,在以后的改进中可对算法进行优化,将波动进一步降低。

参考文献:

[1]闫菲菲, 马红皎, 何在民, 等.基于FPGA和TDC芯片的高精度时间间隔计数器研制.时间频率学报.2019,42(1):33~42.

[2]张彬彬, 崔永俊, 杨兵.基于TDC-GP2的高精度时间间隔测量系统设计.电子器件.2016,39(5): 1108~1112.

[3]王巍, 周浩, 熊拼搏, 等.一种基于FPGA进位链的时间数字转换器.微电子学.2016,46(6): 778~781.

[4]雷琳君, 杨燕, 陈卫标. 星载激光测距仪的高精度时间间隔测量单元. 中国激光. 2007, 34(10):1422~1426.

[5]范欢欢. 基于 FPGA 的时间数字转换电路的若干关键技术的研究[D]. 合肥:中国科学技术大学博士论文, 2015:14~18.

[6]黄海舰. 基于 FPGA 时间内插技术的TDC设计[D]. 武汉:华中师范大学物理科学与技术学院硕士论文, 2013:6~8.

[7]徐振. 基于TDC的时间间隔测量技术的研究[M].哈尔滨:哈尔滨工业大学.2008(1) :10~15.