一种高精度DAC芯片的设计

2020-03-21刘锡锋王津飞陆佳莉

刘锡锋,王津飞,陆佳莉

(江苏信息职业技术学院,江苏 无锡 214153)

0 引 言

数模转换器(Digital To Analog Converter),是一种将输入的数字信号转换成模拟信号输出的电路,通常被应用于数字信号的采集和处理,以及多媒体技术等领域中[1-2]。随着科技的发展,DAC越来越凸显其重要的应用意义。

1 DAC电路设计

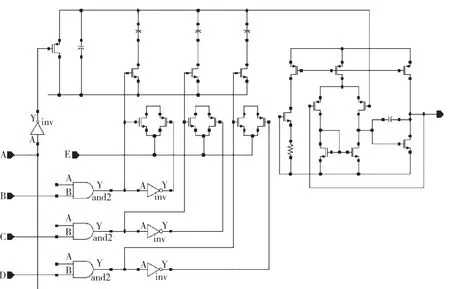

基于速度和功耗权衡考虑,本设计采用电容式DAC架构[3-4]。电容式DAC的优点是功耗低,速度较快;缺点是对于高精度应用场合,容易产生偏差。在本文设计中对精度要求不是很高,故采用该种结构设计能够充分利用其低功耗、高速的优点。电容式DAC主要是采用电容整列结构,开关根据输入8位数字信号从“00000000”至“11111111”之间进行改变,随着输入数字信号的改变,电容整列的电荷发生在分布,从而改变其模拟输出电压。图1为本文设计的电容式DAC总体结构图(由于图片大小关系此处仅显示3位)。

图1中的整体电路共分3个部分,首先是图的左上方为电容整列。考虑到工艺兼容性,在本设计中用MOS电容替代普通电容,好处是能够节约芯片面积。但考虑到MOS电容的特别性,这里要求MOS均采用NMOS,衬底接地。图的右上方是一个二级运算放大器,这里主要是通过它来对DAC输出结果进行电压跟随,电容式DAC本身不具备输出驱动能力,因此为了方便输出信号的使用,电压跟随器部分是必须要有的模块。图中左下方是复位电路和CMOS传输门开关,这部分能够通过数字开关控制电容整列复位,即置位“00000000”。通过CMOS传输门,控制电容整列的连接信号,达到改变电容阵列电荷分布的目的。

图1 电容式DAC电路图

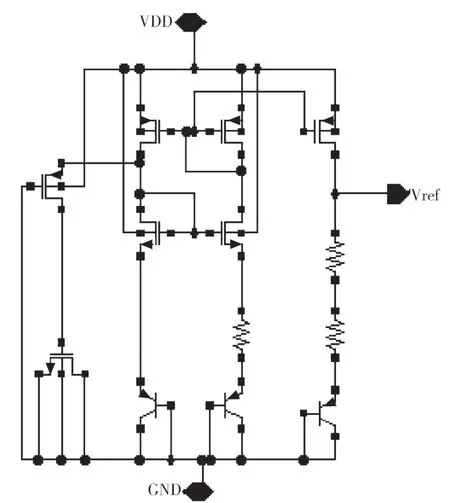

电容阵列式DAC除了需要电源电压和地电压外,还需要一个标准的参考电压,这个电压要求要能够输出非常稳定的电压值作为参考使用。在本设计中我们采用标准带隙基准来作为参考电压提供源。电路结构如图2所示。

该结构为一种普通带隙基准电路,能够提供1.2 V的稳定电压。

图2 本文所用的带隙基准电路结构图

2 信号仿真

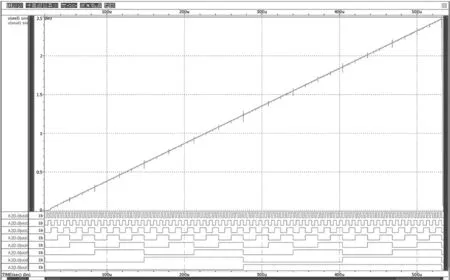

图3为该电容式DAC的总体仿真结果图。

图3 电容式DAC仿真结果图

仿真时间周期为520 μs,图3中下方为8位输入信号,在时间0时刻,输入信号从高位到低位均为0,到520 μs处走完一个周期,8位输入信号均为1。即从“00000000”逐次增加到“11111111”,增量步长为1,共256步。图3中上方斜线为DAC输出电压值。从图3中可以明显看到,随着输入8位信号的逐步增加,输出信号呈现明细那逐步上升态势,且线性度良好,斜率稳定。

根据实际数据与理想曲线非线性误差,可得微分非线性公式(DNL)有:

其中,x(q)为输入信号码的实际台阶高度,对于每个输入信号,DNL都有:

而微分非线性误差积分总量即积分非线性INL公

式如下:

且有:

此外,DAC还具备静态误差和分辨率,其最小值为1LSB。动态特性反映了DAC对于数字输入信号的响应速度快慢。

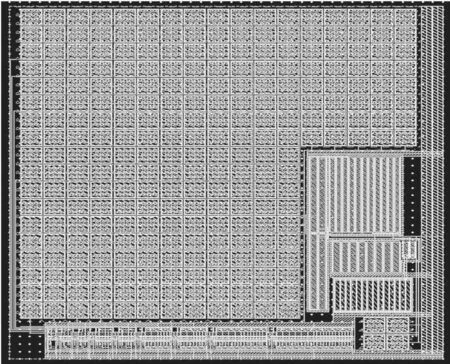

3 版图设计

完成了电路设计并通过仿真确认设计正常之后,还需要将所设计的电路转化为版图才能用于集成电路生产。图4为根据本文所设计DAC电路绘制的版图[5-6]。

图4 电容式DAC版图

4 结 论

芯片版图完成后,经过流片测试。结果表明,该DAC芯片能够实现8位二进制数字信号的转化[7],即将内部1.2 V基准电压按256等分均匀输出各阶电压,具备较高采样速度,且功耗较低,达到设计要求。