基于FPGA的信号采集系统的设计

2020-02-21吉强

摘要:本文提出了由现场可编程门阵列( FPGA)、高速数模转换器和USB接口组成的通用信号采集系统设计方案。设计了以FPGA为核心部件的信号采集系统,实现数据的实时采集、存储。它的优点是摆脱了软件驱动控制,信号的采集传输采用全硬件的操作方式,使系统更加稳定、高效,USB接口作为数据传输的接口,保证了数据的高速稳定传输。

关键词:数据采集;FPGA;信号采集

1 系统总体结构

本文提出的信号采集系统主要是利用FPGA芯片控制模数转换芯片对目标模拟信号进行采样,将模拟信号转换数字信号后,写入到USB接口芯片中将数据传输到PC中,利用软件编写人机交互界面,将信号数据进行存储。信号采集模块的设计功能是实现信号采集与分析,通过ADC进行模数转换,实现数据采集和采样数据的存储。如图1所示。

2 信号模块方案分析

2.1 信号采集模块方案分析

信号采集模块是计算机与外界连接的桥梁,也称信号获取模块。主要完成对目标模拟信号采集,并将之转换成数字信号进行存储。该模块的主要任务是实现模拟信号的数字采集,即进行模数转换,以便进行信号的处理,本设计采用模数转换芯片(ADC)来实现。目前,主流信号采集系统大多采用MCU或者DSP作为核心部件来进行信号转换,存储器和其他外围电路来完成数据采集。但是,不论是单片机还是DSP都有缺点:单片机虽然指令丰富,编程简单,灵活的控制方式,但运行速度慢,稳定性较差,抗干扰能力较低,极大地限制了ADC的采样速度,对于目前强调高速信号处理的今天已经不太适用了。而DSP芯片虽然处理速度较快,但DSP芯片的通用输入输出接口较少,功耗较大,并且对外围设备的控制能力较弱。相反,FPGA(可编程逻辑器件)具有MCU和DSP所无法比拟的优势,它硬件采用并行机制,在性能和处理速度上优势明显,并且编程简单,设计灵活,时钟频率高,抗干扰能力强,稳定性好的优点。特定的逻辑功能由用户通过硬件描述语言(HDL)实现,设计灵活,功能可以更改。此外,FPGA还有大量可编程逻辑的片上系统,主要包括PLL(锁相环)模块和存储单元,可为总线、模块产生时钟。因此,FPGA的这些处理速度快和存储特性使其非常适合用作ADC的控制设备,以实现高速信号采集和存储控制。本文以FPGA为核心控制器,设计了数据采集系统,控制ADC对数据采样,并将采样后的数据存储到SRAM存储器中,以实现数据采集和存储的功能。

2.2 数据处理模块方案分析

在数字信号处理方面,目前有四种实现方法,主要包括使用数字信号处理软件、芯片、单片机、FPGA等。

(1)使用常用的数字信号处理软件是matlab、LabVIEW等软件编写数字信号处理软件来实现数字信号处理。它的缺点是处理速度受计算机CPU处理状态的影响,系统体积大,成本高。因其通用性和可移植性好,数据接口类型丰富,主要适用于教学和科研。

(2)采用特殊的数字信号处理芯片(DSP)。这种芯片一般厂家通过内部硬件电路设计实现特定功能的数字信号处理功能,具有继承性好,运算速度快的优点,但又具有功能较单一,价格较高,应用不灵活的缺点。常见类型的芯片专门用于FFT,卷积,各种数字滤波和其他相关算法。通常用于对加工有较高要求的应用中。

(3)采用MCU进行数字信号处理,单片机虽然编写程序简单,容易开发,但是,其处理速度较慢,稳定性也较差,只能实现一些简单的、对精度要求不高的数字信号处理,对于较复杂信号不能采用单片机。

(4)采用通用的FPGA處理芯片。由于目前FPGA在性能和处理速度上的优势,FPGA在DSP领域应用越来越广泛。这种FPGA处理芯片的特点是采用并行机制;芯片内部有专用的硬件乘法器,可以实现快速信号处理,能够完成复杂的DSP任务。

与前三种实现方式相比,FPGA芯片结构由于采用并行机制,在性能和处理速度上优势明显,并且编程简单,设计灵活,抗干扰能力强,稳定性好的优点,非常适合高速数字信号处理。在工作的第一阶段,采样数据通过FPGA接口传输到PC平台,以实现数字信号处理。在第二阶段,以通用的FPGA芯片作为核心控制器来设计数据处理模块,并设计FPGA软件来完成数字信号处理功能。

3 高速数据存储技术的实现

一般存储芯片数据接收速度快,但无法实现系统显示模块,USB传输模块和数据处理模块的处理速度。因此,必须实现实时高速的数据存储。美光公司的mt29f256908aucabh3的NAND闪存芯片被选为系统的存储芯片。该芯片具有两个工作状态:同步和异步。该芯片采用单层存储架构的SLC,因此在同步工作状态下,数据引脚可以通过DDR模式进行读取,并且该引脚的最大读写速度可以达到200MT/s,即同时上升可以写入时钟的上升沿和下降沿。

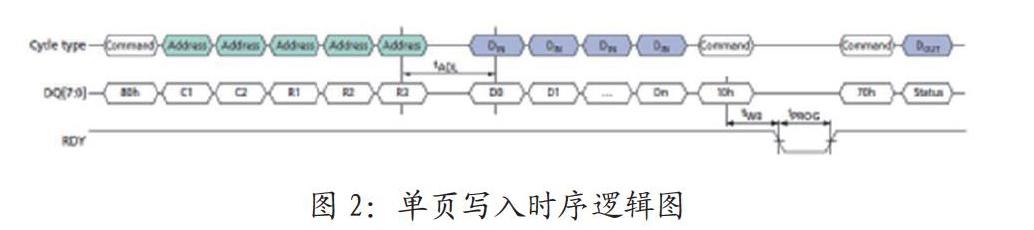

芯片的总存储容量为32GB,每个芯片分为四个目标,每个目标包含两个逻辑单元(Lun)。NAND闪存以Lun单位工作,即每个NAND闪存可以独立完成读取,写入和擦除操作。如果插销允许,多个Lun可以同时工作。每个Lun包含两个平面,每个平面包含2048个块(每个块中256页)。每页包含(8K+ 448)字节,其中8Kbytes是数据存储空间,而448bytes是地址空间。根据对NAND闪存芯片数据手册的分析,在NAND闪存芯片中用于程序页面的时间包括数据加载时间,地址信息加载时间,状态切换时间和页面编程时间。根据产品手册提供的产品电气规格,地址信息的加载时间和R/B状态切换时间均为lOOns,页面编程时间为3505。在同步状态下,NAND闪存芯片需要大约40.96s的时间才能完成。接收8KB数据。可以看出,NAND闪存存储1页数据大约需要400 s,而存储72mb数据需要3.7 s,这不能满足系统的高采样率。如图2所示。

综上所述,系统设计中选用的NAND闪存芯片不能满足正常工作状态下高速数据存储的要求。因此,提出了一种基于NAND闪存芯片和FPGA的高速数据存储方法。根据芯片的存储结构特性,当Lun处于程序页面状态时,尽管Lun的状态显示为忙,但写操作所占用的芯片引脚将被释放(不包括芯片选择引脚和状态)。当芯片中的任何Lun处于编程状态时,其余七个可以写入数据。结合芯片的特点,本文提出使用芯片来写流水线数据。芯片中的八个逻辑单元按顺序排列,并且数据依次写入一页,这减少了等待程序页面状态的时间。当收集的数据达到8K时,处于写就绪状态的Lun开始以DDR模式写入数据。写入数据(8K)之后,下一个Lun准备就绪,并等待联合国存储的数据再次达到8K。这样,当第八个Lun完成写操作时,第一个Lun完成编程过程,并且处于用于写操作的空闲状态。根据NAND闪存逻辑控制程序的时序分析,NAND闪存写入数据页的时间(8K>减少为81.92 US)。设计了一种高速数据存储技术,其存储速率可以达到100 MB,以满足系统要求,实现对收集数据的实时存储。

4 信号采集流程

系统信号采集模块可分为两部分:采集开始和信号视图。操作员可以通过人机交互模块中的LCD触摸屏输入命令来触发相应的功能。通过单击人机交互模块中的“开始获取”按钮,将触发信号获取程序。软核处理器接收人机交互模块的信号采集开始指令,系统进入信号采集过程。

步骤1:初始化A/D转换模块和高速存储模块,以激活最后一批结束的伦的下一个伦的存储状态;

步骤2:软核处理器将芯片选择信号和使能信号发送给相关的定制 IP核,并同时输出somhz时钟信号给模数转换芯片;

步骤3:模数转换模块开始工作,ADC芯片负责将输出的12位数字信号输入到逻辑控制模块。

步骤4:逻辑控制模块对接收到的12位数字信号进行简单编码和处理,然后将当前采集批处理的左移四位和四位二进制值相加,以形成16位数字信号,并将其存储在数据中临时存储FIFO。数据存储FIFO输入信号的位宽设置为16位,信号输入频率设置为smohz;输出信号位宽设置为8位,输出信号频率为200MHz;深度是4096个单词

步骤5:当临时存储FIFO存储已满时,逻辑控制模块将向数据存储模块发出指令要求写入数据,并向临时存储FIFO发送指令要求读取存储的数据。系统开始以直接内存访问模式将数据从FIFO发送到DDR IP内核,并且数据通过DDR IP内核发送到数据存储模块。

步骤6:进入到写入页面数据环节,先入先出队列读取使能将被控制模块关闭。数据存储模块将激活下一个Lun的存储状态,再重复进行步骤5至步骤6。

波形显示流程:波形显示流程图如图3所示。

步骤1:处理器从系统配置存储芯片中获得查看信号的存储地址。

步骤2:将信号存储地址发送給数据存储模块,处理器读取数据存储模块对应地址的数据。

步骤3:处理器量化数据以满足LCD显示要求。

步骤4:将波形控制模块中的数据输入人机交互模块中的存储芯片。

步骤5:初始化波形控制IP核,并在显示屏上建立波形显示窗口。要输出的数据从DDR2锁定到双端口RAM。波形控制IP内核负责输出波形点显示坐标位置和波形显示时钟频率。

步骤6:读取对应批次的所有数据后,波形显示过程结束。

5 总结

基于FPGA器件的结构特点,开发了通用信号采集系统。信号采集与存储系统是通过FPGA技术实现的。设计了基于FPGA和NAND闪存芯片的高速存储解决方案,解决了高速信号实时存储的问题。测试了采集功能,系统运行良好,有效提高了信号采集和处理效率。

参考文献

[1]陈腾飞.地震数据采集模块通用测试系统的研究与设计[D].中国科学技术大学,2019.

[2]金真平.基于FPGA的电路板多功能测试仪设计与开发[D].南昌航空大学,2018.

[3]温建飞,基于FPGA和USB3.O的超高速数据采集系统设计[D].中北大学,2016.

[4]陈亚斐.基于DSP和FPGA的电力电子数字控制平台的研究[D].青岛科技大学,2016.

[5]关守平,尤富强,董国伟.基于FPGA的高速数据采集系统设计[J].控制工程,201 3.20 (5):970-975.

作者简介

吉强,山东省临沂市人。研究生学历,讲师,目前在江苏安全技术职业学院从事教学工作。