一种基于IP的集中检查器自动产生方法

2020-02-21毛佩瑶周建

毛佩瑶 周建

摘要:本文介绍了系统芯片开发中一种基于IP的集中检查器自动产生方法和具体实现流程。片上系统(SoC-System On Chip)是一种高性能、低功耗、低成本的芯片设计方法。而为了提升了产品的竞争力,各类丰富的IP (Intellec tual property)都被集成到SoC中,这给验证工作带来了巨大挑战。笔者从实际验证工作出发,使用该方法简化了验证工作,提高了工作的质量和效率。

关键词:检查器产生;IP;混合信号;

1 引言

为了使系统芯片有更高的性价比,不仅越来越多的数字和模拟IP被集成到单个芯片中,而且现有的芯片中也定义了越来越多的功能操作模式,除了运行模式,还有许多低功耗模式,时钟模式,测试模式等[1]。

检查器( checker)是验证平台中一个负责进行数据对比和报告的组件,是芯片的验证工作必不可少的一部分。因此,在芯片集成的模块越来越多,设计的工作模式越来越复杂的情况下,验证工程师必须花费大量的时间来研究IP的功能以及一些关键接口信号,以保证能开发出正确的检查器来进行系统级验证。

2 问题

在实际SoC开发项目中,因为一些关键IP的检查器构建错误或者因为疏忽而遗漏某些测试点,就会导致芯片产生一些缺陷。以下是笔者在实际SOC项目开发过程中遇到过的几类问题,这些问题都会导致芯片开发延期。

(1)验证工程师必须创建一些检查器去检查当芯片在某种功能模式下运行时,IP是否处于正确的工作状态。但验证工程师却很困难去获取哪些信号需要保持在何种状态。

(2)因为SoC定义的各种功能模式繁杂,且因SoC的定义不同而不同,因此IP设计师很难知道自己设计的IP需要工作在哪些功能模式,也很难给SoC提供相应的指导和帮助。

(3)有的IP内嵌了一些检查器以检查关键的功能,但是在SoC中这些检查器并不容易被配置到不同的功能模式。这些内嵌的检查器可能使用了嵌入的PLI( Programming Language Interface),特定的功能语言等,这也会造成SoC无法直接使用。

(4) 一些模拟信号的检查依赖于仿真工具,因此也很难实现通用的检查器。

(5)因为检查器分散在不同部分,所以很难产生一个直观并且集中的覆盖率报告,也很难知道哪些检查器还没有被覆盖到。

(6)不同的SoC验证工程师和DFT工程师可能花费了大量时间去构建几乎相同的检查器,并且执行了大量的仿真,开发效率非常低,并且检查器的质量和重用性也无法保证。3集中检查器自动产生方法

为了解决上面所述的问题,笔者开发了一种集中检查器自动产生方法。用这种自动化方法产生的检查器可以被不同的工程师灵活的应用在SoC验证环境中。这种方法也提高了检查器的重用性和质量。这种检查器自动产生方法主要分为以下几个步骤。

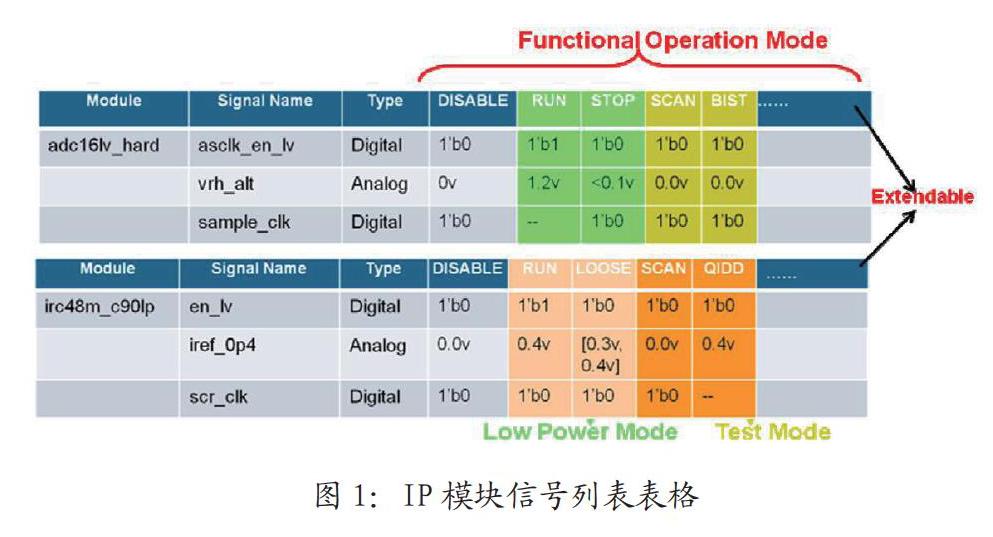

3.1 在IP数据库中构建信号列表

首先针对IP核构建信号列表,包括信号名字、信号类型以及信号在不同功能模式下的预期值。为了降低维护成本,提高重用性,信号列表应按照统一的格式(如.xml,.xls等)构造,并存放于IP数据库中。

在图1中IP模块设计师定义了一些信号和功能模式。因为IP模块设计师很清楚自己所设计的模块的关键信号的预期值与功能模式之间的关系,所以图中表格的内容质量要明显高于SoC验证工程师构建的检查器。

除此之外,IP模块设计师很容易对图1中的关键信号和功能模式进行扩展以满足不断增强的模块功能。并且因为信号列表被存放于IP数据库中,这保证了信号列表的正确性和一致性,很容易被SoC使用。

3.2建立IP功能模式与SoC功能模式映射关系

通常SoC会在用户手册中定义多种多样的功能操作模式,而不同的IP模块会工作在不同的SoC功能模式中。所以我们需要建立IP功能模式与SoC功能模式映射关系。

图2是某SoC功能模式与IP功能模式映射表。adc16lv hardSTOP模式被映射到SoC的LLS模式,irc40m_c90lp模式被映射到SoC的LOOSE模式。也就是说,当芯片进入LLS模式时,adc16lv hard会工作在STOP模式,irc48m_c90lp会工作在LOOSE模式。

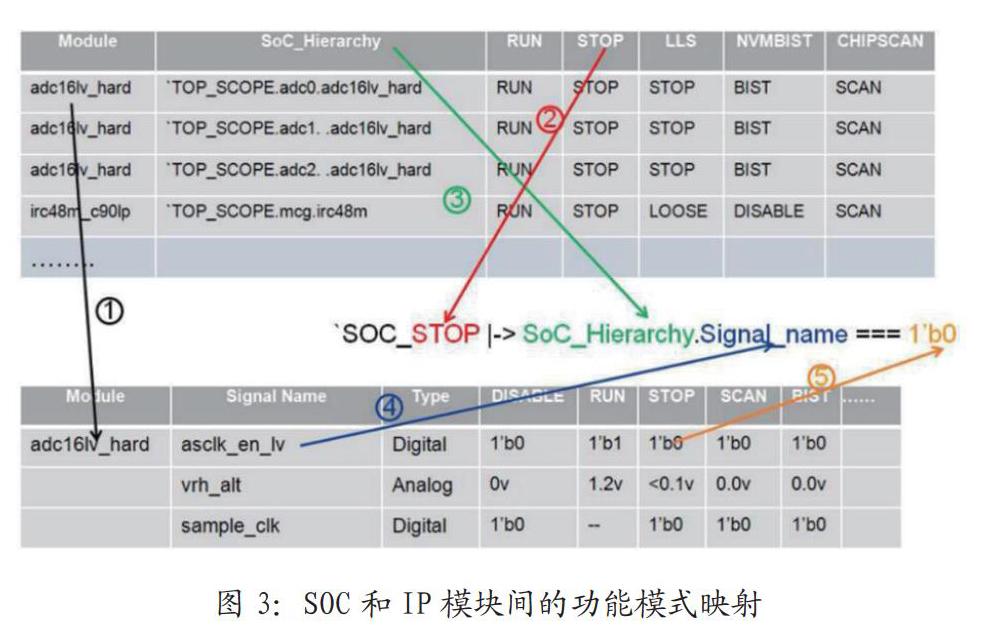

3.3产生统一的SoC级的检查器

IP数据库中的信号列表能够被SoC功能模式抽取,并自动产生检查器。笔者在最近的项目开中采用了该方法。图3给出了详细的产生原理及步骤。

(1)根据SoC映射表中的Module名字从adc16lv hard模块的数据库中抽取到信号列表。

(2)根据SoC的不同功能模式定义产生检查器中的条件。例如,'SOC.power mode control.stop__mode被STOP模式使用,SOC.test control.chip_scan mode被CHIPSCAN模式使用。

(3)从IP模块信号列表中抽取信号名字和预期值,并产生检查器。3.4执行仿真并产生覆盖率报告

该方法產生的检查器是在SoC级实现的,验证工程师通过SystemVerilog断言来实现那些检查器[2]。这样使用仿真工具就能很容易产生覆盖率报告。根据覆盖率报告,我们能知道每个检查器是否被覆盖到了,就能够比较容易地抓到设计中的缺陷。

3.5 检查器产生流程

图4给出了该方法的完整流程。

4 实验结果

我们使用Perl脚本实现了本文所介绍的检查器自动产生方法,并且在最近进行的芯片设计工程中成功使用了该方法。下面摘取了部分产生出来的检查器内容。

//-adc0-

a adco adc16lv hard asclk_ en lv

assert property (@(posedge 'TESTMODE CHECKER SVACLK) disable iff(testmode_checkerdisable)

、L2KSSTOP l~>(、TOP SCOPE.adcO.adc16lv hard.asclk_ en lv一一1'b0));

voltage_range_check

adco adc16lv hard vrh_alt(、L2KS STOP.、TOP SCOPE.adc0.adc 16lv hard.vrh_alt, O.Ov); //analog voltage checker

a adco adc16lv hard sample_clk:

assert property (@(posedge 'TESTMODE CHECKER SVACLK) disable iff(testmode_checkerdisable)

、L2KSSTOP l—>(、TOP_ SCOPE.adcO.adc16lv hard.sampleclk一一1'b0));

5 结论及展望

本文介绍了一种基于IP模块的系统芯片中检查器的自动产生方法。该方法基于SoC定义的功能模式与IP模块定义的功能模式映射,抽取IP模块的关键信号列表,从而自动产生检查器。这种检查器能够被不同的SOC开发工程师使用。IP的重用性与自动产生的检查器提高了SoC产品质量和开发效率,而产生的覆盖率报告也进一步提高了SoC芯片开发质量。

参考文献

[1]王永生.系统级芯片(SoC)可测试性结构及其优化的研究[D].哈尔滨工业大学,2006.

[2] IEEE Std 18001M-2012: SystemVerilog - Unified HardwareDesign, Specification, and Verification Language,Dec.5.2012.

作者简介

毛佩瑶(1995一),女,四川省成都市人。电子科技大学硕士研究生在讀,在读期间实习于恩智浦半导体。研究方向为数字IC设计与验证。

周建(1981-),男,湖北省京山县人。硕士学位,高级工程师,恩智浦半导体(中国)有限公司苏州分公司资深集成电路设计工程师。主要从事计算机体系结构、微控制器系统芯片设计及验证等研究。