基于FPGA的查表式运算器的设计

2020-02-02金天星闵啸

金天星 闵啸

(中国船舶重工集团公司第七二三研究所 江苏省扬州市 225011)

电子计算器已经变成现代人生活中不可缺少的工具,给人们的工作和生活带来诸多便利。随着人们对计算功能的要求越来越高,各种新型的技术也逐渐运用到计算器运算领域,当前,基于FPGA的运算系统应用较为广泛,在传统的运算技术上进行了优化,其计算时间更快,并且能处理更大量级的运算,它不仅给人们带来了很大的便利,还为现代人提供了更迅捷的计算速度,具有非常强大的运算功能。

1 计算器运算系统的总体设计

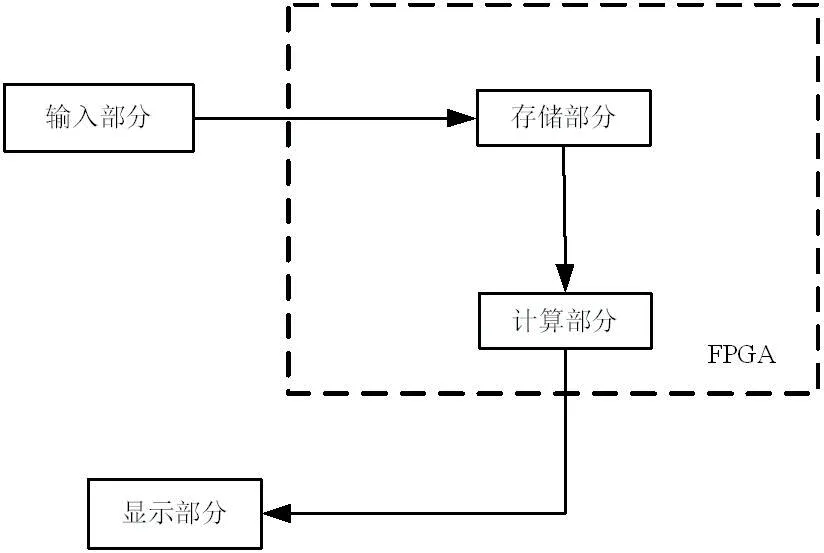

系统总体设计框图如图1所示。此设计由计算部分、存储部分、显示部分和输入部分组成。

1.1 计算器的计算部分

首先,该系统计算部分所采用是8 位或4 位二进制的计算方式,这也是目前应用较为广泛的一种计算方式,其计算语言为VHDl 语言,通过VHDl 语言中的运算符就能将各个数字之间的运算衔接起来。然而,在计算器的显示过程中,百位、十位、个位等必须都是分开显示的,这就需要用到比较的方法去实现。当然,采用VHDl语言进行计算时只能处理以2 位除数的幂的除法,而不能处理除数是其它数字的运算,此时就要求另外设计一个除法器来完成除法运算,这个除法器所采用的是左移运算和减法运算等程序。

1.2 计算器的存储部分

我们都知道计算器的存储部分是非常的重要的,它主要有三个存储器去实现它的计算的功能,包括:结果暂存器(ans)、输入寄存器(reg)和内部累加器(acc)等。通常,将输在存放在输入寄存器或内部累加器中,第一次按下数字按键就能直接显示个位,第二次按下数字按键时就表示此时输入的是个位,而上一次输入的十位,因此,第一次输入的数字就必须乘以10,并与第二次输入的数字进行相加,得到的就是计算结果。同理,第三次按下数字按键时,就要将第一次输入的数字要乘以100,并与第二次输入的数字乘以10 以及第一次输入的数字进行相加,得到最后的计算结果。

1.3 计算器的显示部分

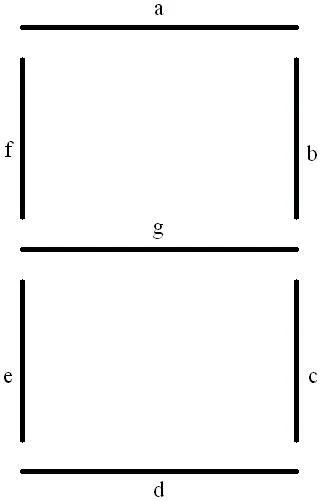

我们都知道计算出来的结果,一定要显示在屏幕上,我们用的屏幕是Fede 的屏幕,这种屏幕功能是非常的强大的,能够更好的显示图形和数字符号。该运算系统采用的是二进制运算方式,用BCD 码来诠释输出表达方式,因此,可以在FPGA 中运用译码程序来实现。该系统选用共阳极七段译码管,当需要显示数字时对应的管脚将切换到低电平,在输出的过程中,按照从左到右、从高到低的顺序,依次为g、f、e、d、c、b、a,其结构图如图2。

通过查阅大量的数据我们编写出相关的代码,并且能够更好的去实现功能。为了设计出计算器中的显示功能,所采用的的七段译码器,同时运用3 个七段译码器,依次显示出百位、十位、个位。当把第1 个数字输进去后,在按下第2 个数字之前,此时三个七段译码器都直接将第1 个数字显示出来。当输入完第2 个数字后,则会直接将第2 个数字显示出,然后,在按下第3 个数字之前,直接将前面两个数字的运算结果显示出来,以此类推,最后按下等号键,其最终的运算结果就快速显示。

图1:计算器的系统组成框图

图2:七段译码器的结构

1.4 计算器的输入部分

在生活中接触计算器的次数较多,都知道计算器上的数字的一般都是都是10 个数字,通过这十个数字不断的加减乘除,都可以计算出想要的结果,并显示到计算器的显示屏上。

在这次设计中,程序是非常的重要的,而设计科学的、合理的按键译码电路是计算器输入部分的关键流程。其中,计算器的输入部分包括0-9 等10 个数字符号、加减乘除等4 个运算符号、1 个清零键、1 个等号键等。因此,就要求对每个按键进行不同译码,保证按键数字的准确性。

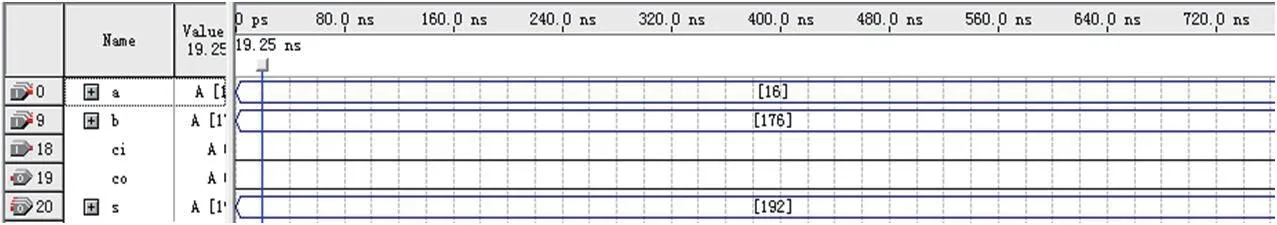

图3:加法器仿真16+176=192

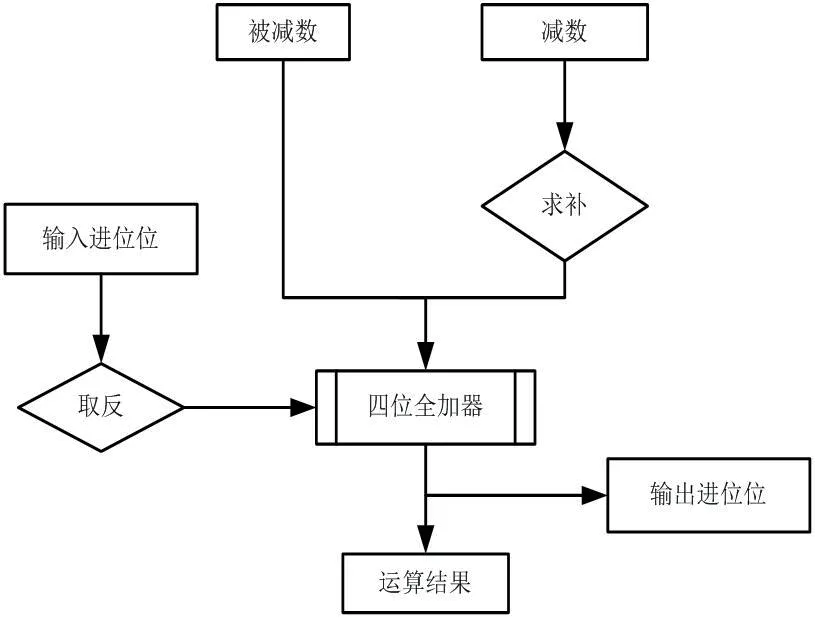

图4:四位全减器的原理框图

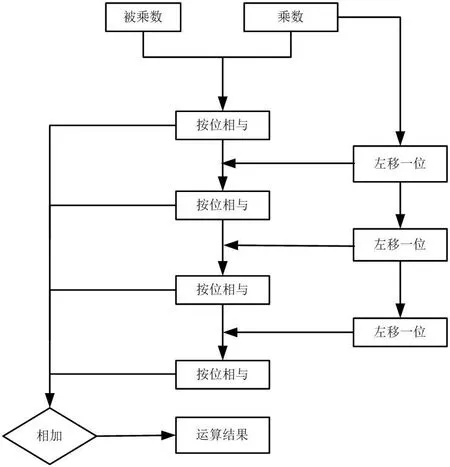

图5:乘法器的原理框图

2 计算器的VHDL设计

2.1 加法器的设计

本文设计的加法器运算程序是多位加法器,能够根据不同的进位方式划分成两种类型,即并行进位加法器和串行进位加法器。其中,串行进位加法器运行原理为把多个一位全加器级联,低位全加器的进位输出送给相邻高位全加器作为进位输入。显而易见,该设计方式所需要的资源更少,并且思路非常简明,然而运算的速度并不快。并行进位方式的运行原理为基于各位的加法程序的基础上,添加进位发生的逻辑电路,各位的进位输入信号都是同时出现,这就可以保证各位能一起进行全加加算,并显示出计算结果。这种运算方式需要的资源较多,运算速度是非常快的。特别在处理运算位数增加的过程中,相比于串行进位加法器,并行进位加法器占用的资源更大。所以,在设计加法器时,必要要全面对比资源占用量和运算速度,尽可能地实现设计平衡。根据相关资料可知,在采用4位二进制的方式进行运算时,二者资源占用量基本一致。所以,就能够将两个4 位二进制并行加法器级联从而从此一个8 位二进制加法器。

接下来,需要去详细的分析这个程序的运行过程,并通过仿真评定其准确性和合理性。加数和被加数进行相加,并且个位和十位、百位都是相对应的,相加之后进行四舍五入的方法总结出来的结果,并且把结果显示到屏幕上去,这样更加的直观而和真实的地了解加法的计算结果。如图3所示,能够更好的让我们分析十六进制和八进制的区别,能轻易分辨出二者是如何进行运算的,通过这种形式能够让我们通过仿真的方式进行分析和验证,最重要的是可以得出正确的仿真结果,也就表明设计出的加法运算器非常的成功。

2.2 减法器的设计

上文我们已经介绍了加法的运算器的运行的原理。接下来我们就介绍减法的运算器的原理,其实加法的运算器的原理和减法运算器的原理都是相通的,它们都是一样的,都是通过数字与数字进行相减,个位和个位相减、十位和十位相减、千位和千位相减,直接将运算的结果显示出来,具体的流程图、原理图,如图4所示。

2.3 乘法器的设计

乘法的运算器是非常难以解决的,所需要的步骤也是非常多的,通过移位的方式去实现相关的运算。在数字系统中,乘法器属于基本的逻辑器件,并且在应用过程中会发生不同类型的滤波器的设计、矩阵的运算等。本文所设计的乘法器程序是4×4,最终得出了乘法运算器的原理的框图如5 所示。

2.4 除法器的设计与仿真

除法运算器实在移位和连减的基础上完成的,而连减实际上也是基于数学上除法的基本原理。由于运算方式采用的是二进制,就能够进行移位操作。该计算器所采用的除法器运用了一个可以控制移位的控制器,再加上由全加器组成的4 位减法器。当做完减法,需要再次判断是否够减,也就是判断有没有发生错位,如果不够减,需要将被减数进行恢复,移一位再减。

3 总结

本次研究是采用FPGA(现场可编程逻辑器件)来设计查表式运算器的,所采用的的语言包括VHDL,并进行编程程序,最后也运用Quartus Ⅱ软件进行仿真。虽然运算器的功能不强,只是简单的运算功能,但采用诸多编程技术,经过经过外接键盘输入、LED数码显示来达到和完成运算目标。