基于FPGA的高速PCI-E的数据传输设计与实现

2019-12-24吴国华杨自恒郭俊磊徐勤涛

吴国华,杨自恒,郭俊磊,徐勤涛

( 黑龙江大学 电子工程学院,黑龙江 哈尔滨 150080)

0 引言

随着现代通信对传输带宽的要求正逐步提高,此前普遍采用的PCI总线已经无法满足高速数据传输的要求,正面临淘汰。为解决这种处境,PCI-E作为第三代互联总线技术应运而生,它支持芯片间和设备间的点到点串行连接,并以低开销、低延迟等特性大大提高了总线的有效数据带宽[1]。又因为PCI-E总线高效传输的性能和低廉的成本,让其获得了广阔的应用,解决了高性能处理器与低效传输系统之间存在的问题,在高速数据传输与存储系统中,通过PCI-E总线进行数据的DMA方式传输,可完成设备间的高速数据交换。

文献[2]使用传统的状态机设计PCI-E接口,结构复杂,容易丢包错包。文献[3]使用Block DMA的方式发送数据,但不能使用连续地址块发送数据,必须要多次打包数据再发送,这就限制了DMA的性能。文献[4]虽然使用最新的ZYNQ芯片进行开发,但使用的是PIO模式,占用大量CPU,传输效率低下。而如今,由于全球集成电路的快速发展,嵌入式技术和芯片的设计方式正经历着突破性的改革,基于片上系统(System-On-a-Chip,SOC)的开发平台将成为未来嵌入式系统设计的趋势,SOC主要的设计方法是通过在FPGA的开发板上调用处理器的IP核或使用芯片内嵌入的硬核得到可编程平台,进行处理器与FPGA的联合开发。Xilinx公司顺应时代发展的趋势,开发出的最新的ZYNQ芯片就是新一代SOC设计的优秀产品,将FPGA 结构和ARM处理器设计在一块芯片里,实现了软硬件间的协同设计,提供了基于IP 核设计的嵌入式方法。本文是基于 ZYNQ的SOC设计平台下的PCI Express 接口设计方案,使用SG-DMA方式传输,这将极大增强高速数据传输的效率以及系统实现方案的集成性和可扩展性[5]。

1 ZYNQ-7000 SOC的功能

ZYNQ-7000系列基于Xilinx全可编程的可扩展处理平台结构,该结构在单芯片内集成了基于ARM公司的双核ARM CortexTM-A9多核处理器的处理系统PS(Processing System)部分和基于Xilinx可编程逻辑资源的可编程逻辑系统(Programmable Logic,PL)部分[6]。

与传统的FPGA和SOC相比,ZYNQ-7000全可编程SOC包含了完整的RAM处理子系统,不仅提供了FPGA的灵活性和可扩展性,同时提供了与专用集成电路相关的性能、功耗和易用性,双核ARM CortexTM-A9多核CPU是PS的心脏,包括片上存储器、外部存储器接口和丰富功能的外设。因此ZYNQ-7000系列芯片具有强大的可扩展性和配置性,成为本设计要求高性能、高效率方案的首选。

2 硬件总体方案设计

2.1 总体设计原理

首先PC_1机发送端利用基于VS2015开发的PCI-E应用程序将要传输的数据进行打包,此数据经过开发板上PCI-E X4的物理接口进入到FPGA中,这一传输过程是PC_1机通过PCI-E总线的物理接口对DMA控制器发送写入数据请求,从而将要传输的数据存放至TLP包上发送至板卡。

FPGA端的DMA控制器接收并处理来自上位机的含有数据的TLP包,经控制器的拆包处理,获得此数据包中的地址和数据等重要信息,并发送数据的有效信号给控制器,控制器把数据暂存在AXI_DATA_FIFO进行跨时钟的缓冲,当收到数据信号后,PS端通过C语言编写的逻辑程序通过AXI_GP接口和AXI_LITE总线控制AXI_DMA 的IP核以DMA的方式由PS端的Slave AXI HP接口把数据从缓冲区取出并高速传输至PS端的DDR3中,当PL端传输完一组数据后,PS端接收到AXI_DMA的中断信号后,将DDR3缓存的数据基于TCP协议以乒乓操作的方式通过PS端的千兆网口发送至PC_2接收机的网口应用程序中显示。总体方案的系统框图如图1所示。

2.2 FPGA(PL)端设计

经过查找资料并研究分析,现有程序中申请的内存一定要物理连续。DMA是直接对物理内存也就是实际的内存条进行读写操作,必须为物理连续的内存;而应用程序和驱动程序一般只能申请到逻辑上连续的内存,在物理上不一定连续,所以DMA传输要分成多次完成,在传输完一块物理上连续的数据后引起一次中断,然后再由主机进行下一块物理上连续的数据传输,在有的论文中可以看到申请内存上的一些特殊处理,目的就是获取物理连续的内存,可获取4 KB的物理连续内存。但是在内存处理上还是存在一些问题,实验尚可,应用则不行。

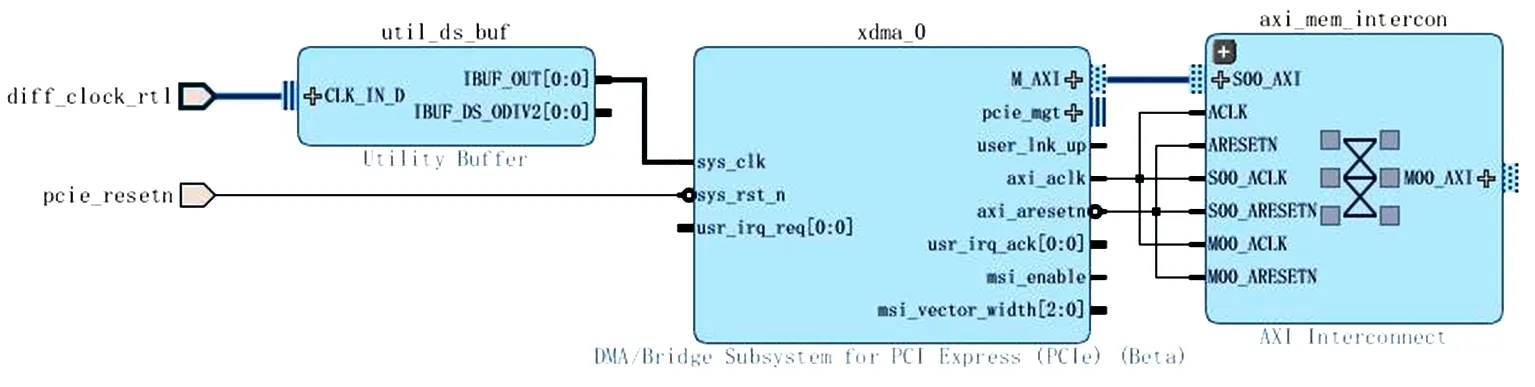

本文解决方法是FPGA逻辑部分的设计是基于PCI-E硬核XDMA IP实现。采用的数据传输方式是SG-DMA方式,它是通过使用链表描述物理上不连续的存储空间的方式,把链表首地址传回给DMA控制器。DMA控制器在一组连续物理地址的数据传输完成之后,并不是像block DMA发起中断,而是根据链表的指向来传输下一块连续的物理地址上的数据,等到全部的数据按要求传输完成后再发起一次中断[7]。由此可见,SG-DMA方式比block DMA方式的传输效率高很多。而使用的XDMA IP核可以完美地支持SG-DMA的方式进行数据传输。PL端XDMA的设计连接图如图2所示。

图2 PL端XDMA设计连接图

2.3 RAM(PS)端设计

PS端设计连接图如图3所示,为了解决异步时钟的问题,把从PCI-E中接收到的数据暂存在FIFO中,FIFO的主接口连接到AXI_DMA的IP从接口上,当PS端发起数据DMA方式传输后,RAM端的ZYNQ处理器核会通过GP接口和AXI_LITE总线传输指令至AXI_DMA,当其接到指令后便通过S_AXIS_S2MM接口从数据缓存的FIFO中接收数据,因为PL端与PS端进行数据交换必须使用AXI总线的数据,因此AXI_DMA会把接收到的流模式数据变成AXI模式,当AXI总线的握手结束信号出现高电平时,则表示需要发送的数据已经传输完成,当一次数据传输结束,IP核便会产生中断信号,触发RAM端的中断控制器响应,PS通过中断服务函数清除AXI_DMA的中断状态,在DMA中断函数中,通过DMA完成指示信号显示为高电平后,标志着一次完整的DMA数据传输结束。

PS的DMA数据接收采用了乒乓操作的模式,2个缓冲区交替进行数据接收[8],适合对数据流进行流水线式的处理,可以有效提高数据传输的效率。

在网口的设计中,根据需求,把开发板当作主设备,PC_2机当作从设备接收机。在逻辑程序中,调用网口连接函数,完成了开发板向PC_2机发起TCP 连接请求的命令。在TCP连接请求3次握手完成后,通过回调函数是否被调用表示开发板与PC_2接收机之间的TCP连接建立完成。

3 系统测试

本系统采用由Xilinx公司研发的ZYNQ 7035芯片构成的开发板,该开发板带有PCI-E X4物理接口,测试平台发送端使用带有PCI-E X4接口的工控机,接收端使用普通PC机,通过网口连接到开发板,共同搭建了PCI-E测试平台。实验测试如下:

测试一:从PC_1机通过应用程序驱动PCI-E X4接口,向FPGA开发板中发送数据,并进行PCI-E接口的测速。

测试结果如图4所示,当数据大小为1K时,发送速度为14 MB/s,接收速度为7 MB/s,而当数据大小增至8 M大小时,PCI-E的发送速度可达到1 160 MB/s,接收可达到1 467 MB/s,与文献[3]平均速度为506 MB/s相比,本方案极大提高了PCI-E的传输性能,并通过PCI-E的传输速度结果比较,可以看出随着测试数据大小的增大,可有效提高接口通路的利用率,SG-DMA的传输性能会越来越高,这与DMA传输的特性相符合。

图4 PCI-E接口速度测试

测试二:开发板通过千兆网口向PC_2接收机发送数据,接收机通过网络调试助手对接收到的数据进行显示。结果如图5所示,在发送文件中发送了从00到FF的循环数据,经过网络接收数据与发送文件的对比,数据准确且没有丢包和错包的现象发生,解决了传统状态机极易出现的丢包和错包的情况。

图5 通过千兆网口向PC_2机上的网络调试助手接收 从PCI-E接口接收到的数据

4 结束语

通过调用IP核的设计方法完成了PCI-E总线接口的实现,并在PS端采用逻辑程序对网口进行开发,联合开发板和搭建的硬件平台,对整个系统进行了测试,实验结果表明本方案的正确性和可靠性,验证了PCI-E接口的传输速度。为了能够进一步提高在FPGA开发板上PCI-E接口的高速传输数据的应用性能,下一步可在其中加载SMS4加密算法,对数据进行加密处理,并在处理器上搭载实时操作系统进行复杂的数据处理,最后通过千兆网口发送到网络上。该项目可发展成高速的数据加密卡设备,在网络安全领域具有广阔的应用前景。