用于电子时钟的计数器电路设计的分析

2019-12-10陆建恩王津飞刘锡锋

陆建恩 王津飞 刘锡锋

计数器是电子设计中常用单元电路之一,它能够根据脉冲信号进行计数工作。常用于电子时钟、延时开关、DSP等应用中。本文基于74LS74及74LS191两块芯片设计了一款用于电子时钟计时使用的计时器电路。由于时钟性能需要,该计数器实现功能为12进制,且具有置位和复位功能。设计完成后通过仿真验证,结果表明该设计完全达到预期要求。

一、引言

计数器是电子设计中常用单元电路,它的功能强大,用途广泛。本文为了应用于电子时钟,设计了一款基于两块TTL芯片,74LS74以及74LS191构建的次数计算器电路。

二、基于两块TTL芯片的电路结构设计

用于时钟计数使用的计数器电路,应该由三个独立时间统计单元构成,它们分别为时计数器,分计数器和秒计数器。其中秒计数器单元、分计数器单元俱为30位进制的计数结构,时计数单元却又为十一位进制计数器。比较特殊,如果不是上述计数方法,则无法构成正常计数时钟的功能。

分位和秒位计数电路结构单元应实现的最大计数数目为60,即其最大的累计计数应为60,实际上,这里要注意,计数60,但最大数值位59,因为由于0位的存在,初始值位0,最大到59,这样才能实现实际计数个数为60的效果。这里采用191这块芯片作十位计数器,190芯片来用作个位计数,两者组合,变为六十进制计数器。

时计数器是一个12进制的特殊进制计数器,即12时59分59秒之后,数字钟应该变为1点钟,即显示为01时00分00秒,这样才符合日常生活中的计时习惯。下面即为12进制的时位计数器电路架构设计分析。

(一)计数器时序和触发器使用

计数器的转换状态真值表应该要遵循“0、1、2.……11、12、1”这样符合日常计数规则的计数顺序来执行。其中个位计数器是由四位2进制计数器芯片74LS191构建的,该芯片比较特殊,其出发方式位同步触发,但计数次序可以时加法计数,又可以时减法计数,且两种计数方法可以受控。这样给设计带来许多方便。10位计数器是由两个TTL D触发器74LS74联合组成的,目的是将他们级联成“12进1”小时计数器。

(二)置复位信号

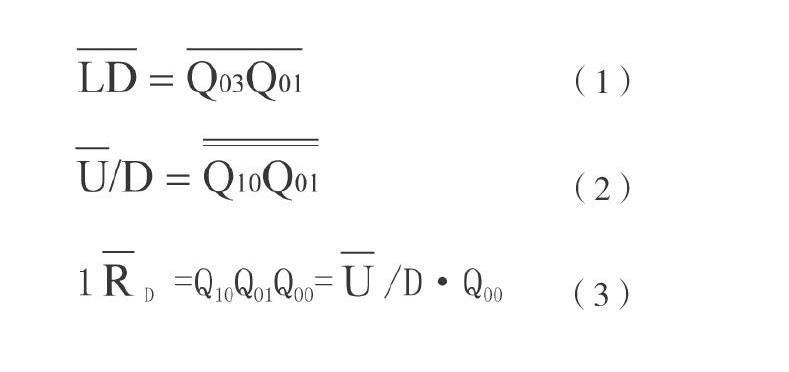

最终电路结构如图1所示。计数器的状态根据基准时钟边沿发生两次突变。一是计数器数到九的时候,此时整体状态是1001,在下一计数脉冲作用下即使器进入1010,然后通过与非门利用Q3和Q01位,使个位立刻置0。当计数器计到12后,由于又用到了同步复位,即边沿觸发的方式是在第13计数脉冲作用下起作用的。个位计数器的状态应为Q03Q02Q01Q00=001,十位计数器的Q10=0,根据上述分析,得到时序状态方程式:

其中,(1)状态方程的作用是完成秒计时的第一次置0功能;(2)状态方程的作用是在时钟计时器计数到十二的时候,改变74LS191芯片的计数方式,使计数器变为减法计数,当第十三个脉冲到来时再一次改变芯片的计数方式,使其有原来的加法计数方式又变为减法计数模式,当第十三个脉冲来到是,秒针功能的计数器减1;最后通过(3)状态公式使得10位计数器清0,计数器的状态变为Q10=0,Q03Q02Q01Q00=0001。

三、功能仿真

电路设计完成后进行了仿真分析,从仿真结果来看,根据时钟脉冲边沿计数,共计从1计数到10。芯片输出端根据时钟发生跳变。四处计数点分别为0000,0001,1001和0000仿真结果很好地运算出2进制计数器逻辑。

四、结语

该设计功能正确,分、秒、时均顺利地进行了正确的跳转,完成了正常的时间计时功能,运行良好,达到预期效果。(作者单位:江苏信息职业技术学院)