基于软件无线电平台的中频信号处理系统设计

2019-12-02

(哈尔滨医科大学附属第四医院,哈尔滨 150001)

0 引言

软件无线电(SDR)的主要设计理念是尽可能使A/D和D/A转换器靠近射频天线端口,并通过编辑软件的方法实现通信硬件的不同功能[1]。考虑到DSP或FPGA受到处理速度和数据存储容量的限制,通常只能在中频(IF)模块之前放置A/D和D/A转换器[2]。

经典的IF收发器软件无线电结构由T/R开关,低噪声放大器(LNA),混频器,宽带IF放大器,功率放大器,宽带滤波器和数字信号处理器组成[3]。对于数字信号处理器,它可以由ASIC、DSP和FPGA实现,但是在软件无线电平台设计过程中,ASIC不再适用于软件无线电系统[4-5]。

本文提出了一种使用ADC+FPGA+DAC的硬件结构模式,实现软件无线电平台的中频信号处理系统的设计,构建了使用FPGA数字处理器控制ADC对MSK信号进行采样,实现将模拟信号转化成数字信号供主机进行处理的整个过程。本系统单独使用FPGA处理处理中频数字信号数据,提高了数据处理能力,并设计了通用主机接口拓展相关通信功能,使得数字信号处理技术可以用于多种通信系统,提高了其实用性。

1 系统组成及工作原理

在本文设计的软件无线电平台的中频信号处理系统中,应用了Xilinx FPGA XC2V3000数字处理器,最大采样频率为210 MHz的ADI ADC AD9430模数转换器(ADC)和最大采样频率为300 MHz的ADI DAC AD9753数模转换器(DAC),输入的处理信号以中频信号MSK IF信号为例,搭建了ADC+FPGA+DAC的MSK通信模块,通过通信接口将结果发送给主机,将模拟信号转化成数字信号供主机进行处理,分析了软件无线电平台的中频信号处理系统的整个处理流程。

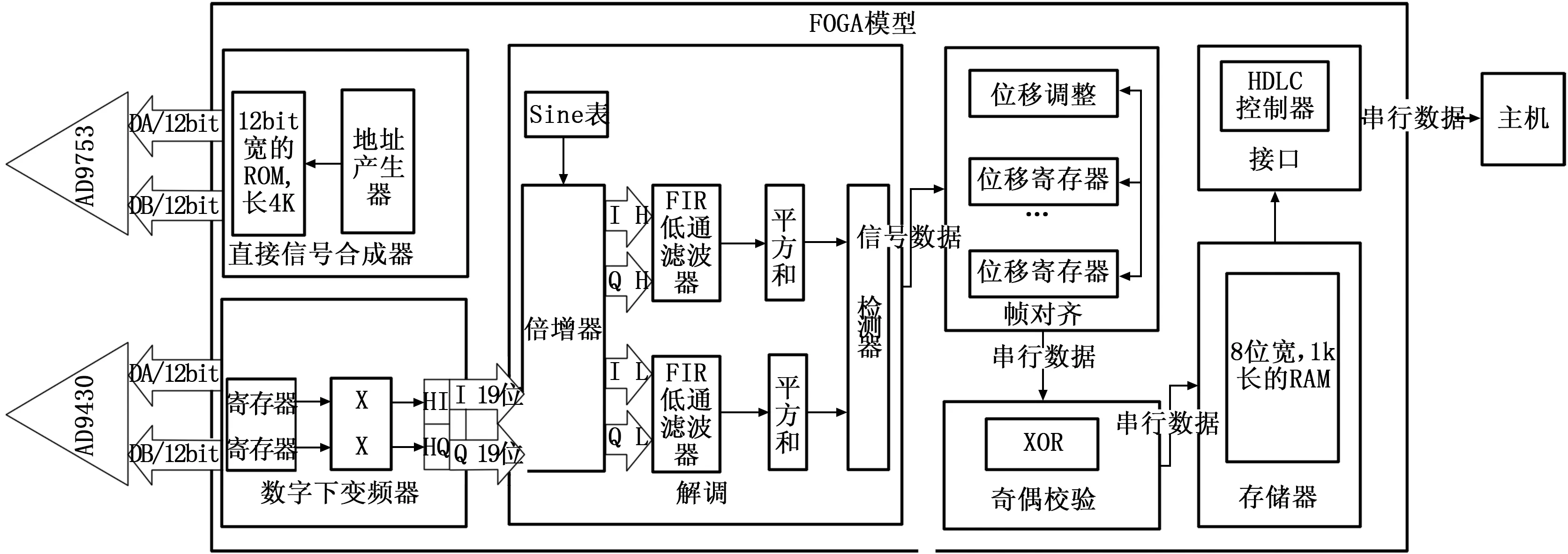

在数字调制的过程中,通常使用最小频移键控(MSK)进行调制[6]。MSK具有最小带宽的二进制频移键控信号,广泛用于数字通信系统。为了解调MSK IF信号,系统需要具备数字直接合成(DDS),下行数字下变频(DDC),同步(相干)解调等功能[7]。本文设计的软件无线电平台的中频信号处理系统的框架图如图1所示

图1 软件无线电平台的中频信号处理系统结构图

从图1中可以看出软件无线电平台对整个IF信号的处理流程,主要模数和数模信号的转化,具体的工程如下:首先采用ADC采样模数转换器,将模拟信号采样转化为数字信号,供数字处理机进行处理。数字信号在经过信号下变频后,在数字信号处理下,可以存储在FPGA的缓冲区中,然后通过FPGA的并行数据接口提供给主机进行使用,加快了数字信号的处理速度;经过处理后的数据在直接数字合成器中进一步处理,最后将处理后的数字信号转换为模拟信号输出。

FPGA内部信号处理的流程图如图2所示,XC2V3000具有丰富的逻辑处理资源,具备可编程门阵列逻辑电路,对软件无线电系统的兼容性和可替换性上有着无可比拟的优势,比较适合软件无线电平台的开发。根据DDS相关理论[7~9],FPGA数字处理器可以控制DAC产生MSK IF信号,并通过数字模拟通道将其传送到该模块的ADC前端。根据带通采样定理,本文设计的ADC+FPGA+DAC的MSK通信模块,使用FPGA数字处理器控制ADC对MSK信号进行采样,并在数字信号实现下变频,解调,帧对齐后,通过通信接口将结果发送给主机,将模拟信号转化成数字信号供主机进行处理,整个过程就实现了基于软件无线电平台对于中频信号的处理工作。

1.1 DAC数模转换器

AD9753是一款12位双数字输入数模转换器,其凭借稳定的性能,赢得了业界广泛的青睐。由于AD9753内部锁相环(PLL)电路能够使输入时钟频率加倍,因此两个输入的数字数据将以输入时钟速度的两倍速度进行模拟信号的转换,并将转换的信号发送出去。因此,FPGA数字处理器可以使用一半的采样频率来控制DAC[10]。

在FPGA内部生成两个12位宽,4 096深度的只读存储器(ROM),可以存储4 096个采样单周期正弦波数据。根据DDS相关理论,可以得到频率控制字K。两个存储器分别以0和K为初始地址,以2K为增量地址。FPGA通过时钟芯片MC100LVEL16以差分形式将采样频率一半的时钟信号输入到DAC数模转换器中[11]。以此速率,从两个存储器读取的数据被发送到DAC的P1B和P2B端口。DAC输出的模拟信号将通过低通滤波器和放大器电路变为单频信号。

可以根据不同的控制字K得到不同输出频率的信号,并在发送所需的码字的基础上进行两个信号的编码组合,从而实现MSK信号的传输。设AD9753芯片的相位累加器的位数为N,AD9753的频率控制字的相位增量为K,参考的时钟频率为CLKIN,AD9753的频率控制字为Freq,则根据DDS相关的计算理论[12-13],可以得到DDS输出信号的频率为:fOUT=(CLKIN*K)/2N,输出信号的频率的分辨率为:ΔfOUT=CLKIN/2N,假定对于一个相位累加器的位数N=32位的芯片来说,参考的时钟频率CLKIN=125 MHz,相位增量取值K=1时,输出的信号评率是最低的,根据计算可知,最低的输出频率为0.03Hz,同时其输出的信号频率的分辨率也是最低的。在实际的应用程序中,K的值不宜过大,否则会生成失真的波形,同时对于输出的频率fOUT理论上的最大值至少应该要小于CLKIN/2,经过以上的分析可知,如果想要提高输出的频率fOUT的最大值,就需要提高系统的参考的时钟频率CLKIN的值。

1.2 ADC模数转换器

AD9430是一款12位单芯片采样模数转换器,专门针对高性能、低功耗和易用性进行了优化,它的转换速率峰值最高可达210 MSPS,具有良好的动态性能,适用于宽带载波和宽带系统的使用[14]。AD9430的芯片集成了全部的模数信号转换包含的必需功能,能够提供完整的信号转换策略。由于AD9430内部时钟管理电路能够将输入时钟的频率除以2,因此输入时钟频率的一半用作输出数据被锁存,然后将模拟信号转换成的12 bit的数字信号传输到FPGA中进行处理,值得注意的是,AD9430模数转换器的最高工作频率超过了4 GHz,相位Jitter典型值RMS仅为0.2/s,是一款性能非常优秀的芯片。因此,FPGA可以使用一半的采样频率进行数据处理。

MSK IF信号经过处理后,转变成变压器后的差分信号,然后输入到ADC采样模数转换器,将差分信号转化为12 bit的数字信号。同时,FPGA生成采样时钟,并通过时钟芯片MC100LVEL16以差分形式将其输入到ADC中进行处理。ADC通过数字端口DA和DB将采样数据发送到FPGA,并将采样频率同时分为两个,以差分形式提供给FPGA作为数据同步时钟DCO。ADC的数据被分配给内部寄存器,以便在DCO的下降沿通过FPGA进行数字下变频。

图2 FPGA内部信号处理流程图

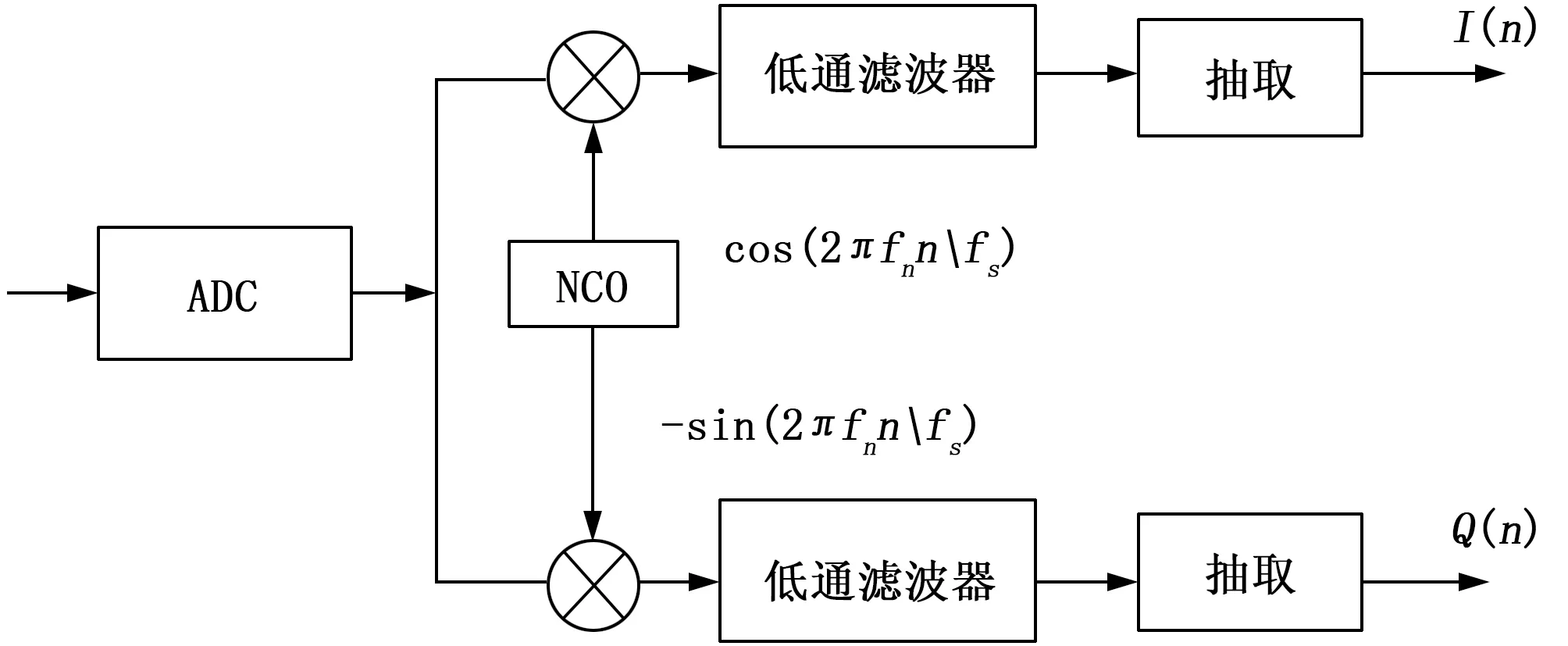

1.3 数字下变频(DDC)

DDC的主要目的是将经过数字混频ADC采集到的中频(IF)数字信号的频谱下变频到基带信号中,然后完成抽取滤波,恢复成原始的信号,数字下变频是采用数字信号技术实现下变频的,它主要包含可数字滤波、正交变换、采样和抽取等算法,DDC的原理图如图3所示。

图3 DDC原理图

在本文的设计过程中,由于AD9430采样的数据输出是两个并行的数字信号输出,因此,不需要FPGA进行数据输入的奇偶检验提取。端口DA和DB的输入数据将被直接视为I Road和Q Road信号,然后采用另一个I信号点和另一个Q的相反符号信号点分别实现信号的处理乘以(-1)n。

本文设计的系统中,通过8个并行乘法器和一个具有8输入,1输出的3级加法器进行设计,可以获得八波段FIR滤波器。设计了两组具有相位延迟的滤波器系数为2 π/T的滤波器,I信号的过滤器被延迟后T/2采样周期,Q信号不做延迟处理。因此,与Q信号相比,实现了I Road和Q Road的时间对齐。

在实施的过程中,从前面的分析改变采样频率为fs=4fL/3。fH变为2Δf和fL变为直流(DC)信号经过DDC处理。然后,只有混合2Δf有必要在里面加工FPGA,节省了乘法器和逻辑单元的FPGA内部资源。

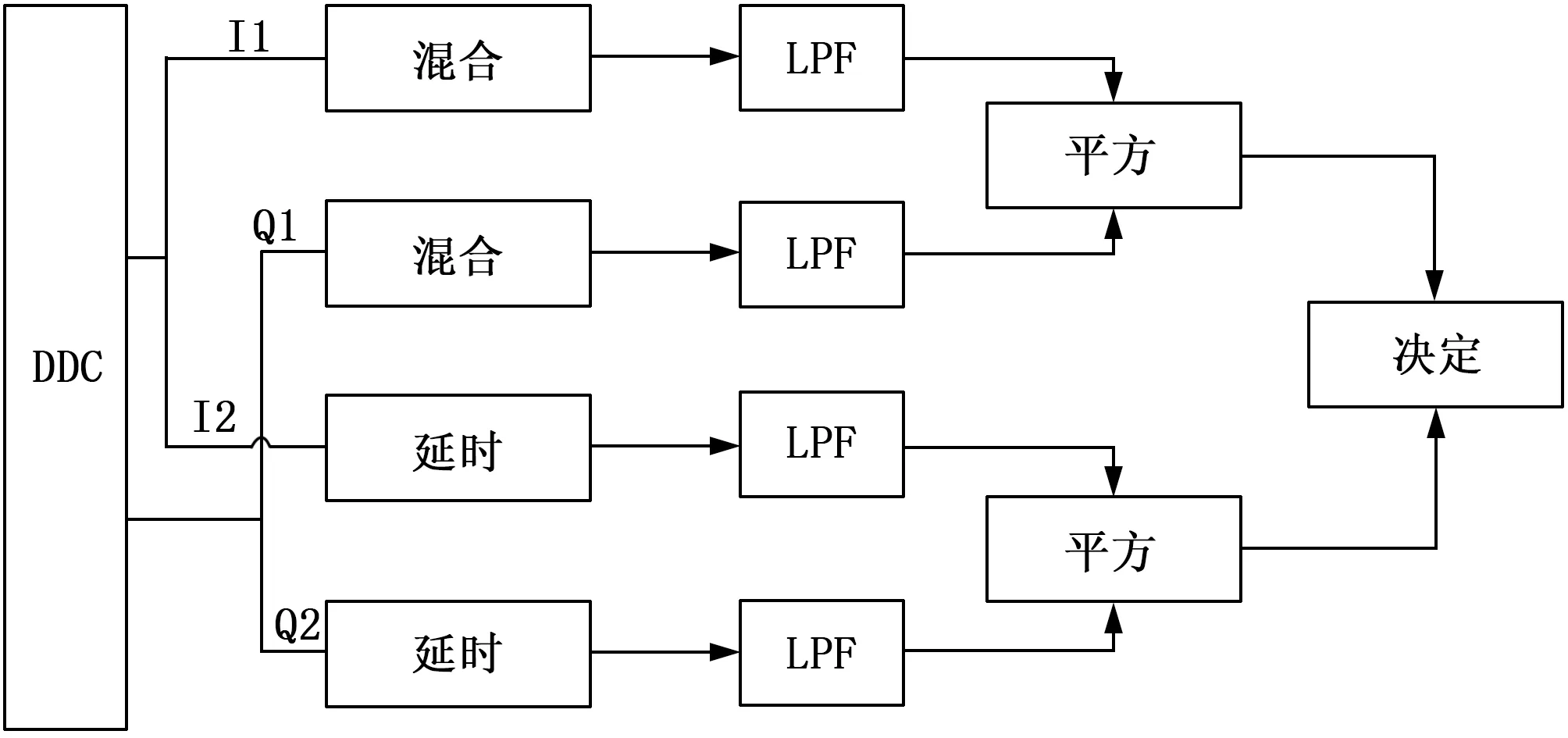

1.4 MSK解调

由于低频信号在ADC采样和DDC处理过程中已转换为两部分的I,Q直流信号,因此MSK解调过程也应该分为两部分,分别对I信号和Q信号进行调制,如图4所示。

图4 MSK解调流程图

在FPGA内部生成存储器,存储采样的单周期正弦波数据,然后,使用查表法实现数据的查找,以处理频率从存储器读取数据,并以频率为本地振荡器(LO)信号2Δ°F产生信号。随后,I1、Q1和LO信号在图4所示的混合器中混合,频率分量分别为DC、2Δ°F和4Δ°F。为了确保同时向LPF发送四个信号,I2和Q2信号通过延迟线设备进行处理,处理的延时时间与混频器相同[15]。

之后,使用与多相滤波器相同的方法生成FIR低通滤波器,并改变特定的生成系数,设定截止频率为500 KHz。在LPF之后,过滤高频分量并且仅保留DC分量。分别取I1和Q1,I2和Q2的直流分量的平方和累加,得到两个频率的MSK信号分量的幅度信息。最后,通过联合判断幅度值来实现MSK调制信号。

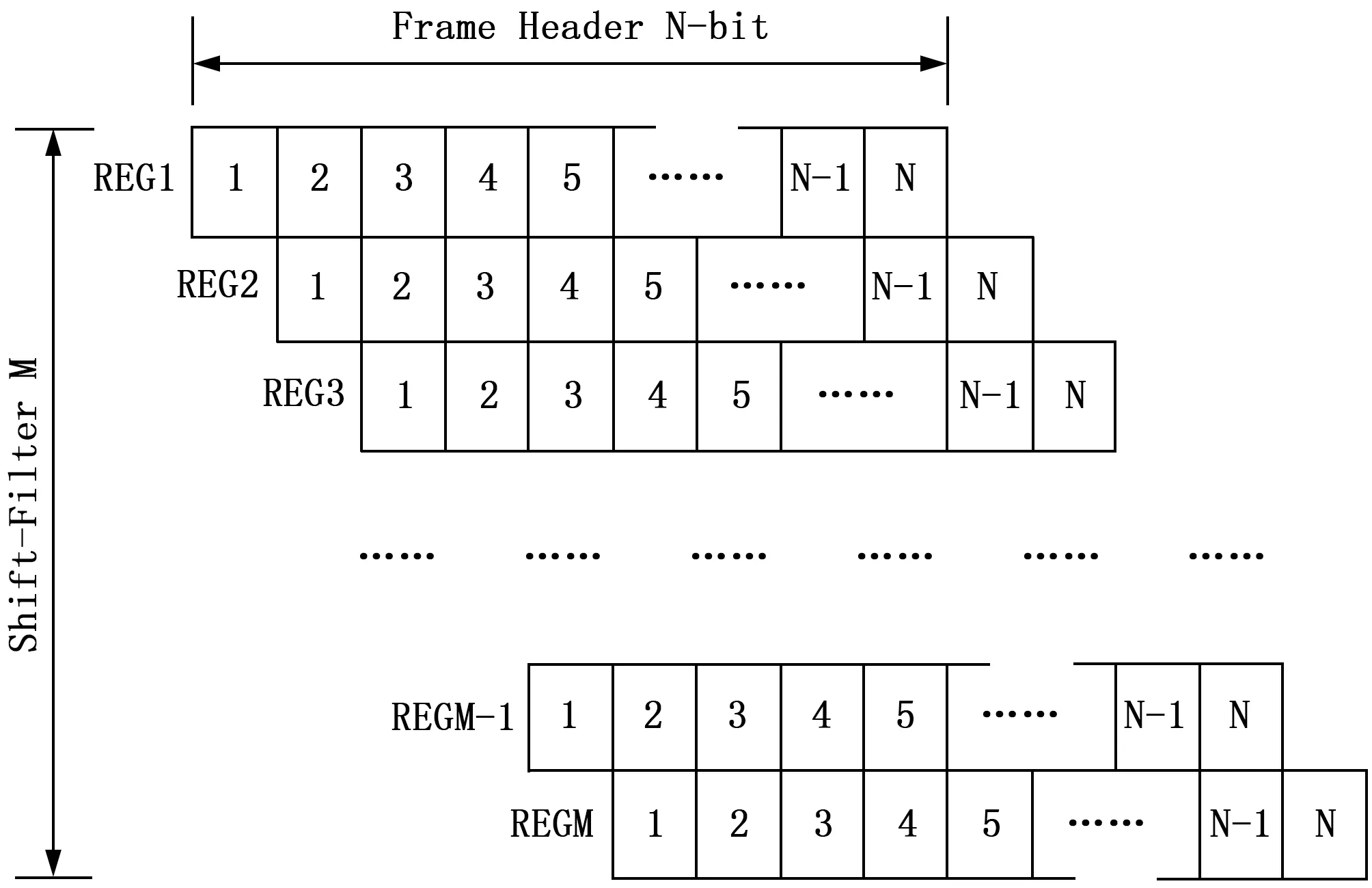

1.5 帧对齐

在获得视频数字信号之后,处理数字信号对齐和帧对齐成为了首要的问题。对于帧对齐,使用匹配方法进行移位寄存器操作[16]。不妨假设帧头的长度为N,然后在FPGA内部构造长度为N位的M个移位寄存器。当检测到输入信号时,启动当前寄存器并同时准备下一个寄存器,然后连续循环启动M个移位寄存器。在每次移位之前事先判断寄存器的长度,如果任一寄存器的长度与之前指定的帧头的长度完全相同,则表示帧对齐成功;否则,继续移位直到帧对齐成功为止。帧对齐的过程如图5所示。

图5 帧对齐过程

1.6 数据处理和传输

在帧对齐成功之后,根据数据帧的定时关系周期性地收集MSK数据,然后解码每组收集的数据,解码操作通常包括删除前缀,后缀和奇偶校验位等[17]。对解码的数据执行按位异或运算XOR,并将结果与奇偶校验位进行比较。如果两者相同,则判断解码数据有效,并以字节的形式存储在FPGA内部存储器中;如果不是,则丢弃此数据帧并向主机发送错误报告。

为了能与主机进行通信,在FPGA内部添加了生成SPI通信模块,它是一种全双工的高速同步通讯总线,能够保证数据传输的实时性,SPI通信模块规定了4中不同的通讯模式,在实际的应用过程中,应该保证通讯主机和从机工作在相同的模式下。SPI通讯模块的工作方式通过时钟极性和时钟相位联合确定,同时通过通信接口上的转换器件进行光耦合隔离和电压转换。在本文系统的设计过程中,采用的是SPI通信模块的常用模式0,主机通过SPI通信模块向FPGA处理器发送编码数据和相应的请求。SPI通信模块接收编码数据,并根据命令将要存储的MSK数据和错误报告发送给主机[18-19]。在通讯的过程中,对于发送状态机,必须在通讯时钟SCK上升沿到来之前将通信的数据放在MOSI信号线上。因此其状态的改变应当在时钟上升沿到来之前。因此,本文设定发送状态机的在SCK时钟的下降沿进行状态变换,在SCK的低电平中心将需发送的数据压至MOSI线上;相对的接收状态机,为了保证通信状态跳变的协作性,也采用SCK下降沿的时刻作为状态跳变的时间点。在SCK上升沿状态下,接收状态机将数据采集存储至接收缓冲口,并在采集完一字节数据后生成标志信号脉冲。这个脉冲将持续一个SCK周期,以便FPGA其余模块进行识别。

2 系统测试与分析

在测试过程中,本文设置的参数如下:IF 120 MHz,带宽10 MHz,信号速率1 Mbps,帧速率100 fps,并取模块的MSK信号输出作为模块的IF信号输入,通信速率2 Mbps。测试时间为30 h,测试帧数为107。

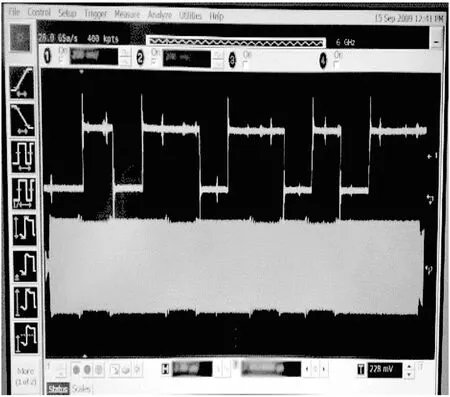

输出MSK符号和输入MSK信号结果的比较如图6所示。经过大量实际测试,输出符号的平均延迟为1.05 μs。当输入IF信号的信噪比(SNR)大于10 dB时,MSK解调的误码率(BER)平均优于10-6,通信的误码率(BER)平均优于10-6,满足无线通信的一般要求,能够胜任对中频信号处理的需求,达到了本文的设计要求。

图6 实验结果比较

3 结论

本文根据SDR的思想,设计了基于ADC+FPGA+DAC的MSK信息处理通信模块,还实现了包括带通采样和IF MSK信号的产生功能。在FPGA内部集成实现了DDC、多相滤波和MSK解调等数据处理。由于该系统基于宽带IF采样的SDR架构,并且所有信号控制和数据处理都在一个FPGA中实现,因此,通过修改硬件程序可以满足各种通信系统的要求。由于在信号采样过程中应用了数字下变频技术,因此也可以实现更高载波频率的IF信号的处理。该基于软件无线电平台的中频信号处理系统具有良好的通用性和重建性,具有广阔的应用前景。