基于FPGA的伺服电机转速控制系统研究

2019-12-02

(1.西北核技术研究院,西安 710024; 2.国防科技大学 气象海洋学院,南京 211101)

0 引言

在高速高精伺服控制系统中,通常选用增量式光电编码器作为位置传感器,结合同步时间信号和闭环反馈控制算法实现对伺服电机转速的精确控制[1]。随着伺服控制需求的提高,传统的以单片机或DSP等微处理器为核心的伺服控制系统表现出系统结构复杂、应用灵活性差、运算能力不足等缺陷,已难以满足伺服控制系统对速度和精度的要求[2]。

随着集成规模和运算速度的不断提升,FPGA器件被广泛应用于伺服系统控制领域。与单片机、DSP等传统控制方式相比,基于FPGA的伺服控制系统具有以下优点:采用硬件并行处理技术的FPGA器件比DSP芯片具有更快的运算速度和更低的功耗;相比于单片机的软件控制方式,FPGA通过硬件电路执行控制指令,不存在程序跑飞、软件延时等问题,提高了伺服系统的稳定性和准确性;FPGA器件内部集成有通信接口、数据缓存、专用IP核等功能模块,使得电路设计更加灵活多样,有效缩短了开发周期,提高了设计效率[3-4]。

本文构建了基于FPGA的伺服电机转速控制系统,选用高精度光电编码器作为位置传感器,结合同步时间信号,实现了对电机转速的闭环反馈控制。仿真和实验结果表明,控制系统具有较高的控制精度和响应速度,额定转速下的速度控制精度可达1 r/min,位置控制精度可达0.03°,并且能够执行较为复杂的伺服控制算法,可实现对电机转速的精确控制。

1 系统总体结构

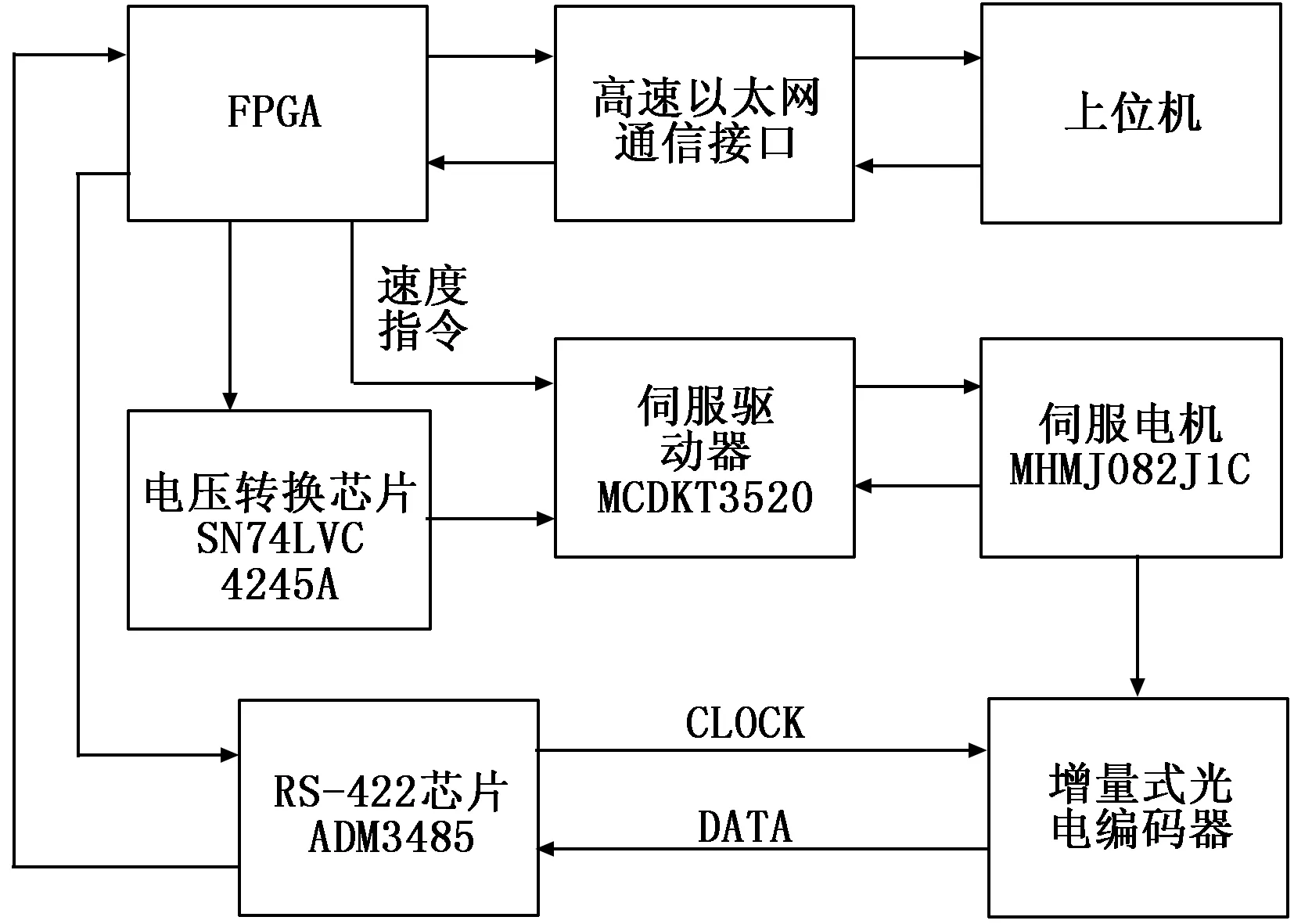

控制系统结构框图如图1所示,主要包括伺服电机转速控制模块、光电编码器数据读取模块以及FPGA与上位机数据通信模块。系统工作方式如下:

1)在上位机软件控制下,FPGA向伺服驱动器发出速度指令,驱动电机转动。

2)在电机转动过程中,光电编码器测量电机转轴的位置信息,并在FPGA时钟脉冲驱动下,通过RS-422串行通信总线将编码序列传输至FPGA。FPGA根据电机转轴位置及同步时间信号计算电机的实时运行速度,通过PID算法实现对伺服电机转速的闭环反馈控制。

3)为减小数据传输延时造成的测量误差,本文采用高速以太网通信方式实现FPGA与上位机之间的数据交换,其通信接口主要由Xilinx FPGA内部集成的相关IP核实现,具体为:由三模式以太网MAC IP核实现MAC子层协议,由GTP高速串行收发器及PHY芯片88E1111实现物理层协议。

图1 控制系统结构框图

2 各功能模块实现方法

2.1 伺服电机转速控制模块

伺服电机具有体积小、重量轻、响应速度快、过载能力强等优点,在工业测控领域得到广泛应用。目前,高性能伺服控制系统多采用永磁同步交流伺服电机及与之匹配的全数字式伺服驱动器,主流生产厂家包括美国Kollmorgen公司、德国Siemens公司、日本松下公司等[5]。本系统中选取松下MINAS-A5 II系列伺服电机及驱动器,该系列伺服电机具有良好的速度控制性能,能够实现整个速度区间内的平滑控制,并且具有较高的控制精度和响应速度。

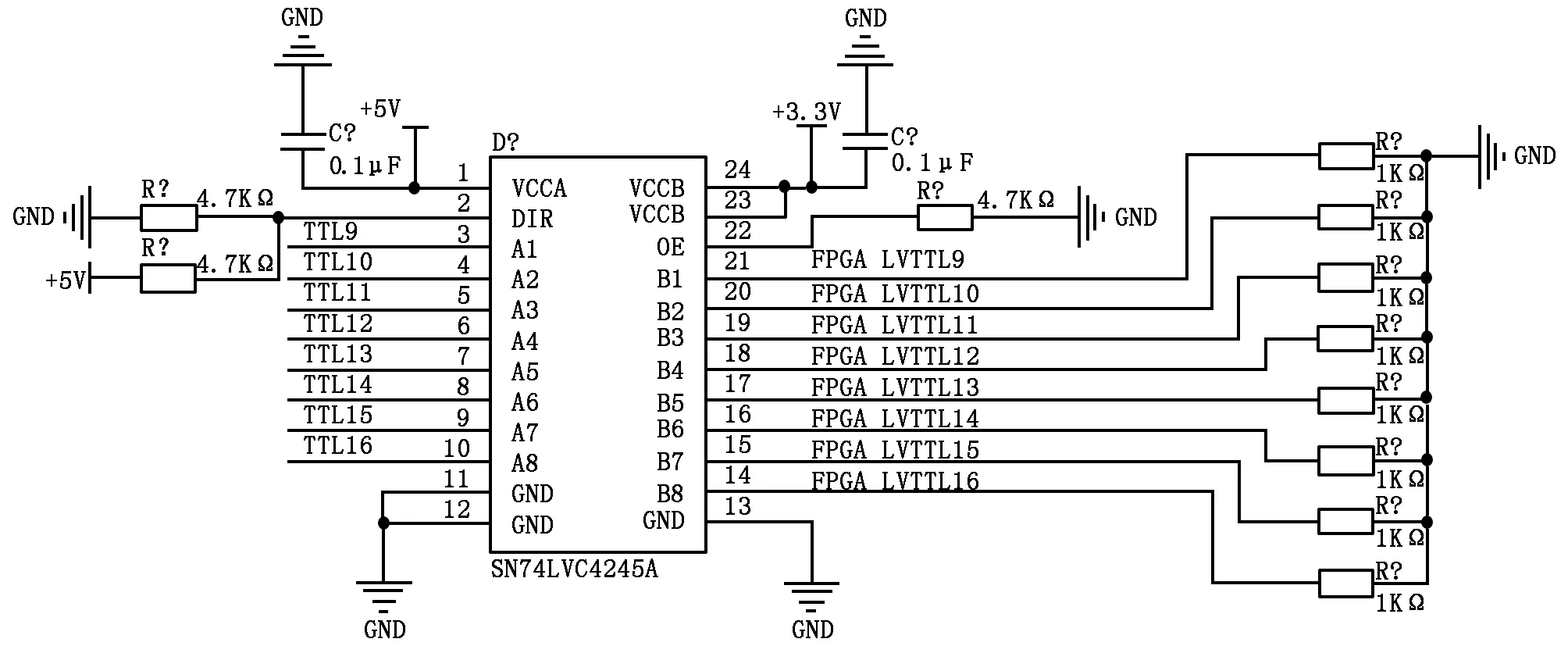

在该伺服控制系统中,FPGA主要实现以下功能:通过高速以太网接口与上位机进行通信,接收上位机发出的速度控制指令,并向伺服驱动器发出相应的控制信号;通过RS-422串行通信接口读取光电编码器的二进制编码序列,并将其反馈至上位机;根据时间信号和位置信号运行闭环反馈控制算法,实现对电机转速的精确控制。为调整FPGA和伺服驱动器的工作电平差异,选取TI公司生产的SN74LVC4245A芯片实现二者之间的电平转化,其接口电路如图2所示。

图2 电平转换接口电路

2.2 光电编码器数据读取模块

光电编码器是一种集电子、光学、机械等多学科于一体的角度传感器,具有抗干扰能力强、分辨率高、可靠性好、体积小、重量轻和易于维护等优点。通常安装于机械设备转轴上,可将旋转轴的角度位移量转换为二进制(或格雷码)编码序列,并传输给计算机或其他测控设备,为机电系统的闭环控制提供位置反馈信息。将转轴位置信息与时间信息相结合,还可以获得速度、加速度等信息,可用于系统的闭环反馈控制[6-7]。

目前,较为知名的光电编码器制造商主要有美国Itek公司,日本Nikon、Connon公司,德国Meyle、Hengstler公司等。本文选取Hengstler AC36型增量式编码器作为位置传感器,其分辨率为13位,精度可达±35″,采用SSI同步串行接口通信协议,输出编码格式为二进制码。

SSI接口是一种具有帧同步信号的串行通信接口,大多数高精度编码器均采用该接口方式。SSI采用主控芯片主动读取方式,在时钟脉冲驱动下,从最高有效位读取编码器的编码序列,通过时钟、数据同步的串行方式完成数据传输。基于上述特征,本文采用RS-422串行通信总线读取编码器输出的编码序列。

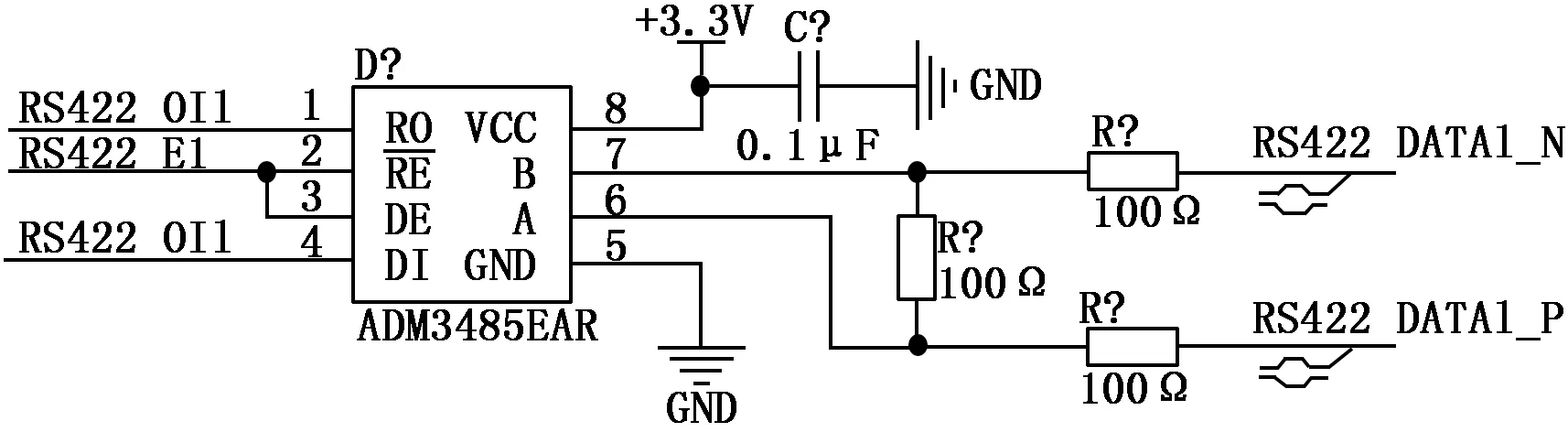

RS-422是目前广泛采用的一种串行传输总线,由于其接收器采用了高输入阻抗和发送驱动器技术,使得RS-422具有更强的数据传输能力,最高传输速度可达10 Mbps,最大传输距离为4 000英尺,可实现点对多点的双向通信,并且具有抗干扰能力强、通信成本低等优点[8]。ADM3485是一种低功耗差分线路收发器,在整个共模范围内符合RS-422/RS-485通信协议,数据传输速率可达10 Mbps。本文选取ADM3485串行接口芯片和RS-422数据传输总线完成编码器通信接口电路的设计,其结构如图3所示。

图3 编码器通信接口电路

2.3 高速以太网通信接口设计

作为目前主流的局域网技术,千兆以太网沿用了原有以太网标准所规定的技术规范,包括CSMA/CD协议、以太网帧格式、流量控制等,同时又包含了8 B/10 B线路编码、载波扩展等新技术。相比于USB、RS-485等通信总线,千兆以太网在传输速度和通用性等方面具有更强的优势,并且可以直接连接到Internet,具有更大范围的远程访问能力[9-10]。基于上述优势,本文选取千兆以太网方式实现FPGA与上位机之间的通信。

千兆以太网通信接口的设计重点在于网络结构的MAC子层和物理层,其中MAC子层主要通过以太网MAC控制器实现,常用设计方式有两种:一种是将MAC子层和物理层集成在一块专用芯片上,通过网络芯片方式实现千兆以太网接入,常用的千兆以太网芯片主要有Marvell公司的88E8040、Realtek公司的RTL8168等。另一种是调用FPGA内部集成的相关IP核作为以太网MAC控制器,通过PHY芯片实现物理层设计。目前,Xilinx、Altera等主流FPGA生产厂家均推出了支持10/100/1 000 Mbps等多种传输速率的以太网MAC控制器IP核,显著降低了网络接口的设计难度。

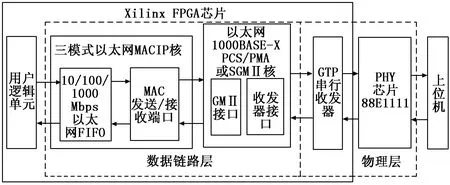

本文选用Xilinx公司的三模式以太网MAC、GTP高速串行收发器等IP核以及Marvell公司的PHY芯片88E1111,实现了千兆以太网的接口设计,其结构如图4所示。

图4 千兆以太网通信接口结构框图

其中,用户逻辑单元用于实现以太网的上层传输协议,自定义数据帧格式并完成数据包的初步封装。三模式以太网MAC IP核是网络接口的核心部分,主要用于完成以下任务:在用户逻辑单元生成的初步封装的数据帧中添加帧首部、校验码等字段,将其转化为标准的以太网数据帧格式,并完成数据包的发送或接收。以太网1000BASE-X PCS/PMA或SGMII核用于实现MAC层与物理层间的串行通信接口设计,其内部的GMII接口和收发器接口分别连接到以太网MAC IP核的数据发送/接收端口和GTP串行收发器,最终实现速率为1 000 Mbps的高速串行数据传输。

网络接口的物理层协议由GTP串行收发器及PHY芯片共同实现。GTP串行收发器主要包括线路编码/译码器、串行/解串器、发送/接收FIFO等模块,可实现8 B/10 B线路编解码、数据串并转换等功能。根据网络接口各模块的功能需求,PHY芯片需支持1000BASE-T传输介质标准及GMII、RGMII、SGMII等多种接口模式。基于上述需求,选择Marvell公司的千兆以太网PHY芯片88E1111实现网络接口的物理层协议。该芯片支持10/100/1 000 Mbps三种以太网传输速率以及GMII、RGMII、SGMII等多种接口协议,支持传输介质及线路故障的自动检测,可通过5类非屏蔽双绞线实现物理层的数据收发功能[11-12]。

2.4 UDP通信协议实现

以太网传输层协议主要包括TCP和UDP两类,其中TCP协议通过数据发送端和接收端的多次握手操作来确保数据传输过程的准确性,因此会造成数据传输速度慢、系统资源占用多等缺陷。相比于TCP,UDP是一种无握手操作的传输协议,在数据传输过程中,收发双方不需建立链接,因而程序结构更简单,对系统资源的要求更低,且具有更高的数据传输效率[13-14]。基于上述对比,本文选取UDP协议作为FPGA与上位机之间的以太网数据传输协议。

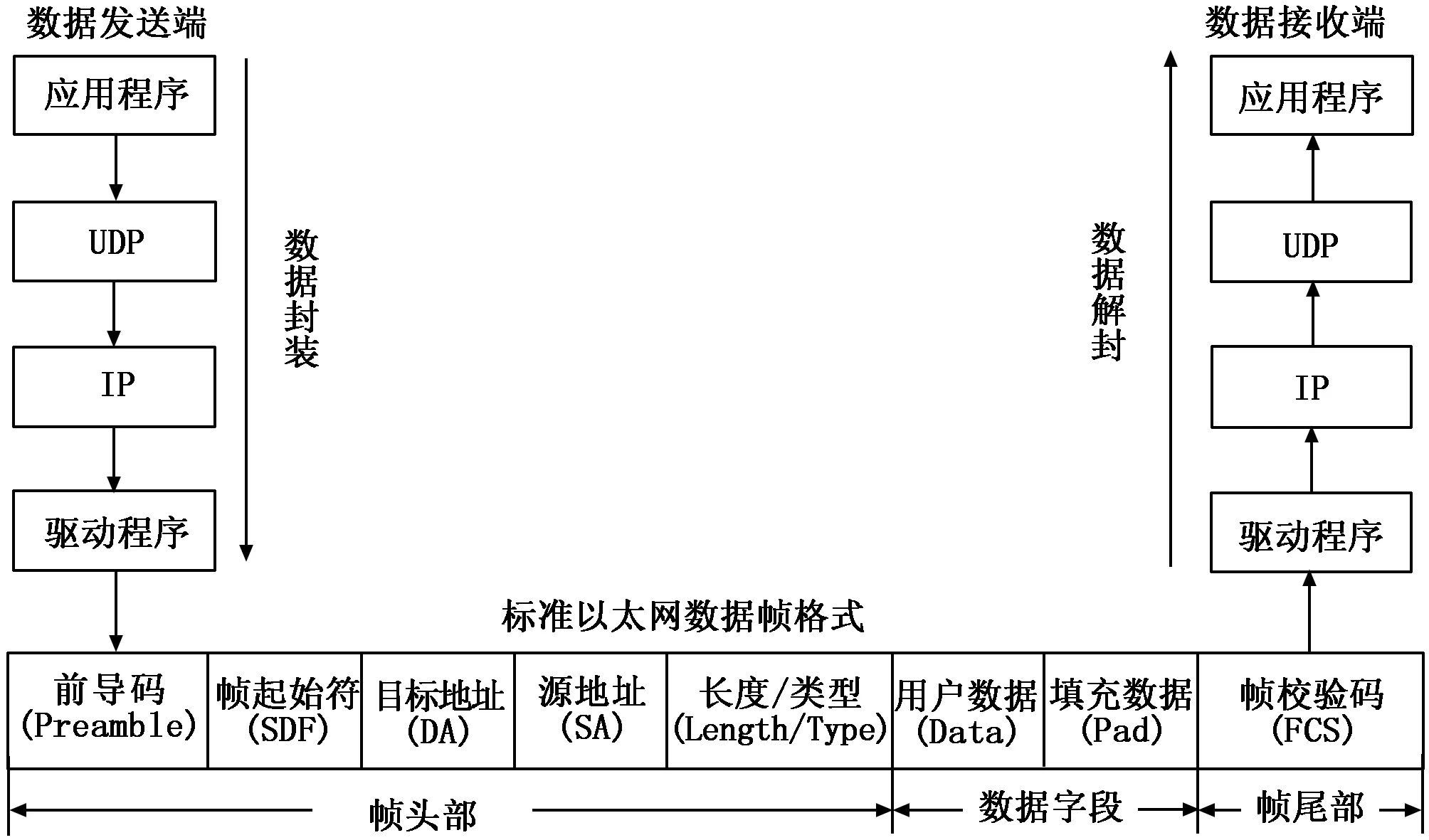

UDP协议数据传输过程如图5所示,来自于发送端的数据依次经过UDP/IP协议栈,并根据其格式要求添加UDP/IP数据包头。经初步封装的数据在MAC子层中添加以太网帧头部、尾部等字段,将用户数据封装为标准以太网数据帧格式并完成数据传输。以太网帧在物理层完成数据解封,还原用户数据并将其传输至接收端。

图5 UDP协议数据传输过程

3 实验验证与分析

ChipScope Pro在线逻辑分析仪是由Xilinx公司推出的一款虚拟逻辑分析工具,该工具可在FPGA内部时钟的触发下捕获用户需要了解的芯片内部的信号,并通过可视化窗口以波形形式显示出来。运用ChipScope可使工程设计人员快速检查设计结果的准确性,有效提高了开发效率。

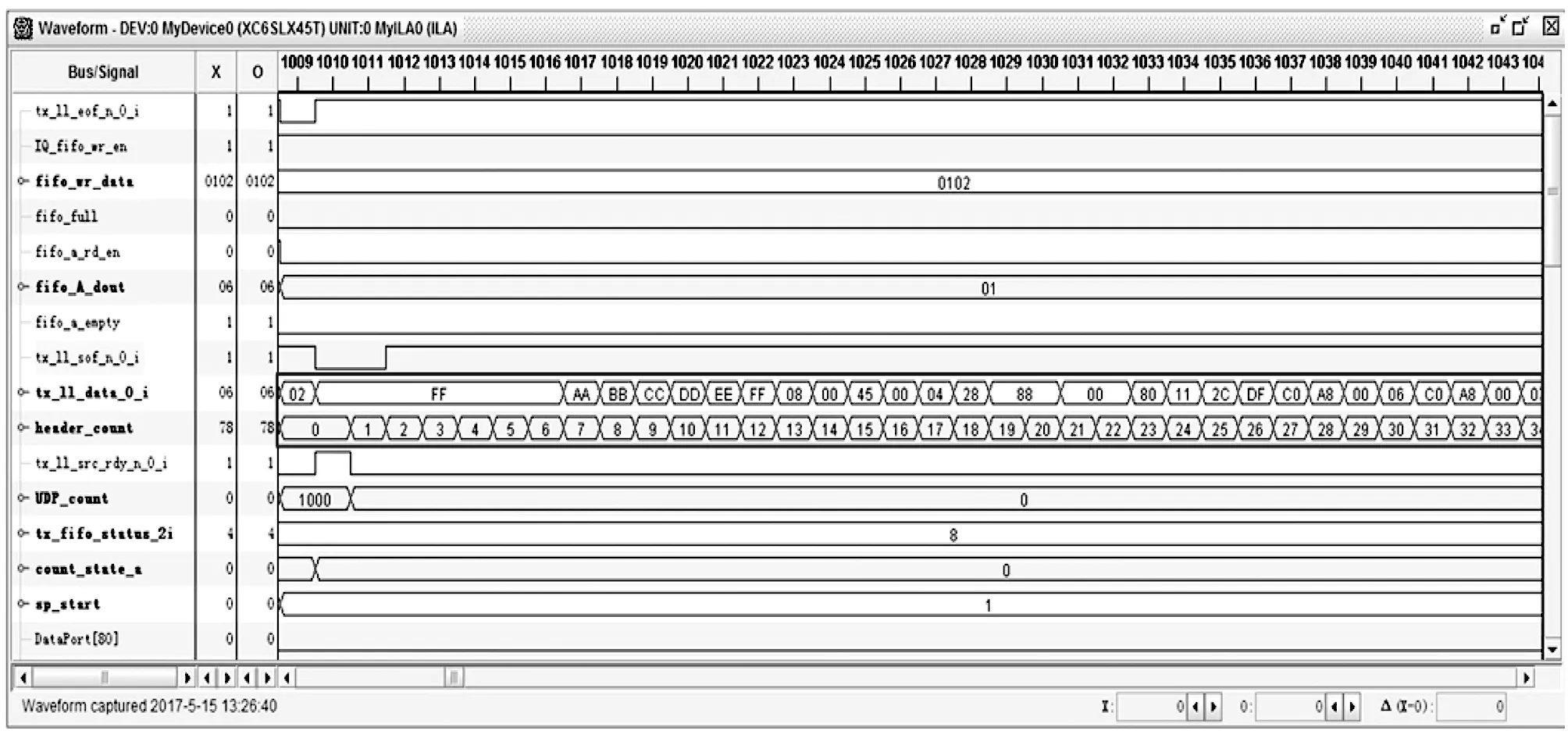

本文采用ChipScope Pro在线逻辑分析仪验证上述功能模块的设计方案。以高速以太网数据通信模块为例,FPGA发送至上位机的自定义数据帧格式如表1所示(截取前20位),该功能模块的在线仿真结果如图6所示。

由仿真波形可知,FPGA和上位机之间可根据设定的帧格式完成数据通信,图6与表1中的数据帧序号与内容可实现一一对应,由此证明了设计方案的准确性和合理性。

表1 FPGA发送至上位机的自定义数据帧格式

图6 高速以太网通信模块在线仿真结果

4 结论

本文构建了基于FPGA的伺服电机转速控制系统,选用高精度光电编码器作为位置传感器,结合同步时间信号,实现了对电机转速的闭环反馈控制。重点对各个功能模块的设计方案和编码器、FPGA、上位机之间的数据通信方式进行了研究。为验证设计方案的可行性,运用ChipScope Pro在线逻辑分析仪对设计方案进行在线仿真。仿真和实验结果表明,该控制系统具有较高的控制精度和响应速度,能够执行较为复杂的伺服控制算法,可实现对伺服电机转速的精确控制。