FPGA硬核处理器系统的数字化集成电路设计

2019-10-16王肖巍

摘 要:为最大程度降低系统成本,提高工作效率,提出FPGA硬核处理器系统的数字化集成电路设计。通过对电源电路、接口电路以及主控电路进行设计,完成电路整体设计。结合电路抗干扰设计,实现数字化集成电路设计。仿真实验证明,设计的集成电路相比常规电路,使得FPGA硬核处理器系统的工作效率更高,并且降低29.5%能耗。

关键词:硬核处理器;数字化;集成电路;电路设计

中图分类号:TH744文献标识码:A

我国多数机械装置常常应用FPGA硬核处理器来降低装置成本、功耗,从而提高装置性能。FPGA硬核处理器系统能够集成分立处理器,具有可编程逻辑的灵活性。[1]系统中常规电路设计虽然可以满足装置各项性能要求,但是会产生面积较大的电路板,严重影响机械装置的成本,同时产生不必要的电能消耗,因此提出FPGA硬核处理器系统的数字化集成电路设计。

1 FPGA硬核处理器系统的电路整体设计

根据FPGA硬核处理器系统的功能特征,首先对系统的主控电路进行设计。为满足多种类型信号的处理要求,设计的主控电路如图1所示。

设计的主控电路在确保FPGA硬核处理器系统的稳定性之外,还增加了抗复位功能,最大程度降低系统功耗。[2]

同时,为减少不必要的电能消耗,将FPGA硬核处理器系统的接入电源设计成5V。电源电路是FPGA硬核处理器系统从外界获得电源的唯一途径,因此设计电源转换电路,实现220V电源到5V电源的转变。将电源接口电路设计成F接口,[3]采用I/O接口,I/O接口芯片,通过输入不同的命令和参数,使得I/O电路动作,成为信号高速交换的通道。通过对主控电路、电源电路以及接口电路进行设计,完成电路整体设计。

2 数字化集成电路的实现

在FPGA硬核处理器系统中,信号分为模拟信号、数字信号、高频信号以及低频信号,常常受到外界信号干扰,大大降低电路中信号处理精度,使得FPGA硬核处理器系统工作效率降低。因此为了增加电路抗干扰能力,对电路进行抗干扰设计。

在FPGA硬核处理器系统的主控电路中加入差分放大器,对电信号放大处理。差分放大器通过F接口,使得输入频率为25HZ的电信号,转换成以正弦和余弦两路电信号,应用互联网技术对两路电信号进行隔绝,确保了信号的原始性。由于差分放大器输出为高压电信号,需利用220Ω的电阻将高压电信号调制成5V,形成低压电信号,从而实现数字化集成电路的设计。

通过对主控电路、电源电路以及接口電路进行设计,完成电路整体设计。结合电路抗干扰设计,实现数字化集成电路设计。

3 仿真分析

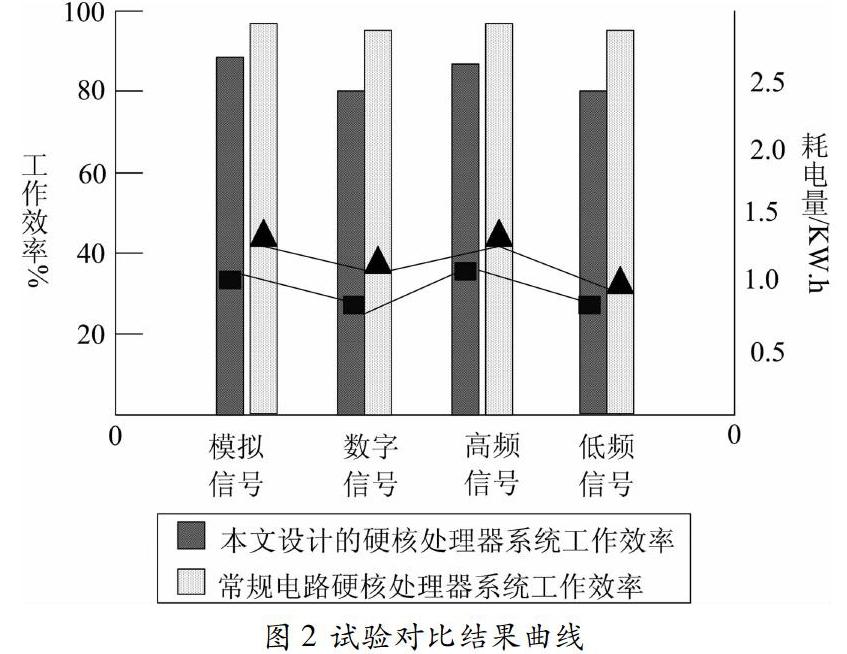

仿真试验需准备的设备及参数包括:搭载simulation仿真软件的计算机两台套、两种设计电路的FPGA硬核处理器系统(常规的以及本文提出的数字化集成电路)、仿真参数变量。试验过程中,多次改变输入的信号形式,对两种不同电路的FPGA硬核处理器系统进行工作效率对比实验。同时记录FPGA硬核处理器系统单位时间的耗电量,绘制试验结果图表,如图2所示。

由图2可知,本文设计的集成电路,无论处理哪种类型信号,工作效率几乎不变,稳定性极高。同时采用算术平均值计算法,计算能耗比率,得出本文设计的集成电路相比常规电路,使得FPGA硬核处理器系统的能耗比率降低29.5%。

4 总结

本文提出FPGA硬核处理器系统的数字化集成电路设计,基于电路整体设计、数字化集成电路设计,完成了提出的电路设计。实验证明,本文设计的集成电路,能够降低PGA硬核处理器系统功耗,提高工作效率。

参考文献:

[1]李冰,周岑军,陈帅,等.用于SRAM PUFs的伪随机数发生器的FPGA实现[J].电子学报,2017(9).

[2]张琳,梅雪松,陈勇.基于SoCFPGA的光伏电力通信管理机系统[J].电子技术应用,2018.

[3]李正杰,张英.一种千万门FPGA芯片中DSP硬核的设计[J].微电子学,2018,48,276(04):60-65.

作者简介:王肖巍(1977-),男,汉族,陕西乾县人,硕士,工程师,研究方向:集成电路设计。