基于VHDL 语言的数字电子时钟设计

2019-09-07马宁刘佳辉谭月洁河北农业大学

马宁 刘佳辉 谭月洁 河北农业大学

引言

数字电子时钟是典型的时序逻辑电路,在日常生活中有着广泛的作用。拿VHDL 硬件编程语言实现数字电子时钟的设计,相比于其他设计实现途径来说可移植性强,易于共享和复用,有更大的借鉴实用价值。

一、总体实现方案

分别将各功能模块:分频模块,计时模块,报时模块,扫描译码显示模块单独写出,编译仿真之后生成对应的模块的模拟元件,将模拟元件作为底层文件放在一个文件夹里,用元件例化component 语句编写数字钟整体系统。

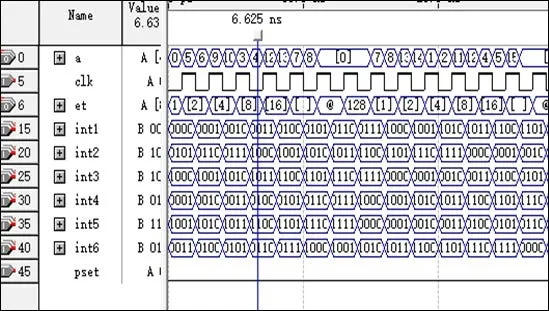

1.分频模块:为了得到1HZ 的秒信号的输入,需要对输出信号进行分频,实现分频器的电路是计数器电路(采用多级二进制计数器实现),采用的是100 倍分频,经过三次分频即可得到1s 的时钟信号。

2.计时模块:计时模块由三部分组成:秒计时器、分计时器和时计时器。秒、分计时器采用的六十进制计数器,小时计时器采用的二十四进制计数器,将计数器输入输出端逻辑相连即可构成秒、分、时的计数,实现计时功能的进制计数器。秒脉冲信号通过计数器,可分别得到秒的个位、十位,分的个位、十位,以及时的个位、十位的计时。60 秒为1 分,60 分为1 小时,24 小时为一天的计数周期。

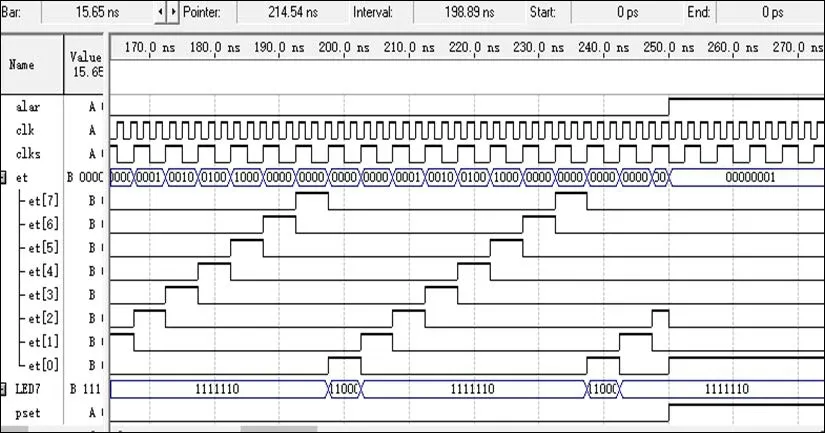

3.报时模块:报时模块的功能是当整点时即将min 作为模块的输入信号,min1=00,min2=00 时,alarm 输出高电平,并且持续一分钟。alarm 在0 分时输出高电平,并且持续至min 的值不为0。

4.扫描译码显示模块:将数字钟的和计时状态直观清晰的通过数码管反应出来。

5.整体设计:将以上模块作为底层文件,并用原件例化语句编写顶层设计的程序,通过 PORT MAP 语句将各模块对应的引脚正确连接起来。

二、设计仿真结果图

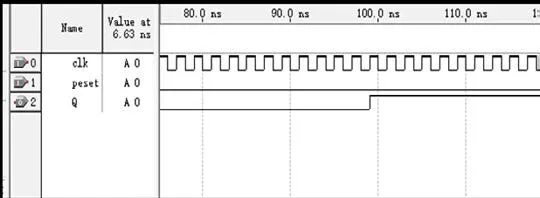

2.1 分频器:

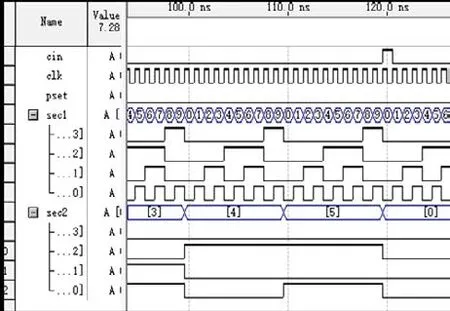

2.2 秒计时器

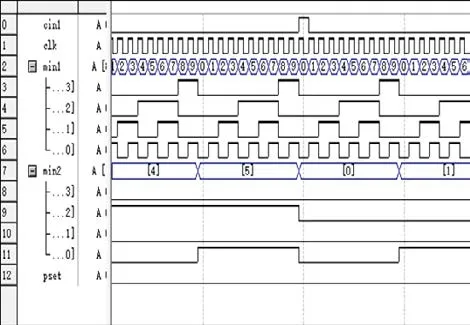

2.3 分计时器

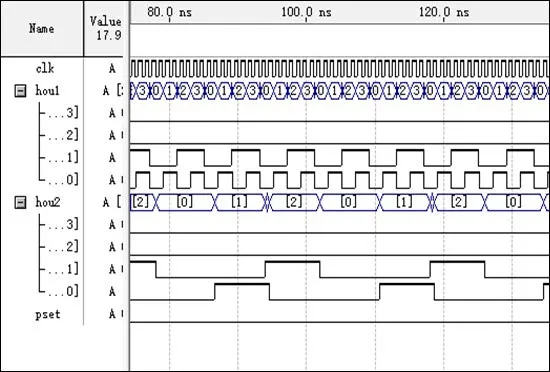

2.4 时计时器

2.5. 报时模块

2.6. 扫描模块

2.7. 译码显示模块

2.8. 数字钟系统设计模块

三、总结

本电子时钟的设计拿VHDL 语言成功的实现了计时功能,重置时间功能,清零功能以及整点报时的功能,但在功能实现上仍有需要完善的地方,计时功能还能实现年月日的计时,整点报时功能能继续改进成闹钟功能。但是掌握了设计的原理和基本思路为以后的工作打下了良好的基础,提供了有效参考。