基于国产FPGA的简易千兆以太网交互系统设计*

2019-09-03于东英王才能

于东英,王才能,张 磊

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

2015年5月国务院印发《中国制造2025》,是全面提升中国制造业发展质量和水平的重大战略部署。2018年上半年美国商务部发布对中兴通信的禁止出口令。2019年5月,美国政府宣布将华为列入“实体清单”。

一系类事件告诉我们,每个人应该树立起各个关键领域应该具有自主可控的研发能力和产品的意识。对于我们电子通信从业者来说,芯片是我们的基础,是我们表演的舞台,必须加大力气和精力来发展与支持国产芯片建立全产业链、增强其应用实践。否则,就会面临随时受制于人的被动局面,使自己处于危险的境地。

由于电子通信行业的高速发展,对数据传输的速率要求越来越高,千兆以太网口已经成为通信设计中较常见的传输接口。在通信设计中,经常采用的千兆以太网接口处理芯片和交换芯片以进口芯片为主。而本文在国产FPGA平台上实现简易的千兆以太网接口数据交互系统的设计与验证。摆脱了对进口芯片的依赖。

1 国产FPGA平台

本文采用的国产平台为深圳市紫光同创电子有限公司提供的采用了完全自主产权体系结构和主流的40 nm工艺高性能FPGA(PGT180H)[1]。此外,针对该芯片公司提供了自主开发套件。

该芯片逻辑资源丰富,并且内置了数据传输速率高达6.375 Gb/s高速串行接口模块,即HSST(High Speed Serial Transceiver)。此外,HSST还集成了丰富的物理层协议配置功能,可灵活应用于各种串行协议标准。该芯片具有3组HSST接口,每组支持四个全双工收发通道,以满足不同用户的对高速串行接口的需求。

在IP core 方面,作者主要采用了厂家提供的基于IEEE802.3-2012标准设计的SGMII 1GbE IP[2](简称SGMII core)和IEEE 802.3-2005标准设计的 10/100/1000M Ethernet MAC[3](简称 MAC core)用于实现千兆以太网口SGMII接口模式下的数据接收和发送。

2 协议简介

本文实现的千兆以太网数据交换的简易系统,遵循TCP/IP协议和以太网的正式标准IEEE 802。

TCP/IP协议族划分为5层包括物理层、数据链路层、网络层、运输层和应用层[4]。

本文主要涉及到的协议或数据传输结构包括以太网帧结构、网际协议、Internet控制报文协议(Internet Control Message Protocol,ICMP)、地址解析协议(Address Resolution Protocol,ARP)、反向地址转换协议(Reverse Address Resolution Protocol,RARP)、传输控制协议 (Transmission Control Protocol,TCP)与户数据报协议(User Datagram Protocol,UDP)等协议结构。

由于网际协议、ICMP、ARP、RARP、TCP与UDP等协议及其数据传输结构现在已经比较成熟,在本文就不在进行详述。

3 逻辑设计与实现

本文在国产FPGA内置的高速串行接口模块HSST的硬件基础上,通过使用厂家提供的SGMII core与MAC core,实现SGMII接口的数据收发,并对接收到的数据进行简单的协议判断和区分,实现3路千兆以太网口之间的高速数据传输与交互。

3.1 设计方案

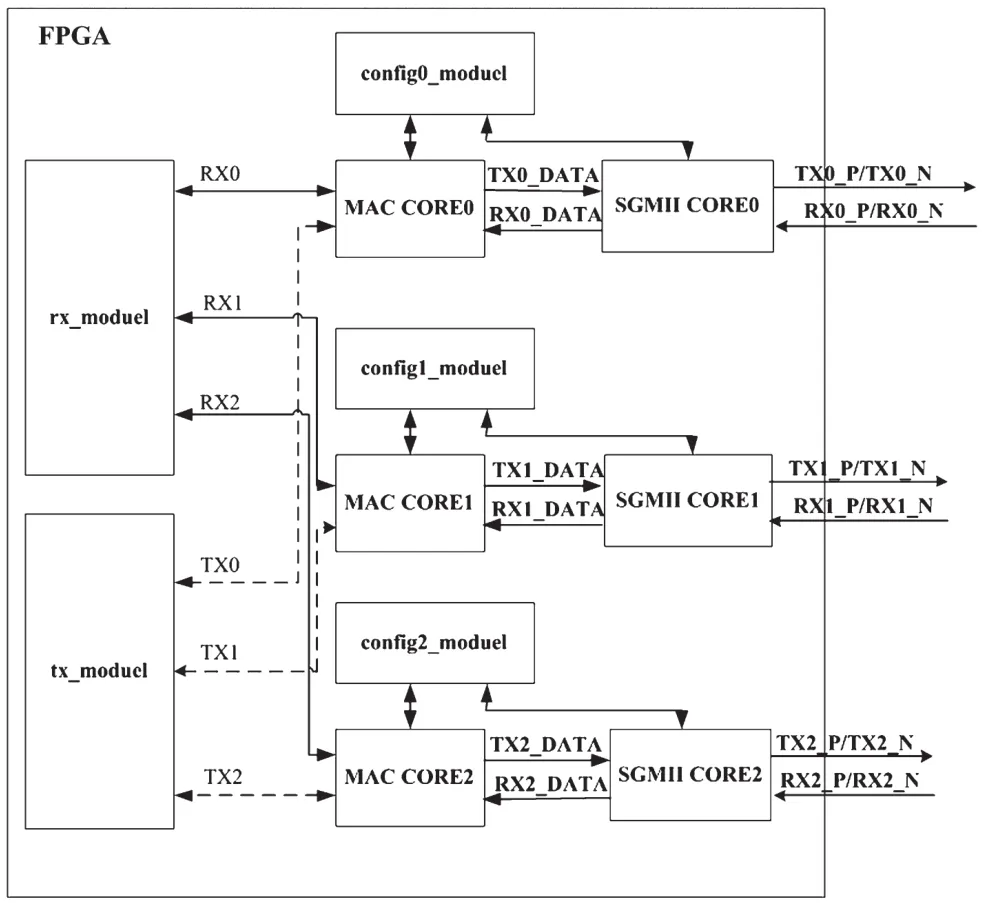

本文以三路千兆以太网为例,设计了该数据交互系统,主要包括4个部分:SGMII core与MAC core组成的以太网网口收发链路、config_module、rx_module与tx_module。各个模块之间的互联关系如图1所示。

SGMII core:用于对HSST接口的配置,实现以太网SGMII接口。其工作模式有4种,包括SGMII模式、GE模式、Both GE and SGMII 模式和LoopBack模式。在本文的设计中选用的是SGMII模式。

MAC core:用于实现以太网的MAC层协议。速率配置为10/100/1000 Mbps自适应,自动填充CRC校验以及全双工使能模式。

config_modul模块:用于对SGMII core与MAC core的使用模式以及速率等特性进行设置。

图1 FPGA内部设计

rx_module模块:该模块的功能是将通过SGMII core与MAC core接收到的数据依此存储到FIFO组内,并按照传输数据涉及到的协议,将所需的重要信息(如数据长度,目的IP,源IP以及该帧数据遵从的协议等)提取出来,写入到与FIFO编号相对应地址的SDRAM内。

tx_module模块:该模块的功能是依此读取SDRAM内各个地址上所存储的信息,并依据这些信息将对应编号FIFO内的数据按照MAC core用户侧时序的要求发送到相应的以太网收发链路上。

3.2 数据交互流程设计细节

本文以以太网口0向以太网口1和2发送数据为例,描述该交互系统的数据处理流程。

三个网口是否通过PHY芯片与外部交互,MAC core可以通过config_modul模块来进行设置以满足用户的需求,在本文中所采用验证系统是将FPGA输出的SGMII接口差分对与外部的PHY芯片对接。千兆以太网数据交互流图如图2所示。

图2 千兆以太网数据交互流图

外部网口0输入数据后,经过SGMII core0与MAC core0的处理后生成8 bit宽度的数据流RXD0,该数据通过rx_logic_module进程中的内部状态机的判断,写入到FPGA内部例化的相应的第X(0≤X≤n)个fifo内(备注:三个网口接收到的数据根据状态机的判断,通过开始接收到数据的先后顺序依次写入到FPGA内例化的n个fifo内,默认从第0个fifo开始写入,依次循环写入)。在接收数据的同时,解析传输数据所遵从的各个通信协议,将数据长度、目的地址、源地址、目的IP,源IP、协议类型等所需要的有用信息拼接起来写入到SDRAM的第X个地址上(备注:SDRAM的数据拼接内容和宽度可以依据需求进行灵活变更)。

在本文示例中,接收到的数据遵从ARP与RARP协议时,数据长度默认为有效数据长度60字节加14字节的以太网帧头,且只提取目的地址、源地址与协议类型等有效信息。其他协议类型均是依据协议格式提取数据长度、目的地址、源地址、目的IP,源IP、协议类型等所需要的有用信息。

当tx_module模块中的logic_module进程依据MAC core用户侧时序将第Y(0≤Y≤n)个fifo内的数据发送完成时,发送状态机将处于空闲状态,此时tx_logice_module模块中的读取fifo的状态机将会去读取SDRAM第Y+1个地址内存储的信息,依据该信息判断第Y+1个fifo内的数据将发送到网口1或者网口2内。Logic_module进程中发送数据时用户侧需要满足的时序要求参见MAC core的用户手册。tx_module模块读取fifo内的数据时,默认是从第0个fifo开始读取,依次循环读取数据。

3.3 验证结果

本文将3个电脑终端通过3根网线连接到两块搭载有xilinx的XC7Z100芯片的测试板上,测试板通过连接器与搭载有国产FPGA(PGT180H)上的SGMII网口连接。两块测试板上的3个网口通过搭载有国产FPGA的板卡进行网口数据交互,进而取代交换芯片。

验证过程主要是通过其中一台电脑终端通过串口助手发送网口之间的ping指令,并收到对端的响应,显示网口之间ping成功。在实际验证环境中,设置一台电脑的IP地址为192.168.3.6,另一台电脑的IP地址为192.168.3.1。由IP地址为192.168.3.6的电脑发起对地址为192.168.3.1的ping指令,不间断进行20次,结果显示全部ping通。

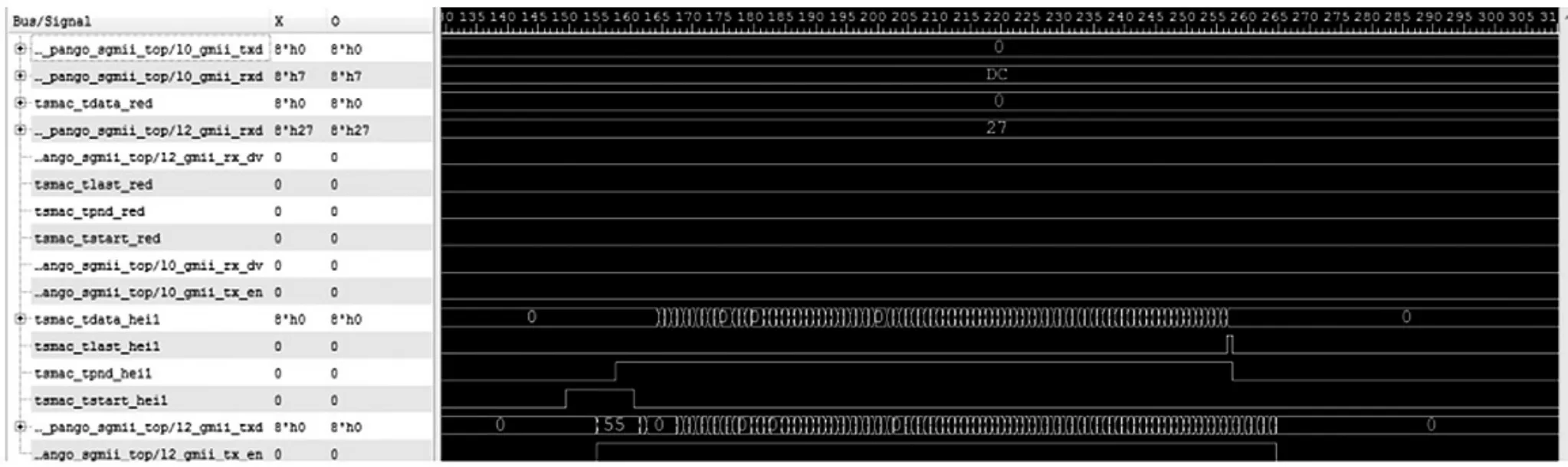

此外为了验证TCP、UDP等协议,还通过网口进行了几十M大小的文件传输,传输过程中的SGMII core与MAC core用户侧的时序如图3所示。

图3 发送、接收时序图

通过验证我们发现,该系统可以进行网口的ping指令以及在不同网口之间进行正确的文件传输,证明了国产FPGA实现的千兆以太网口简易交互系统的稳定性和正确性。

4 结 语

在目前的国际形势下,重要芯片的国产化势在必行,千兆以太网口作为成熟的高速处理接口已经被广泛应用在各个领域,不可避免涉及到的网口之间的数据交互。本文在国产FPGA的平台上,通过国内自主研发的SGMII core与MAC core实现了千兆以太网口的设计以及网口之间的数据交互系统设计,并通过了传输大量数据来验证其稳定性和正确性。其可以广泛应用于需要网口的小系统设计和具有多个网口的板间设计,进而取代与网口数据交互相关的进口芯片的依赖。