基于FPGA 的极化码交织器设计与实现

2019-07-22向明尚张志华潘丽艳

向明尚,张志华,潘丽艳

(东北石油大学,黑龙江 大庆 163318)

1 引言

Pοlar码是基于信道极化现象提出的一种编码方案[1],在设计时并没有考虑码距特性,而是利用了信道联合与信道分裂的过程来选择具体的编码方案[2],是目前理论上证明唯一可以达到香浓极限[3]传输的信道编码方案,已被3GPP选为5G eMBB场景控制信道编码标准。

随着5G技术逐步走向商用,在移动通信过程中对信息安全、可靠的传输要求越来越高。为保证信息的可靠传输,需要用到各种编码技术来纠正信道中产生的随机错误。当传输过程中产生突发性的干扰,用纠错编码理论和技术进行纠错需要很长的码字,增加了复杂度且延时较长。交织技术与纠错编译码技术相结合,可以把突发错误离散成随机错误,在随机错误状态进行译码纠错,可取得良好的效果[4],使突发错误引起的码字个数在规定的安全范围内。交织编码主要应用于有记忆信道,特别是无线信道,以此来纠正成串发生的比特差错和一些突发错误[5]。发送端加上交织器,接收端接收到交织后的信息后,按照一定的规律进行解交织,即可还原信息。

极化码具有很好的误码性能并且速率兼容性能优良[5],与交织器和解交织器配合,既可以纠正信道传输中的随机错误,也可以纠正突发错误。交织与解交织过程是信道纠错的一个非常重要环节,本文利用Altera公司开发的Quartus软件仿真环境,基于FPGA设计实现了交织器电路。

2 交织模式的确定

交织是通信系统中进行数据处理而采用的一种技术,交织从其本质上来说是一种实现最大限度改变信息结构而不改变信息内容的技术[6]。极化码采用统一的交织方法和结构,即给出了统一的交织模式,是根据交织器最大输入信息比特数Kmax得到的,它是一种根据信道的状态信息进行符号调整的自适应交织方法[7]。最大信息比特数包括传输的原始信息位和添加的CRC校验位,共计164位,构成了循环冗余校验码,其中CRC校验位为24位,添加在原始信息比特的后面。即发送信息中添加了冗余码,使信息传输的开销增大了,但却可以进行差错检测和纠错[8]。添加CRC校验位长度为K的信息表示为:c0,c1,c2,c3,…,cK-1是加入到交织器的输入序列,是经过交织器交织的输出序列,它们之间满足下列关系:是子交织模式。当输入信息序列长度小于最大输入信息比特数时,可以通过下列算法得到子交织模式。

当K的取值不同时,得到的子交织模式各不相同。例如K=50时,可以得到的一种子交织模式,如表1所示。其中m取值为0~49,是加入到交织器输入序列共计50个信息比特的原始比特顺序。Π的值也是0~49,但它是离散的,是经过交织器交织后输出序列对应的信息比特顺序。如m=9表示原始信息比特在输入序列中的第9位上,与其对应Π=18,表示交织后原始信息比特在输出序列中第18位上。

子交织模式如表1所示。当m≥29时,交织器输出的信息比特顺序与交织前信息比特顺序一致,并没有做交织处理。如果在这些连续的比特位传输过程中发生连续的突发性错误,是否会降低编码的可靠性?回答是否定的。因为加入到交织器输入序列的后24位是CRC校验码,可以得到修正。

表1 子交织模式(K=50)

3 交织器电路设计

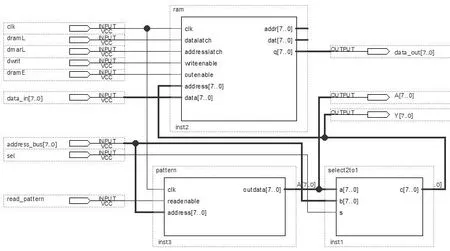

图1 交织器设计原理图

3.1 交织模式存储器设计

交织模式存储器设计利用ROM元件实现,地址线8位,数据线8位,存储单元256个,每个单元可存储一个8位二进制数。其中0~163连续的164个单元存储交织模式数据它事先保存在数据文件中,作为存储器配置文件在设计存储器时提供。

数据文件的内容取决于输入信息比特位数K,对应不同的子交织模式Π(k)。当K的值确定后,Π(k)及其数据文件都是固定不变且唯一,只能完成K个比特数据的交织工作,K变化时需要修改模式数据文件,并且需要重新配置模式存储器,即可实现交织操作。

3.2 数据存储器设计

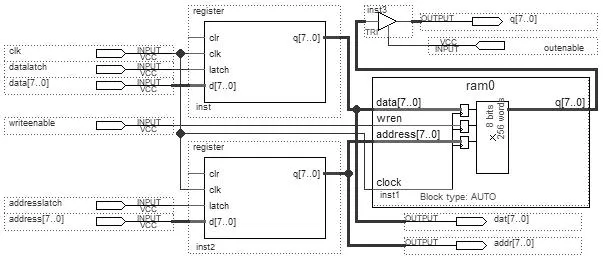

数据存储器设计,利用RAM元件实现,如图2所示。

图2 数据存储器原理图

地址线8位,数据线8位,存储单元256个,每个单元可存储一个8位的二进制数。其中,0~163连续164个单元,用于连续存储加入到交织器的输入序列,即等待交织的二进制信息比特数据,其长度K=164,即按照交织模式进行数据交织。

由于输入的信息比特是二进制数,所以RAM的每个存储单元只需保存1位二进制数据即可,也就是说其数据线只需要1位。而这里设计RAM时数据线用了8位,目的是在仿真测试时,可以使用十进制数0~163作为信息输入,连续存入数据存储器的存储单元中,经过交织后输出的是按交织模式离散的十进制数,方便观察交织器的输出情况,并与输入序列作对比,有助于判断交织器的工作是否正确。

3.3 数据选择器设计

数据选择器的设计利用硬件描述语言编程实现,完成地址二选一功能。在进行交织操作前,数据选择器选择连续地址0~163作为输入,并按此顺序输出且作为地址提供给数据存储器RAM,指向RAM连续的164个存储单元。当需要交织输出数据时,由交织模式存储器输出离散的模式数据,作为数据选择器的输入,经选择器选中输出且作为地址提供给数据存储器RAM,指向RAM的对应存储单元。

3.4 交织器工作流程

3.4.1 待交织数据的存储实现

如图1所示,加入到交织器等待交织的连续数据0~163,通过数据总线依次加到数据存储器RAM的数据输入端data_in,同时由地址总线address_bus依次给出连续的地址数据0~163,经过选择器加到数据存储器RAM的地址端,指向RAM连续的0~163个存储单元,在写信号和时钟作用下,将待交织数据按信息比特顺序存入数据存储器RAM连续的存储单元中。

3.4.2 交织过程的实现

由地址总线address_bus给出连续的地址0~163,加到模式存储器pattern的地址输入端,在读信号和时钟作用下读出模式数据加入到数据选择器。经选择器输出加到数据存储器RAM的地址端,在读信号和时钟作用下读出数据存储器的数据,即可完成交织过程。

4 仿真结果分析

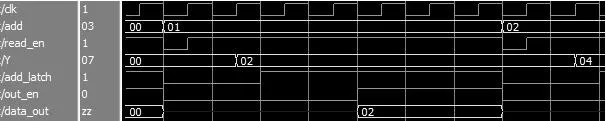

测试数据为0~163连续的十进制数据,作为输入序列加入到交织器的数据输入端,经交织器交织后输出,通过输出波形图观察验证交织器的工作情况。

4.1 信息比特的输入与存储

等待交织的信息比特测试数据存入到交织器的数据存储器中,这里用十进制数代表二进制信息比特,如图3所示。图3中add是0~163个连续的存储器地址,add_latch为地址寄存器锁存信号。

data_in为输入的0~163个待交织的信息比特数据,data_latch为数据寄存器锁存信号。data_write为写信号,在时钟信号clk配合下,将连续的待交织信息比特数据依次写入数据存储器0~163个存储单元中。

图3 交织器数据输入波形图

4.2 交织器输出验证

经过上一步操作,输入信息比特数据已经写入交织器数据存储器,在此通过输出操作来验证数据存储是否正确,如图4所示。add为模式存储器的连续地址0~163,read_en为模式存储器读出信号,Y为模式存储器的输出,即为交织模式的数据。果,也是交织模式的数据。

图4 交织器交织结果输出波形图

Y的输出数据是离散的交织模式数据,由add_latch信号锁存,作为数据存储器的地址,指向数据存储器离散的存储单元,当clk和οut_en信号有效时,data_οut输出交织结

5 结语

交织器是极化码编码过程中的重要一环,它的质量直接影响到5G控制信道短码传输效率。通过交织器电路的验证,得到了与交织模式完全一样的输出序列信号,表明交织电路设计正确。交织器的设计方法及实现电路,可以满足信息传输的可靠性和工作效率的要求。