一种通用信号处理模块设计

2019-07-20谢伟

谢 伟

(中国电子科技集团公司第十研究所,成都 610036)

传统的电子系统设备中,各功能都是以分离式的设备完成其相应的功能,而现在的电子系统设备大多都是将多个功能作为整体进行设计,其特点就是软硬件模块化、通用化,达到降低成本、缩短研制周期的目的,本文介绍了一种通用信号处理模块的设计方法。

1 总体设计

本设计以DSP作为处理器,DSP与FPGA协同工作,完成系统中频及基带信号的处理,模块FPGA和DSP程序代码可动态加载,根据主机任务需要实时配置成不同功能。同时具备FPGA和DSP代码在线更新功能。模块框图如图1所示。

图1 模块设计框图

模块主要由DSP、FPGA、LVDS高速串行总线接口组成。DSP和FPGA功能程序加载正确后,模块的处理通道根据系统配置执行数字接收或者发送流程。在数字接收流程中,FPGA接收通过LVDS高速串行总线传来的AD数据,经过处理后传给DSP进行进一步处理,同时通过离散线接口和RapidIO总线接口和信道等单元交换控制参数,最终的处理结果由DSP通过RapidIO接口传送系统。数字发送流程和接收流程相反。待处理的基带信号由整机通过RapidIO接口送给信号处理模块。DSP和FPGA对基带信号进行处理后,通过LVDS高速串行总线发送给信道激励模块。

主机通过RapidIO总线下传新版本程序进行FPGA和DSP代码在线更新。主机在需要对信号处理模块进行功能重构时,通过RapidIO总线向DSP发送功能重构指令。

2 硬件与软件设计

2.1 LVDS高速串行总线接口电路设计

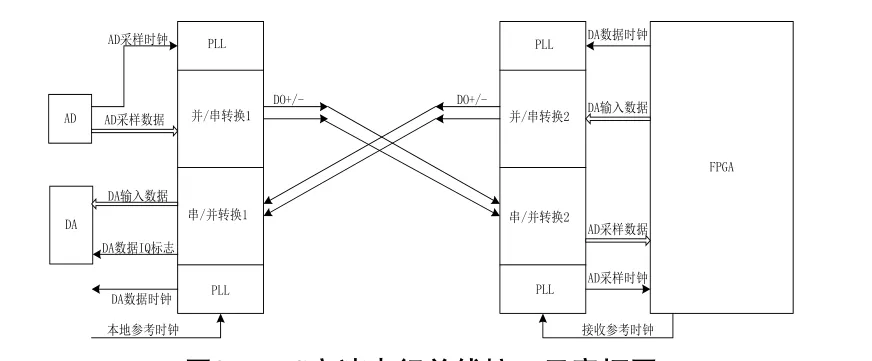

数字接收和发送流程是各功能算法对中频信号的解调过程和对发送基带信号的调制过程,LVDS高速串行总线接口用来传输AD/DA数据,其连接示意框图见图2。

图2 LVDS高速串行总线接口示意框图

AD采样数据和采样时钟按照图3所示时序送入信道模块并/串转换的同步并行数据输入端,就会获得如图3所示的串行数据输出Do。Do信号传送到信号预处理模块的某个接收通道串行输入端。信号处理模块产生和AD采样频率相同的时钟信号送给该处理通道FPGA,FPGA将该时钟信号作为本地参考时钟输入到串/并转换的锁相环,获得如图4Rout所示的并行数据输出。DA数据的发送和AD数据的接收流程相似,传输方向相反。

图3 数据发送时序

图4 数据接收时序

2.2 程序在线更新设计

主机通过RapiIO总线向信号处理模块DSP发送功能程序烧写指令,并将需要更新的程序数据发送给模块DSP。DSP收到功能程序烧写指令后立即停止当前运行的程序,跳转到底层管理程序,并开始执行底层管理程序。底层管理程序接收主机传来的新程序,解析功能程序烧写指令,然后将新版本程序固化到非易失性存储芯片中相应的地址处,覆盖原来的程序。功能程序更新流程框图如图5所示。

图5 FLASH程序更新流程框图

2.3 FPGA程序加载设计

FPGA上电后不能自行加载程序,要等到DSP运行底层管理程序时才开始加载FPGA程序。DSP底层管理程序通过外部存储器接口总线从非易失性存储芯片中读出FPGA程序,接口控制CPLD实现DSP外部存储器接口总线和FPGA加载端口的接口适配逻辑,然后通过接口控制CPLD写入FPGA配置端口。DSP和FPGA加载端口之间接口电路原理如图6所示。

图6 DSP和FPGA加载端口之间接口电路原理图

2.4 DSP程序加载设计

上电完成后,当DSP锁相环稳定工作,DSP将立即启动上电自举流程。DSP上电自举流程分下述三个步骤进行:首先进行底层引导程序加载,然后加载DSP底层管理程序,底层管理程序主要完成模块硬件初始化、上电后程序加载、处理通道功能重构以及功能程序在线更新等任务,最后加载用户功能程序。

3 结束语

本文介绍了一种信号处理模块的硬件电路及软件设计,能够方便的实现应用程序的动态加载和代码更新,开发者可以灵活的选择DSP与FPGA的型号来实现功能。