基于淘汰判决的跳频同步捕获方案设计

2019-06-25赵祥武全厚德崔佩璋

赵祥武,全厚德,崔佩璋

(陆军工程大学石家庄校区 电子与光学工程系,河北 石家庄 050003)

0 引言

同步技术是跳频系统的关键,传统同步方案一般都利用跳频同步引导码完成跳频同步的工作,随着电子通信的不断发展,敌方干扰越来越“聪明”,干扰方可以通过捕获一些跳频的通信参数来进行更为精确的干扰,比如跟踪干扰,干扰方在干扰一段时间之后,可以通过分析得到信号时频域的特征信息,从而精确干扰,使得跳频通信无法正常进行。

高跳速下通信系统的同步技术是同步技术发展方向之一。文献[1]提到,目前高跳速电台应用较多的是时间信息(Time of Day,TOD)和同步头联合应用的一种策略,该方法是跳频信号前端将时间信息填入,方便进行同步识别,接收机通过将接收到信息进行捕获,从而调节伪随机码发生器,完成信息的正常通信。由于这种策略一旦被敌方发现,很难进行通信。文献[2]提出了门限比较的同步策略,在高速的跳频通信中具有性能的优势。随着跳频通信发展,差分跳频作为抗干扰较好的通信方式,是今后重要的发展方向。同步性能也直接影响差分跳频的系统。文献[3]中,同步技术主要使用的是信号的FFT检测,该方法是对数字信号进行FFT的时频分析,根据跳频信号能量的遍布情况,从而得到跳频同步信息,完成同步过程。文献[4]提到跳扩混合系统的关键是跳频同步和快速实现扩频序列的捕获。该方法是基于时间信息与同步头的直接序列扩频编码方法,可以很好地增强同步方法应对干扰的能力。文献[5]提到一种基于滑动相关的自适应同步捕获策略,可以迅速完成正常通信。

跳频同步主要包括3个方面:同步捕获、同步跟踪以及同步保持[6]。同步捕获是一个粗略的同步过程,也是最需要首先解决的问题,主要解决的问题是收发两端时间误差控制在一个允许的范围内,一般取1/2跳频序列的相位;同步跟踪是一个精确同步的过程,使接收端与发射端的时间误差在原来捕获的基础上再尽可能缩小,更细小的相位差的修正需要同步跟踪来完成。跳频通信系统中同步跟踪方法是通过锁相环技术来实现的,常见的跟踪过程方法有2种:基于抖动锁相环和基于延迟锁相环[7-9]。

本文主要对自同步方法中串行同步捕获方案和并行同步捕获方案进行具体的研究分析,针对2种同步捕获方案的性能优缺点,提出了基于淘汰判决的同步捕获方案,通过在一定范围内的能量检测,快速进行同步判决,节省了同步捕获时间,增强了抗干扰能力。

1 跳频同步捕获方案

1.1 串行自同步捕获方案

跳频通信系统串行搜索捕获方案的原理框图如图1所示[10]。工作原理是:基于发射端跳频信号与接收端本地伪随机发生器的频率进行相关运算,而后对一个跳频周期内的判决结果作能量比较,根据提前设置的门限电平,如果相关运算后的门限电平没有超过输出电平,这代表着收发两端没有同步,此时搜索控制器控制PN码发生器相位移动,重新进行相关运算;反之,超过输出电平,收发两端已经同步捕获,进而进行同步跟踪,进一步缩小误差。

图1 跳频系统串行捕获原理框图

1.2 并行自同步捕获方案

跳频通信系统并行搜索捕获方案的原理框图如图2所示[11-12]。工作原理是:发射端的跳频信号与接收端信号相关运算后,经过平方检波器,而后进行能量相加求和。如果能量和大于规定的门限电平,就意味着收发两端已经同步。其中,Th是跳频周期,n代表跳频同步的频率数。图2可以看出,S条支路的中心频率按照f1,f2,f3,...,fn的顺序排列,其顺序应与同步引导码的顺序一致。跳频图案按照f1~fn的顺序进行跳变,经过平方检波后依次延迟一个跳频周期;当输入的跳频频率fn进入接收机时,对加法器累加的能量值输出门限判决。如果输出门限值超过规定的门限,即可实现跳频的同步。

图2 跳频系统并行捕获原理框图

从理论上分析,并行自同步捕获方案在捕获时间上较串行自同步捕获方案有很大的优势,就系统复杂度来说,串行自同步捕获方案较为简单。

1.3 基于淘汰判决的自同步捕获方案

图3为淘汰判决自同步捕获系统框图。该方案的中心思想是同步过程中在Q个频点内通过门限判决结果快速做出相应的处理,如果在Q个频点内相关的能量检测结果明显小于规定门限值,意味着跳频信号没有同步,直接将接收机本地跳频信号序列淘汰,经过跳频序列相位移动后,再开始同步,经过混频、滤波及门限判决等一系列操作,然后再进行出局判决,跟并行自同步捕获方案一样,一个跳频周期内的相关判决直接决定着同步是否成功。

图3 淘汰判决自同步捕获系统框图

2 性能分析

2.1 系统复杂度

就系统复杂度而言,根据3种捕获方案的设计模型可以很清晰地看出:串行自同步捕获方案只需一路由混频、带通滤波、包络检波以及门限判决模块构成的支路,而并行自同步捕获方案则需S路相关支路,所以相比于并行自同步捕获方案,串行自同步捕获方案系统设计简单,得到很好的应用而淘汰判决的自同步捕获方案,相较于串行自同步捕获方案,只是快速淘汰判决模块以及搜索控制模块,系统复杂度不高[13]。

2.2 抗干扰性能

假定跳频序列进行同步需要n个不同频率,即跳频序列长度是n,跳频频率间隔为T0,假设捕获方案在第k频点实现同步捕获。

并行自同步捕获方案捕获成功的概率表示为:

(1)

串行自同步捕获方案捕获成功的概率表示为:

(2)

在无干扰存在时,基于淘汰判决捕获方案捕获成功的概率表示为:

(3)

就抗干扰性能而言,串行自同步捕获方案和并行自同步捕获方案都是对于一个周期内的相关检测结果进行门限判决,对于使用相同长度的跳频序列,判决门限相同时,2种方法抗干扰性能相同,都具有很好的抗干扰能力。

抗干扰性的主要指标是虚警概率和漏捕概率,淘汰判决自同步方案是根据淘汰判决模块的控制,跟串行自同步捕获方案比较,不会增加虚警概率。所以,重点研究该同步方案的漏捕概率。本节选择的干扰模型为单频干扰,假设存在F=αn个单频干扰,定义每个频点的出现干扰概率为α。假定在某频率间隔内,检测到幅度为A的有用跳频信号,干扰幅度为Ai,A与Ai之间的夹角为θ,而且θ均匀分布在[0,2Π]上,则有用信号与干扰信号的幅度可以写为:

(4)

在相关检测后,判决门限电平为A1,此时如果A1>Av,就会造成频率漏捕,即

(5)

此时可以得到频点的漏检概率:

(6)

如果存在R个以上的跳频频点出现漏检时,同步方案漏检的概率为:

(7)

经过以上分析可知,淘汰判决自同步捕获方案和串行自同步捕获方案相比,判决模块会出现错误判决,从而使得漏检概率增加,需要对Q取值大小进行约束。

当连续漏检的频点数目是Q时,总的漏检个数小于R的概率为:

(8)

当连续漏检的频点数目是Q+1时,总的漏检个数小于R的概率为:

(9)

当连续漏检的频点数目是Q时,系统漏捕获概率为δQ=1/n;

当连续漏检的频点数目是Q+1时,系统漏捕获概率为δQ+1=2/n。相较于串行自同步捕获方案,淘汰判决自同步捕获方案的漏捕概率增量为:

(10)

2.3 平均捕获期望

串行捕获方案捕获时间的期望[14]:

(11)

并行捕获方案捕获时间的期望[15]:

(12)

基于淘汰判决的捕获方案捕获时间的期望:

(13)

根据式(11)~式(13)分析可知,基于淘汰判决的自同步方案捕获时间期望远远不及串行自同步捕获方案的捕获时间期望,同时,仅当依据对一个频点能否进行同步捕获而进行相位判决时,即当Q=1时,淘汰判决自同步方案的捕获时间与并行自同步捕获方案相同,使得捕获时间最小。

3 仿真结果分析

3.1 捕获时间仿真分析

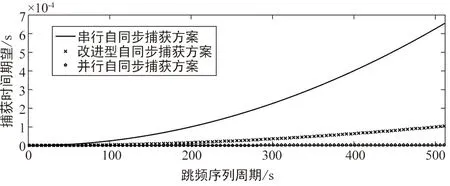

考虑在无干扰环境中,设定Q=0.3n,跳频长度n取值范围为0~512,通过Matlab仿真计算,得到串行自同步捕获方案、并行自同步捕获方案和淘汰判决自同步捕获方案。3种方案捕获时间期望的对比曲线如图4所示。

从图4的仿真结果可以看出,淘汰判决自同步捕获方案的捕获时间相比于串行自同步捕获方案的捕获时间有了较高的提升,在Q=0.3n时,捕获时间约为串行自同步捕获方案的1/5。

图4 改进方法与经典方法的性能对比曲线

3.2 参数Q的大小对捕获性能的影响分析

在n=256,α=0.2,P=0.15的取值状态下,设定R=n·(α+P)/2,漏捕概率增量与Q的仿真结果如图5所示,其中Q的取值大小设定(0.5R,R)。

从图5中可以看出,淘汰判决自同步捕获方案的漏捕概率增量仅仅是10~11数量级,当Q/R≥0.66时,漏捕概率增量达到最小,在实际的跳频电台中可以忽略,参数Q的大小主要是由捕获时间以及抗干扰性进行综合选择。Q过大时捕获时间增加,Q过小时抗干扰性能不达标。通过多次计算机仿真结果,当参数取Q=0.66R左右时,跳频通信具有很高的抗干扰性能,同时也满足捕获时间的要求。

图5 漏捕获概率增加量与Q值的关系曲线

4 结束语

从系统复杂度、捕获时间以及抗干扰性能这3个方面对串行自同步捕获方案、并行自同步捕获方案和基于淘汰判决自同步捕获方案进行了详细的分析与对比,串行自同步捕获方案捕获时间最长,并行自同步捕获方案捕获时间最短,串行与并行自同步捕获方案的抗干扰性能相同,在一定条件下优于淘汰判决自同步方案。但是,当淘汰判决自同步捕获方案取得适当的淘汰参数Q时,既可以保证抗干扰性能,也能保证捕获时间的最佳。