AD9832芯片在10.24 MHz频率变换器中的应用*

2019-06-14张晓华王群颖王卫国李娟

张晓华,王群颖,王卫国,李娟

(1.武警湖北总队,武汉 430062;2.武汉船用电力推进装置研究所,武汉 430064;3.武警后勤学院基础部,天津 300361;4.中国人民武装警察部队警官学院,成都 610213)

0 引言

随着数字电路的普及,锁相环电路得到了大量的应用。由其鉴频工作原理可知,其输入参考源信号的准确度和稳定度直接影响锁相环电路输出信号的精度。

在MC145152锁相环芯片[1]应用中,输入参考源信号须通过内置R分频器预分频后才能作为鉴相参考频率,R分频器的分频系数可选8,128,256,512,1 024,2 048,2 410,8 192其中之一。以常用10 MHz信号作为输入参考源信号时,由于通过R分频器后无法整除得到10的整数倍鉴相参考频率,因而选取10 MHz信号并不适合。经过计算,当选择2NMHz如2.048 MHz信号作为输入参考源信号时,可以整除得到10的整数倍鉴相参考频率。在本应用中选取10.24 MHz作为输入参考源信号,R分频器的分频系数选1 024,鉴相参考信号为10 kHz。

MC145152锁相环芯片得到10.24 MHz输入参考源信号有两种方式,方式一是将10.24 MHz晶体外接于芯片OSC1和OSC2管脚,通过其内部振荡电路生成10.24 MHz信号,经1 024分频后作为锁相环鉴相参考频率。但普通石英晶体振荡器只能达到10-5的频率稳定度,在采用优质石英晶体、恒温控制等措施后,虽能达到10-11的频率稳定度,但因为成本或功耗等原因导致很少使用。方式二是将10.24 MHz信号外接于芯片OSC1管脚作为输入参考源信号,通过1 024预分频后同样能够得到10 kHz锁相环鉴相参考频率。当10.24 MHz外接信号频率稳定度达到10-11以上时,MC145152锁相环控制的输出频率就可以达到10-11以上的频率稳定度,使方式二应用于高精度时频领域成为可能。

通过上述描述,应用的核心在于研制出频率稳定度达到10-11以上的10.24 MHz参考源信号。经过研究发现,10.24 MHz信号并不常用,通常都是由高精度的10 MHz信号经过基于直接数字频率合成技术(direct digital frequency synthesis,DDS)的频率变换电路生成。

本文主要介绍一种利用DDS频率变换电路产生10.24 MHz高精度信号的实现方法。该信号作为MC145152锁相环参考源,使锁定输出信号具有较高的稳定度。

1 AD9852芯片实现10.24 MHz频率变换

有文献已针对高精度10 MHz信号经过频率变换电路输出高精度10.24 MHz信号作出介绍[2],它通过FPGA(现场可编程门阵列)+DDS(直接数字频率合成器,如AD9852)实现,在这一方案中,10.24 MHz信号是10 MHz信号经倍频电路后通过DDS器件AD9852直接输出得到。

DDS器件可以精确预置输出频率和相位,应用灵活且易于集成,但由于AD9852器件自身的技术要求所限,存在功耗高、杂散大、不利于电路小型化等缺点。最重要的是,根据Nyquist采样定理,DDS的最高输出频率应小于二分之一fc(输入时钟),实际应用中一般只能达到40%fc。也就是说,上述方案中为直接获得10.24 MHz信号,10 MHz参考信号必须经过至少3倍频后才能作为AD9852器件的输入时钟(要求fc≥30 MHz),因此该方案中倍频电路是必需的。从理论上讲,倍频器将信号频率提高N倍,会让相噪抬高20 log(10N) dB,类似的N分频会让相噪降低20 log(10N) dB。那么,经过计算由3倍频电路所引入的附加相噪为9.5 dB,不容忽视。

2 AD9832芯片实现10.24 MHz频率变换

经过分析不难发现,若以10 MHz作为参考源信号,要得到10.24 MHz信号既可以由10 MHz通过倍频电路经DDS器件直接生成,也可以通过10 MHz信号和0.24 MHz信号混频后获取。其中0.24 MHz信号属于低频信号,10 MHz信号约为0.24 MHz信号的42倍频,按照Nyquist采样定理,10 MHz信号完全可以直接作为DDS器件的输入时钟fc,经过直接数字频率合成后得到0.24 MHz信号。

按照上述思路,只需利用DDS器件生成0.24 MHz信号即可。由于设计需求简化,选用AD9852/AD9854之类功能复杂的DDS器件并不适合。而另一款DDS器件AD9832,既能够以10 MHz直接作为输入时钟,又具有功耗低、调试简便等优点,且通过编程可精确预置输出频率和输出相位,完全能够满足设计需求。以下将具体介绍AD9832器件在10.24 MHz频率变换器中的应用。

2.1 AD9832芯片使用原理介绍

DDS由相位累加器、累加寄存器、波形存储器和D/A转换器构成,外部搭配低通滤波器。图1为工作原理示意图,它利用采样定理,通过查表法产生波形。每接收一个时钟脉冲fc,相位累加器将控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使相位累加器在下一个时钟脉冲fc的作用下继续与频率控制字相加。如此,相位累加器在时钟脉冲fc作用下,不断对频率控制字进行线性相位累加。相位累加器最终输出的数据就是合成信号的相位,用该相位数据作为波形存储器(ROM)的相位取样地址。这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的数据输出到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量信号,配合外部低通滤波器滤除生成的阶梯形正弦波中的高频成分,最终输出频谱纯净的正弦波信号fo。

图1 DDS工作原理图

AD9832芯片同样由相位累加器、累加寄存器、波形存储器和D/A转换器构成,它具有一个10位数模转换器,最高支持25 MHz输入时钟[3],频率控制字寄存器为32位。其输出频率Fout=Mclk×N/232。本文中MCLK为10 MHz参考时钟,N为FOUT输出0.24 MHz时,由MCU控制器写入AD9832频率控制字寄存器中的32位控制字。

将AD9832芯片合成的0.24 MHz与10 MHz信号混频相加后即得到10.24 MHz信号。为了能够满足谐波、相位噪声和稳定度等技术要求,还需增加滤波、匹配、功率放大、隔离输出等电路。设计原理如图2所示。

2.2 AD9832外围硬件电路介绍

按图2的设计原理,频率变换器包含有MCU主控单元电路[4]、AD9832单元电路、混频电路、两级滤波电路、匹配、放大以及隔离输出电路。受篇幅所限,本文仅给出AD9832单元电路、3阶椭圆带通0.24 MHz滤波电路以及混频电路[5]的设计,其余部分从略。图3所示为AD9832单元电路。MCLK即为输入时钟管脚,接10 MHz参考源信号。

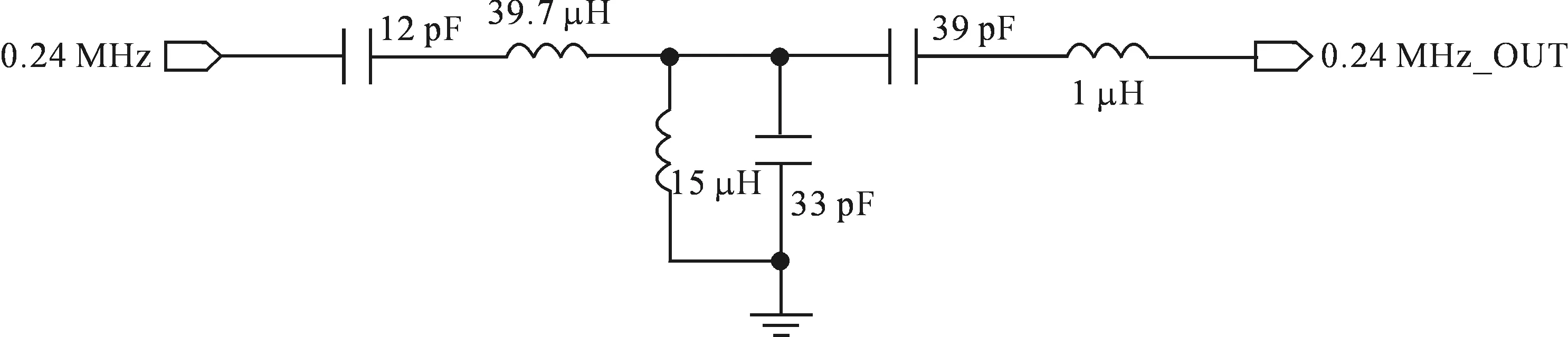

AD9832输出的0.24 MHz由于含有丰富谐波成分,正弦信号呈阶梯波状,必须经过带通滤波器改善幅频、相频特性、滤除带外杂散[2,6]后方可使用。椭圆函数滤波器由于其过渡带很窄、下降迅速,相比其他函数滤波器性能更好[7]。结合设计需求,本文选择3阶椭圆带通滤波器,通频带200 Hz,截止频率为0.25 MHz,配合软件仿真计算,实际电路如图4所示。

图3 AD9832单元电路、滤波电路及混频电路图

图4 3阶椭圆带通滤波电路图

图5为3阶椭圆带通滤波电路前、后波形对比。可见,经过带通滤波器后0.24 MHz信号质量得到明显改善。

图5 3阶椭圆带通滤波前、后波形对比图

图6所示为使用频谱仪监测AD9832的14脚IOUT输出0.24 MHz信号频谱和经3阶椭圆带通滤波器后的0.24 MHz信号输出频谱。

可以看出,直接输出的0.24 MHz信号中含有丰富的高次谐波梳状谱分量,但经过3阶椭圆带通滤波器后,频谱纯度得到明显改善,谐杂波得到明显抑制。

图6 AD9832输出频谱和滤波输出频谱

经3阶椭圆带通滤波后0.24 MHz信号与10 MHz信号的混频是通过54HC86异或门(等同于作加法)得到,如图7所示。其输出为方波,再经过高Q值、窄带通晶体滤波电路[2]和选频放大后最终可获得光滑、频谱纯净的10.24 MHz正弦波信号。

图7 混频电路图

2.3 AD9832器件软件编程

AD9832串行接口SPI时序图如图7所示,根据AD9832芯片寄存器控制字配置时序要求[3],从SDATA口对3个16位功能寄存器依次赋值,串行数据从MSB开始,LSB结束。同步端FCTNC在对功能寄存器操作时拉低生效[8]。SCLK接外部10 MHz参考时钟信号。具体寄存器内容设置可参考芯片手册和编程指南。

对AD9832软件控制流程图如图8所示,编程控制如图9所示。

图8 AD9832串行接口SPI时序图

图9 AD9832软件控制流程图

修改频率控制字N和相位控制字P[6,8-9],就可以灵活修改输出频率和输出相位。

2.4 10.24 MHz信号输出信号频谱分析

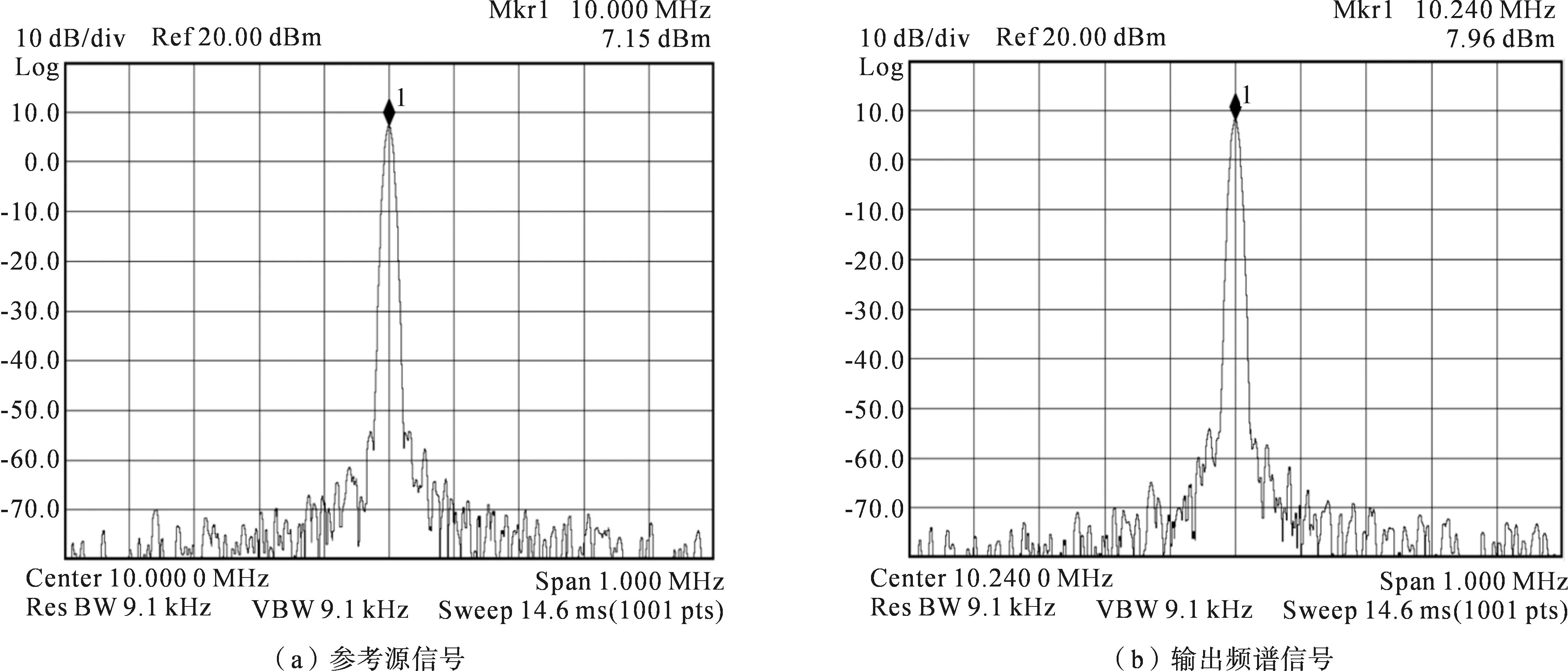

使用频谱仪观测10 MHz参考源信号和最终输出的10.24 MHz频谱信号如图10所示。可见,经高Q值晶体滤波器及选频放大后,10.24 MHz信号和10 MHz参考源信号质量相当,且谐、杂波成分得到了充分的抑制。

图10 10 MHz参考源信号和10.24 MHz输出频谱对比图

表1为10 MHz参考信号通过AD9832无倍频方案和AD9852倍频方案两种频率变换电路分别得到的10.24 MHz信号技术指标对比,对比内容包括信号谐波、功率、相位噪声以及对提升锁相环电路输出频率稳定度的改善程度[6,10-11]。

对比发现,采用0.24 MHz信号与10 MHz信号混频的无倍频设计方案,同样能够得到10.24 MHz信号,并且谐波、相噪指标已经达到(远端)或优于(近端)含有倍频电路的AD9852方案。同时,MC145152锁相环参考源采用频率变换器方案生成的10.24 MHz对比10.24 MHz普通石英晶体振荡器方案,其锁相环输出频率稳定度提升3个量级。

表1 技术指标比对

3 结语

本文针对10.24 MHz频率变换器展开研究和改进,在不使用内部或外部倍频电路的情况下,利用10 MHz参考源信号直接作为数字频率合成器件的输入时钟,实现了10.24 MHz信号的频率变换。

同时,相关测试比对证明,在不使用倍频电路的情况下,通过直接数字频率合成器生成的信号在频谱纯净度提升、谐波和相位噪声抑制等方面处理更容易、改善效果更优,并且具备低成本、功耗低、小型化等优点。

推广而言,对于10 MHz高稳信号转换为其他特殊频点后作为高稳信号输出时,只需修改AD9832频率控制字和相应滤波参数即可。