一种低资源消耗的中值滤波硬件架构设计

2019-03-22李智伟

王 珏,李智伟,陈 松

(中国科学技术大学 信息科学技术学院,安徽 合肥 230026)

0 引言

图像在采集、传输、处理、接收及成像过程中会因各种干扰而引入椒盐噪声。椒盐噪声是由图像传感器、传输信道、解码处理等产生的黑白相间的亮暗点噪声,是一种因为信号脉冲强度引起的噪声。这种噪声的存在恶化了图像的质量,影响了图像本身的特征,妨碍了对图像的研究,所以如何实现更好的图像去噪是一个很值得研究的问题[1]。

目前,去除脉冲干扰及椒盐噪声最常用的算法是中值滤波,它可以很好地抑制脉冲噪声提高信噪比,同时还能保护图像的边缘[2]。中值滤波的基本原理是把数字图像中一点的值用该点邻域内的各个点值的中值来代替。一般的排序算法思想就是对像素的值进行比较和交换,典型的有冒泡排序、插入排序。这些算法和当前的比较操作必须基于上一次的比较操作结果,所以对于大窗口的中值滤波,软件运行需要很长时间,而硬件计算起来就需要大量的硬件逻辑资源。目前大部分使用的是3×3的中值滤波算法,但是在较为复杂的图像中,滤波效果不是很好。所以本文采用了5×5的窗口设计。但是基于一般的排序中值滤波算法硬件实施起来会消耗较多的逻辑资源,因此本文设计了一种基于位级中值滤波算法的硬件架构[3],减少了比较的次数和进行数据计算操作的位宽,从而实现了节约硬件逻辑资源,且易于FPGA的实现。

1 位级中值滤波的算法

整个位级中值滤波算法的原理是基于不断找到所有排序的数中较大的数并淘汰的这个原理来实现的。

图像数据要求以二进制形式进行计算,从最高位到最低位,依次对窗口内所有数据在相同位上的数值进行操作。假设当前窗口内有N个非0数据需要排序,则窗口内非0数据的一半为M(向下取整)。从最高位开始,统计在当前位有效数据中所有数值为1的数据个数。最高位计算时,数据非0即为有效数据。再将数值为1的个数与被淘汰的较大的数累加,累加的和与M进行比较,若大于M,则在下一位的计算中,当前计算位值为1所对应的数据为有效数据;否则,在下一位的计算中,当前计算位值为0所对应的数值为有效数据。

对于被淘汰的较大的数据个数的计算,在每一位的计算中,如果在当前位值为1的数据集合没有进入下一位的计算,则说明在当前计算位值为1的数据被淘汰,将这个在当前位淘汰的数据个数与在前面的位计算中淘汰的数据个数累加,即为总的被淘汰的数据个数。

从最高位到最低位,依次进行上述的位操作,直到最后一位计算完之后,留下的仍然有效的数据就是所需要找到的中值。

2 硬件架构设计

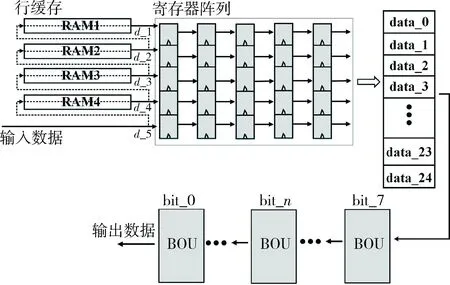

本次硬件架构主要由两个部分组成:数据缓存模块和位计算单元模块,图1展示了总体的一个硬件架构图。

图1 总体设计硬件架构图

2.1 数据缓存模块

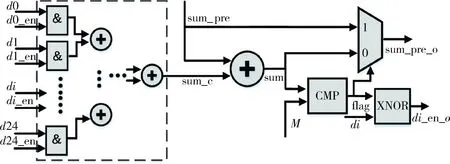

图2 位计算单元结构图

对于数据缓存模块,由于本次设计使用了5×5的中值滤波窗口,且为了提高处理速度要求整个硬件设计是一个流水线结构,也就是窗口内25个数据会同时送入到下一个计算模块中,因此需要4个RAM来缓存每一行的数据,和5×5的寄存器阵列来缓存窗口内的数据。RAM是调用FPGA的IP核来实现的。4个RAM的连接关系和数据流走向如图1中虚线所示,d_1~d_5口同时输出相邻的5行在同一列下的数据到寄存器阵列中。

由数据输入端逐行输入图像数据,并按照虚线的箭头方向依次送入RAM1~RAM4中。每一个周期从输入端送入一个新的图像数据,所以d_1~d_5口每个周期都会输出一组新的列数据,再送入后面的窗口寄存器中。这样就可以实现采样窗口在每个时钟的控制下可以沿被处理图像数据的行方向逐个像素滑动[4]。对于边界处的像素数据,只考虑在图像内的窗口数据参与后续的计算单元。当RAM3和RAM4缓存满时,即可以将窗口寄存器内的数据送入后续的位计算单元来实现流水线的结构设计。

这个寄存器阵列中的25个数据需要同时送入到下一个计算单元中,每个数据都是8 bit的,所有的25个数据都需要从最高位bit_7依次运算到最低位bit_0。所以一共需要进行8次相同的位计算,也就是需要8个位计算单元(bit Operation Unit,BOU)。

2.2 位计算单元

对于每一个位计算单元,结构如图2所示:假设25个窗口数据在同一位的值为d0,d1,…,d24,它们对应的使能信号是d0_en,d1_en,…,d24_en。最高位每个非0数据的使能信号都为1,否则为0。

将每一个数据在当前位的值di及其使能信号di_en相与,然后通过累加这25个数得到sum_c,这个值代表了当前位有效数据中值为1的数据个数。再将sum_c和sum_pre这个值累加起来的值sum与窗口内非0数据总数的一半M进行比较,来计算标志位flag。若大于M,则flag为1,否则flag为0;当flag为1,则在下一个位计算单元中,当前位的有效数据中,值为1的数据的使能信号为1,且传递到下一个位计算单元中的淘汰的较大值个数为sum_pre_o;flag为0时,下一个位计算单元中,当前位的有效数据中,值为0的数据的使能信号为1,且传递到下一个位计算单元中的淘汰的较大值个数为sum_pre_o。上述等价为逻辑计算就是,在下一个位计算单元中,每个数据的使能信号:di_en_o=di ⊙ flag。

每个位计算单元在一个周期内完成,因为每个像素是8 bit的数据,所以需要8个周期才能完成一个窗口内的中值排序输出结果。位计算单元仍是流水线结构。

根据上述的硬件架构设计可知,每个位计算单元仅为1 bit的逻辑操作,位计算单元的个数等于数据的位宽,所以本文设计的中值滤波的硬件设计的一个重要优点就是硬件资源的消耗和窗口模板大小以及数据的二进制表示位宽呈线性关系,这在中值滤波窗口较大的情况下有利于节约资源。

3 实验结果和分析

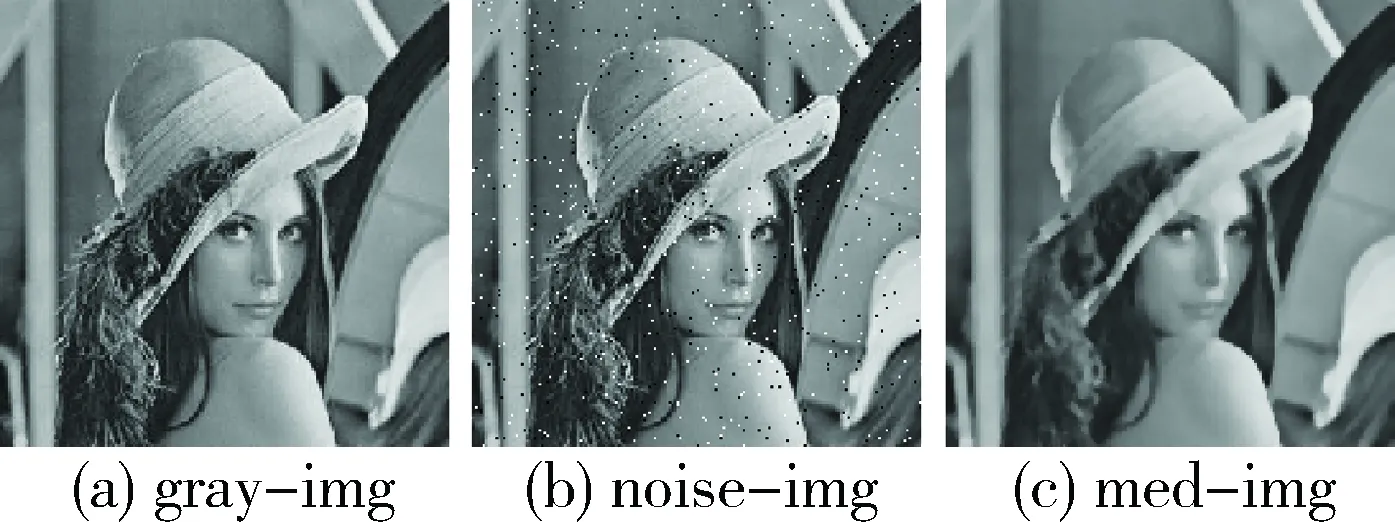

本次实验使用了Xilinx公司下的硬件开发工具Vivado平台来进行开发,完成了架构设计、代码撰写、功能仿真、综合实现等一系列的开发流程。首先将一幅加了高斯噪声的256×256分辨率大小的图像通过MATLAB转化为数据文件,来作为硬件设计的激励文件,再经过Vivado Simulator进行仿真来得到中值滤波后的数据结果,将仿真得到的数据再写入.txt文件中,再用MATLAB来处理这个文件并显示数据。所得到的结果如图3所示,其中图gray-img表示原图,图noise-img为加了高斯噪声后的图像,图med-img为通过仿真得到的5×5窗口大小下的中值滤波的效果。

图3 实验结果图

表1对比了一些常规的中值滤波算法和本文的设计在硬件实现时,所消耗的LUT(Look Up Table)硬件资源。从表中可见,在5×5窗口下的,本设计中的硬件资源LUT消耗远低于一些传统的中值滤波算法。

表1 中值滤波器硬件LUT资源使用情况对比

本文的硬件设计中,对于从第一个数据串行输入到第一个有效中值输出总共间隔了2×256+16=528个周期,所以对于处理一幅分辨率大小为256×256的图像,采用本文的设计,在100 MHZ的处理频率下,所花费时间为:(528+256×256)=0.66 ms,完全满足实时性处理的要求。

4 结论

为了解决数字图像中常遇见的噪声问题,本文从去噪性能、资源消耗、运算速度等方面综合考虑,设计了一种基于位比较算法的中值滤波器的硬件架构,选择了5×5大小的窗口,相对于一些常规的中值滤波算法,本文的设计大大地减小了硬件资源的消耗。本文所设计的结构简单,系统实时性高,硬件资源消耗较小,易于在FPGA上实现,为高效率、低资源的中值滤波硬件设计提供了进一步的参考。