多通道高速数字处理机设计

2019-03-05

(中国空空导弹研究院,河南 洛阳 471009)

0 引言

软件无线电技术在无线通信领域中具有很强的灵活性和开放性,其采用标准化,模块化的结构,主要由天线、射频前端、高速A/D转换器、数字处理器及软件组成,可以很容易实现扩展和升级。因此,在电子战和雷达系统中也广泛使用,数字化接收机比传统接收机具有很大的优势,是未来雷达接收机的重点发展方向[1]。

数字化接收机将中频或射频回波信号进行A/D采样,大大减少了模拟电路的温度漂移、增益变化或直流电平漂移,可保留更多的信息;其回波信号的正交鉴相所得到的正交特性也是模拟接收机所无法比拟的,特别在多通道应用中,采用数字化后,通道间的一致性得到保证[2-3]。并且在利用巴克码调制的二相编码波形后,可以使用脉冲压缩技术提高目标的距离分辨率。

本文设计了一种4通道高速数字处理机,使用4通道250MHz的高速ADC和Kintex-7 FPGA 芯片XC7K325T作为主体,对回波进行采样、数字下变频、脉冲压缩、IQ正交和滤波,将得到多普勒信号通过USB接口传送到上位机,通过数字仿真和实测,验证了数字处理机的良好性能。

1 数字处理机电路设计

电路设计是建立完整的硬件平台,具备高速多通道采样、数字处理及算法实现、电源分配、控制信号和数据通信接口等功能。其系统如图1所示。

图1 数字处理机工作框图

数字处理机采用高速ADC对回波信号数字化,高速时钟分成二路给ADC和FPGA,以保持同步。在数据通信中使用RS-422和LVDS方式进行传输,提高数据抗干扰能力。选用的ADC是TI公司的4通道ADS4449,分辨率14位,采样率高达250 MSPS,使用DDR LVDS并行输出。选用的XC7K325T具有HP IO功能,在1.8 V电源下兼容LVDS接口。

1.1 ADC电路设计

在ADC电路设计中,其前端接收电路设计至关重要,影响信号的SNR、幅度、线性度等,在本设计中,采用无源变压器实现单转差分设计,前级电路的工作带宽中心设置为90 MHz,设计的接收带宽如图2所示。

图2 输入工作带宽

ADS4449 是一款高线性、四通道、14位、250 MSPS模数转换器。此器件针对低功耗和高无杂散动态范围而设计,具有低噪声性能以及在宽输入频率范围内出色的SFDR。ADC通过SPI方式进行设置,可选多种工作模式。

影响ADC的另一个重要指标是孔径抖动,由孔径抖动所限制的SNR为:

SNR=-20lg(2πfaΔtrms)

(1)

式中,fa为模拟信号输入频率,Δtrms是孔径抖动的均方值,其与模拟信号的输入成正比。ADS4449的孔径抖动Δtrms=140 fs,其SNR最大为71 dB。

1.2 电源管理及接口设计

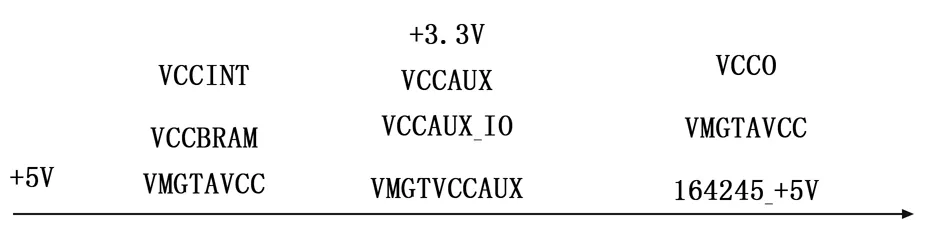

XC7K325T是设计的核心器件,主要的数据处理和算法都在其进行。FPGA采用的是BPI配置方式,使用的配置芯片为PC28F512P30T,具有500 Mb的存贮空间。在电路设计中要考虑到器件对电源上电要求,XC7K325T、PC28F512P30T和SN74ALVC164245采用的电源管理时序如图3所示。

图3 电源管理时序图

采用合理的电源时序控制可以减小上电时的瞬时电流、保证FPGA上电初始IO脚为高阻态和提高芯片在上电瞬间管脚无毛刺和正确偏置。

作为信号处理机需要与外设进行通讯和数据传输,使用的方式为RS-422、USB接口、LVDS接口等,实现多种功能应用。

2 数字下变频设计

数字下变频是软件无线电的关键技术之一,其基本功能是从输入的宽带高数据流信号中提取所需的窄带信号,滤除带外噪声,将其下变频为数字基带信号,并转换成较低的数据流,一般采用多速率数字信号处理。

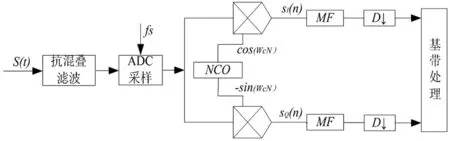

单通道数字下变频算法如图4所示。

图4 单通道数字下变频框图

当ADC前端的中频输入信号为:

x(t)=a(t)cos(wot+χ(t))

(2)

根据带通采样定理,ADC的采样频率要满足fs≥2 rB,避免过渡带混叠且可得到处理增益,或fs≥(r+1)B,允许过渡带混叠。B为中频信号的带宽,r为ADC前的带通滤波器矩形系数。

经过ADC采样后的信号为:

x(ts)=a(ts)cos(wots+χ(ts))=

(3)

式中,a(t)和χ(t)为幅度和相位调制函数。数字正交鉴相要进行I/Q分离,本文使用数字混频低通滤波法进行,其优点是对双路信号同时作变换,所用的滤波器系数一样,从而具有很好的负频谱对消功能,并且处理带宽较宽。数字化中频信号与NCO输出的正交信号进行下变频,NCO的信号频率fc=fo/k,混频后的信号经过低通滤波后,除去高次项,得到:

(4)

s1(t)包含回波信号的全部信息。简化数字信号处理过程为直接抽取和符号变换,取k=3,m=2,此时得到的I/Q两路为:

(5)

从式(5)中得到的I/Q两路,信号频率已经降到基带,但数据量与ADC采样率一样,需要进行抽取和滤波处理。对数字正交混频后的信号进行D倍抽取,抽取后的信号频谱为:

(6)

抽取后的频谱是原来频谱D倍扩展后经频移产生的D个频谱叠加之和。根据奈奎斯特采样定理,原信号含有大于fs/2D的频率分量时,抽取后会产生频谱混叠,因此需要加低通滤波器以滤除fs/2D外的信号,再进行D倍抽取[4]。

2.1 数字下变频模块

数字下变频模块将数字化后的中频信号进行下变频处理,通常使用NCO产生正交的sin(wct)和cos(wct),与中频信号进行相乘滤波[5]。采用最佳的ADC采样频率fs和数字下变频频率fc,可以将数字下变频简化为符号变换。经过ADC采样后的中频信号经过最优采样率变换后,根据式(5)得到的最优采样率关系为:

(7)

由于在FPGA内进行数字下变频时采用数据量与fs是一致的,所以当使用正余弦进行相乘时,实际是经过fs采样后的正余弦信号与ADC采样后的信号相乘,即可得到:

(8)

式中,θ0为选择正交的初相位,当θ0=0时,所用的正交的余弦为[1,0-1,0],正弦为[0,-1,0,1],序列每4个周期重复一次,从而把正交下变频处理简化为符号变换处理,避免在多通道处理中需要多个NCO和相乘运算带来的资源占用问题。

2.2 脉冲压缩模块

根据雷达基本方程,最大探测距离的四次方正比于发射信号的能量,而发射机的峰值功率难以做到很高以满足最大探测距离要求。因此,只能通过提高发射信号宽度来增大发射能量,但发射宽度增大会导致距离分辨率变差。距离分辨率主要取决于信号频域结构,要求信号具有大的带宽,而速率分辨率主要取决于信号时域结构,要求信号具有大的时宽,要设计一种大时宽带宽积信号,才能同时提高速度和距离分辨率[6]。

利用匹配滤波理论,对幅度谱宽的信号进行匹配处理,必然输出一个在时域很窄的响应。采用13位巴克码实现二相编码的脉内调制,可以实现带宽为原脉冲频谱的13倍。巴克码的信号波形时宽为PT时,P为码长13,T为单脉冲宽度。脉压前的信号的距离分辨率为PTc/2,c为光速;脉压后的距离分辨率为Tc/2,即保证了发射信号的时宽,也提高了距离分辨率。巴克码得到的模糊函数图如图5所示,其在原点呈现尖锐的单峰,为图钉型模糊函数。

图5 13位巴克码模糊函数图

在时域进行脉压处理,设计匹配滤波器可以使信号获得最大的SNR,其对应的滤波器的响应为:

h(n)=s*(N-1-n)(0≤n≤N-1)

(9)

由于巴克码脉冲压缩信号的主旁瓣比最大只有13,当采用基于级联失配的旁瓣抑制方法后,可以将主旁瓣比提高到30 dB以上,并且不改变主瓣宽度。其失配网络系数为:

(10)

式中,β的值根据加权网络输出的主瓣叠加方程计算。

脉压滤波器输出的信号即为输入信号与滤波器响应的卷积。经过脉压后得到的信号即为目标的距离信息,通过低通滤波,即可以得到多普勒回波信号[7]。在数字下变频后再进行脉冲压缩处理,只需与原调制码进行互相关即可,有效提高处理效率。

3 仿真设计

使用Matlab对回波信号及处理过程进行设计,模拟目标回波信号的处理过程。设计13位巴克码调制的波形,巴克码单脉冲宽度为25 ns,目标在50 m,径向速度为500 m/s时的接收回波信号及其处理过程如图6所示。信号时宽为325 ns,其相对距离分辨能力为48.75 m,通过脉冲压缩,其相对距离分辨能力为3.75 m,提高了目标的距离分辨能力。

图6 脉冲压缩处理

根据优化后的数字处理流程,对模拟目标的回波信号进行采样、数字下变频、抽取滤波处理,将信号降为基带后进行脉冲压缩、抽取滤波后,得到目标的距离、多普勒频率信息。这些信息对获取目标的主要特征十分重要。

对于4个目标的处理情况如下,距离分别是为50 m,径向速度为500 m/s、距离为55 m,速度为300 m/s、距离为60 m,速度为700 m/s和距离为65 m,速度为600 m/s时的目标,回波处理情况如图7所示。

图7 四个目标时脉冲压缩处理

通过对信号的脉冲压缩处理过程的分析,可以分辨四个相近距离的目标和多普勒频率,通过对代码和处理方式的优化,降低了对处理器资源的要求,提高了信号处理能力。

4 处理机测试

电路设计中ADC前端的滤波器特性实测结果如图8所示,与设计要求一致。信号的插损小于1 dB,边带抑制大于20 dB(BW≥140 MHz),既能保证回波信号时频域的完整度,也可以有效滤除开关电源噪声、低频干扰信号和前端高频串扰信号。

图8 ADC前端滤波器特性图

通过对ADC进行测试,采样频率为120 MHz时,电路板静态噪声特性如图9所示。四通道的噪声一致,峰峰值在1.22 mV左右,对应的动态范围为64 dB。

图9 处理机ADC静态噪声

各个通道的偏移电压是由于ADC器件自身特性及前端电路引入的,可以通过上电之后对其采样取均值,在信号处理中消去即可。使用40 MHz采样,得到的信号和功率谱如图10所示。

图10 ADC采样信号特性

得到信号采样特性较好,其功率谱的信号达到83 dB。通过对设计的数字处理机进行测试,其噪声、通道间串扰及频谱特性较好,处理机所用的处理器资源充足,通过算法及资源优化,可以满足设计要求。

5 结论

本文设计了一种四通道的高速数字处理机,对数字下变频和脉冲压缩处理进行分析,通过简化处理,给出了多目标处理仿真分析结果和数字处理机的电路性能,克服了通道间的串扰,达到了静态噪声1.22 mV的性能和动态范围64 dB的能力。通过测试结果,有效实现高速多通道数字处理机和大动态范围处理,具有广泛的应用前景。