基于片上Loopback的FPGA DDR模块串行测试方法∗

2019-03-01张大宇

王 贺 张大宇 汪 悦 张 松

(中国空间技术研究院 北京 100094)

1 引言

FPGA器件具有高性能、低成本、资源丰富、可重复编程等优点,利用FPGA片上资源设计DDR(Double Data Rate)控制器来实现双倍速率数据传输控制,是高速通信、数据压缩与信号处理等领域中的常用方法。DDR控制器一般通过FPGA片上的专用DDR模块和部分通用可编程资源实现,其中DDR模块是实现双倍速率数据传输的关键电路。传统的DDR模块测试方法是通过FPGA的IO端口对每个DDR模块分别施加测试向量并输出测试结果,因此需要使用大量的测试通道资源,对测试仪器的硬件配置要求较高。

Loopback是高速SERDES(串行器/解串器)电路测试中的常用技术,其原理是将SERDES的输出端口与输入端口短接形成反馈回路[11],以实现高速信号的自发自收测试(如图1所示)。

从实现方式上看,Loopback分为片外的Loopback与片上的loopback两种形式。其中片外Loopback需要通过测试 DIB(Device Interface Board)硬件上的物理线路实现Loopback环路(图1中实线)[13]。相比而言,片上Loopback对DIB硬件设计几乎没有要求,但需要电路在设计时内部预留了Loopback环路(图1中虚线)[12]。

IOB电路是FPGA上的双向可编程IO端口模块,其信号传输方向可通过程序进行控制。利用IOB中的IOBUF可以构建DDR模块的片上Loopback环路,将大量DDR模块在FPGA器件内部串联成链进行测试,从而有效减少测试所需配置次数及IO通道数量。

2 DDR模块特点

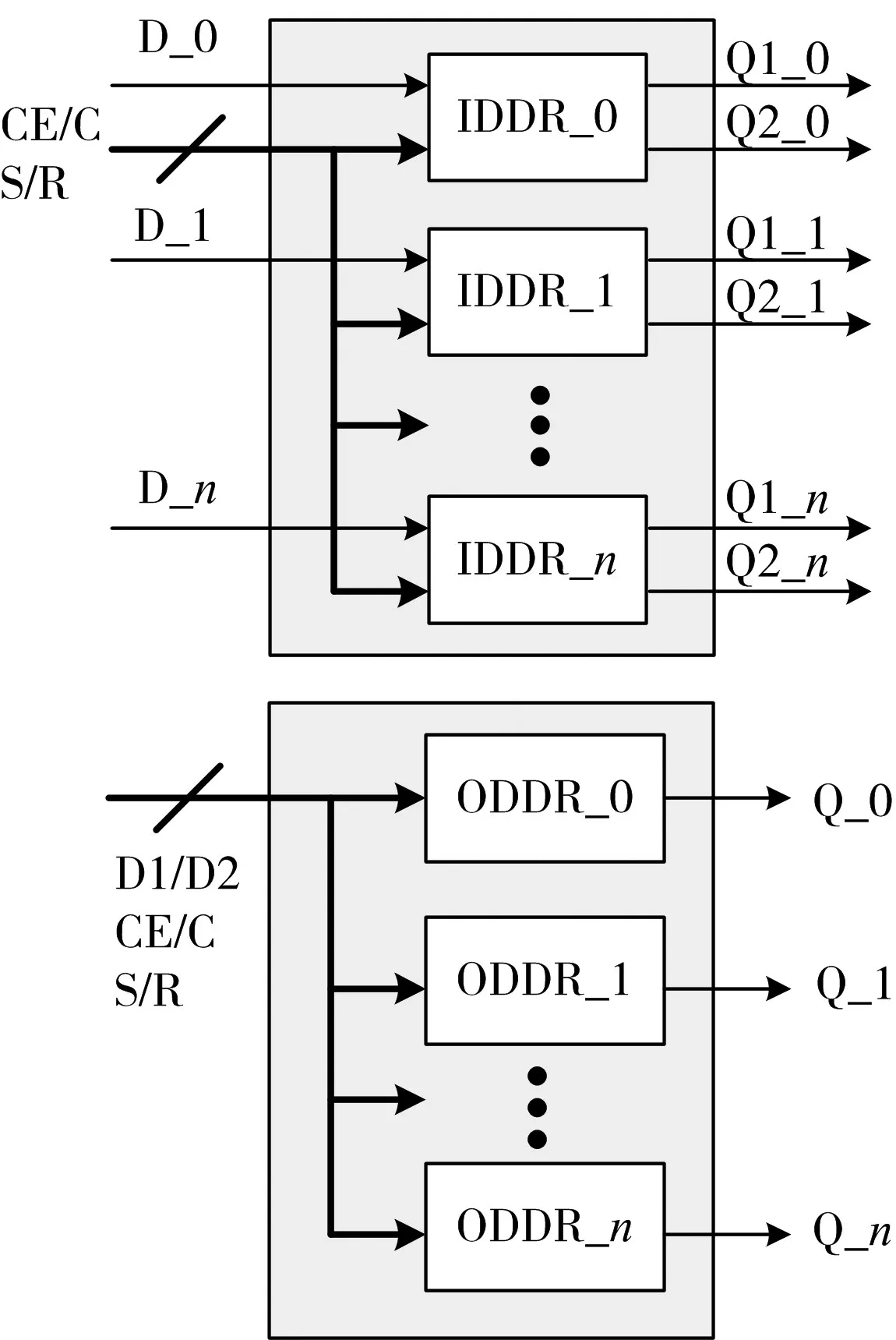

DDR模块位于Virtex FPGA的Select IO资源中,数量与FPGA的IO端口数量相同,每个DDR模块包括IDDR与ODDR两部分[2]。

2.1 IDDR模块

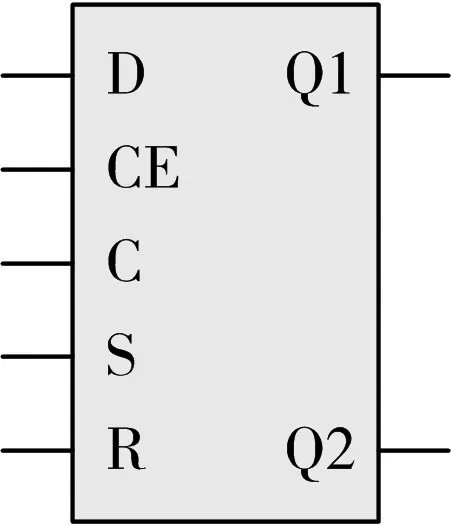

IDDR是用于FPGA输入的双倍数据速率模块,其原语的原理图如图2所示[3]。

图2 IDDR原语原理图

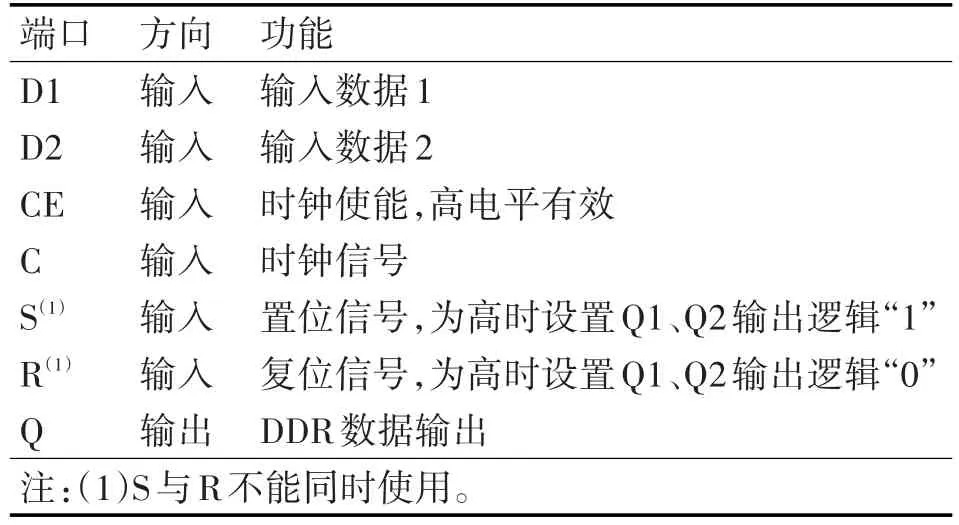

对于IDDR模块端口功能的说明如表1所示。

表1 IDDR端口功能说明

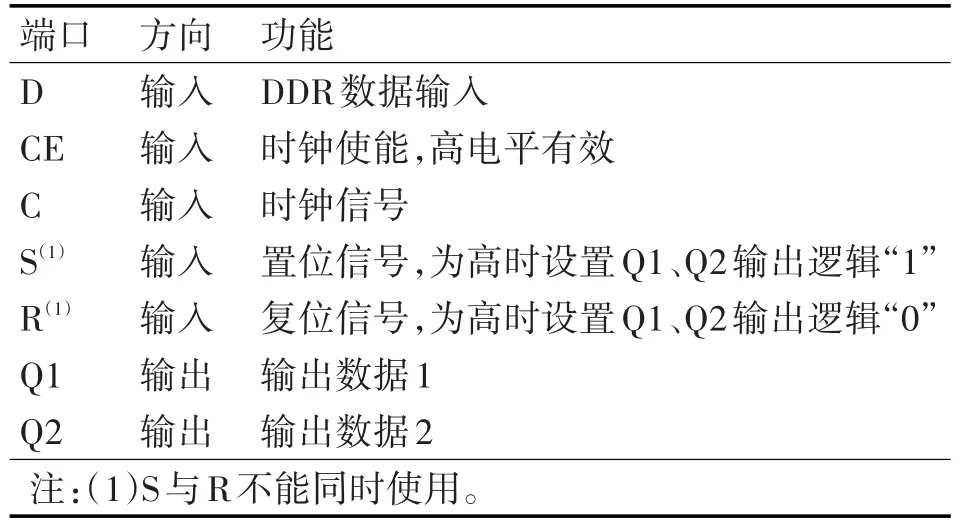

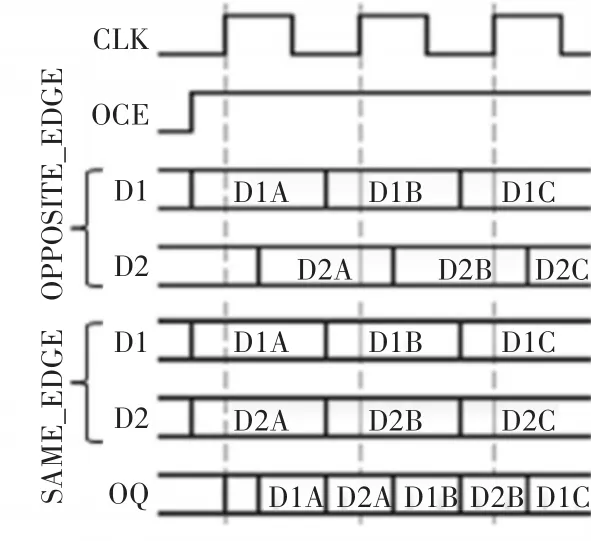

为适应不同应用接口需求,IDDR模块支持三种工作模式,分别是反相模式(OPPOSITE_EDGE),同相模式(SAME_EDGE)与流水线模式(SAME_EDGE_PIPELINED),三种模式的主要区别在于Q1、Q2端口输出数据的时序存在一定差异。其中,OPPOSITE_EDGE模式是在时钟C的上升沿与下降沿分别进行数据采样,输出信号Q1与Q2与时钟C的上升沿与下降沿同步变化;SAME_EDGE模式则通过增加额外的下降沿采样触发器将Q1、Q2的输出都与时钟C的上升沿同步起来,但Q1、Q2之间存在一个时钟周期的相位差;SAME_EDGE_PIPELINED则通过增加额外的流水线寄存器将Q1、Q2的数据输出进行同步,且都对应于时钟C的上升沿[5]。

IDDR模块3种工作模式的具体时序差异如图3所示。

图3 IDDR三种模式功能示意图

2.2 ODDR模块

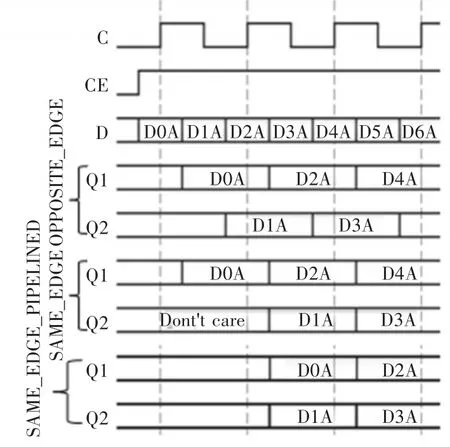

ODDR(Output DDR)是用于FPGA输出的双倍数据速率模块,其原语的原理图如图4所示。

图4 ODDR原语的原理图

对于ODDR模块端口功能的说明如表2所示。

表2 ODDR端口功能说明

与IDDR模块不同,ODDR模块仅支持反相(OPPOSITE_EDGE)与同相模式(SAME_EDGE)2种工作模式,具体输出信号时序特点与IDDR类似,如图5所示。

图5 ODDR两种模式功能示意图

3 DDR模块测试电路设计

3.1 并行测试结构问题分析

传统的DDR模块一般采用并行测试结构,如图6所示[15]。

图6 并行测试方案

并行测试电路的特点是对每一个IO端口的DDR模块功能分别进行检测,代价是需要使用大量的测试仪通道来覆盖FPGA的全部IO端口。此外,IDDR模块测试需要使用2倍于被测DDR模块数量的FPGA IO来输出测试结果(Q1[0..n]、Q2[0..n]),造成每次配置只能完成不足1/3的IDDR模块测试。

以具有850个IO的某Virtex FPGA为例[4],覆盖IDDR与ODDR的全部工作模式测试需要850个测试通道并进行至少16次配置[10],具体分布如表3所示。

表3 某FPGA DDR测试所需配置数量

3.2 基于片上Loopback的串行测试电路设计

从功能上看,DDR模块实际等价于简化的SERDES电路,其中ODDR相当于2并1的串行器,IDDR相当于1分2的解串器,因此可以将ODDR与IDDR组合起来按照Loopback的思路进行测试。但是,由于ODDR的输出与IDDR的输入端口在物理上不存在可编程互联线路,因此无法在HDL程序设计时直接连接,必须借助IOB模块来实现Loopback。

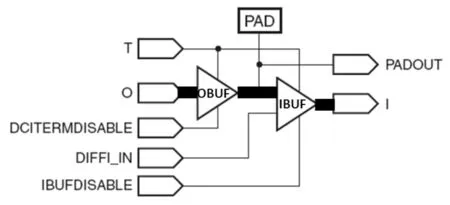

图7 IOB基本结构

某Virtex系列FPGA的IOB模块基本结构如图7所示,其中输入端口O与ODDR的输出Q相连,输出端口I与IDDR的输入D相连。因此,通过图7中加粗的线路(包括2两个驱动器IBUF与OBUF)可以实现ODDR与IDDR的片上Loopback环路。

图8 片上Loopback测试电路结构

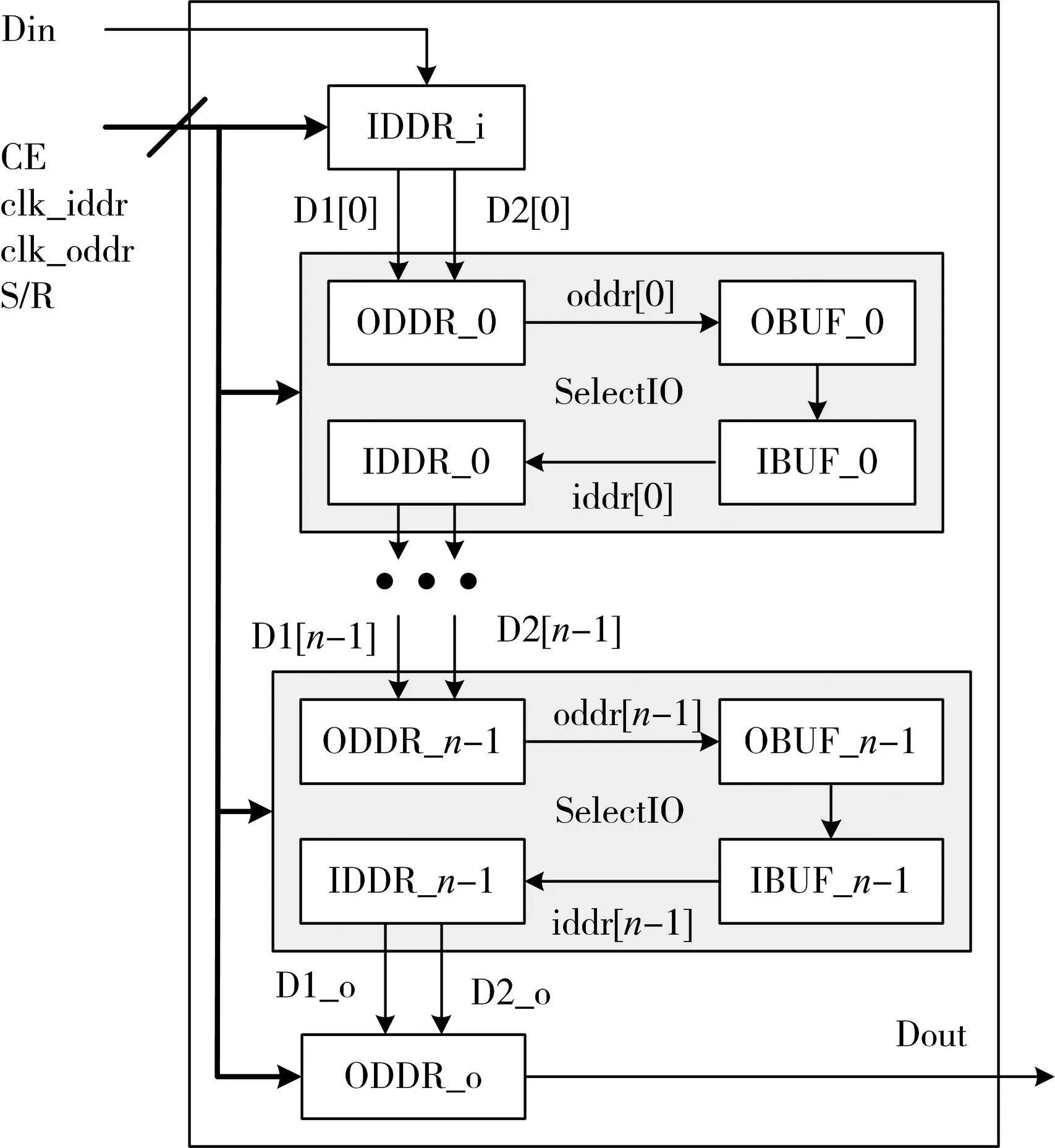

基于IOB构建的DDR模块片上Loopback串行测试电路结构如图8所示,对其说明如下:

1)串联测试线路由“位于链首的Din端口IDDR、位于链中的n个Select IO和位于链尾的Dout端口ODDR”组成,串接的Select IO数量由具体器件的封装引脚数量决定;

2)每个Select IO内部形成一条Loopback环路,n个Select IO在FPGA内部串联成链,上一级Select IO IDDR的两个输出端口(Q1[i]和Q2[i])连到下一个Select IO ODDR的对应输入端口上;

3)全部IDDR与ODDR模块的时钟clk_iddr、clk_oddr、使能CE、复位R(或置位S)由FPGA IO统一提供,Din与Dout各占用一个IO端口。

4)每条片上Loopback串行测试链路需要6个FPGA IO作为测试辅助端口,覆盖全部DDR模块至少需要12个FPGA IO并进行6次配置[8],如表4所示(仍以850个IO的Virtex FPGA为例)。

表4 某FPGA DDR测试所需配置数量

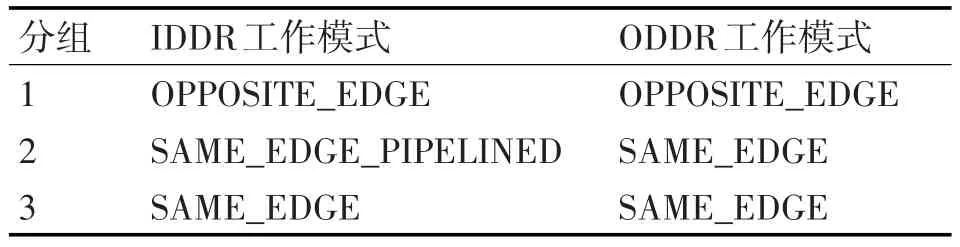

由于Loopback串行测试电路交叉使用了IDDR与ODDR两种模块,因此每个测试电路都需要进行3次配置,以覆盖IDDR与ODDR的不同工作模式,具体组合方式按表5进行。

表5 串行测试组合方案

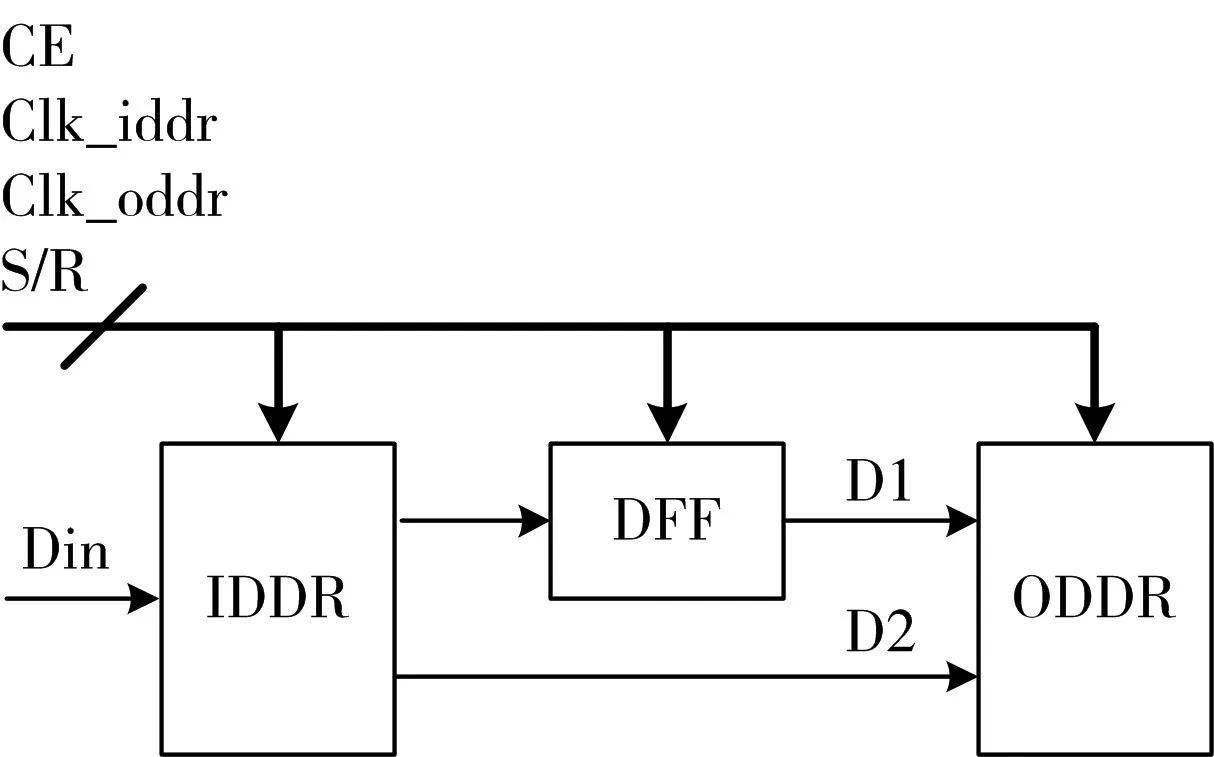

由于IDDR的SAME_EDGE与SAME_EDGE_PIPELINED两种模式仅在Q1端口输出信号上相差一个时钟周期,因此在进行SAME_EDGE(分组3)测试时,可以将图8测试电路中的IDDR与ODDR之间插入一个D触发器(如图9所示,其中IDDR与DFF共用时钟信号),这样就可将其转化为SAME_EDGE_PIPELINED(分组2)模式进行测试。

图9 IDDR SAME_EDGE测试电路

3.3 功能仿真验证

综合分析图8串行Loopback测试电路结构与表5中DDR模块工作模式组合可以得出:

1)图8测试电路的输出Dout应落后输入Din n个信号传递周期,并在第n+1个信号传递周期的clk_oddr上升沿开始变化,其中n为测试电路中串联的Select IO数量。

2)表5分组1(OPPOSITE_EDGE模式)的每个信号传递周期由1个clk_iddr脉冲与1个clk_oddr脉冲组成;分组2(SAME_EDGE_PIPELINED模式)的每个信号传递周期由2个clk_iddr脉冲与1个clk_oddr脉冲组成;分组3按图9设计后功能同分组2。

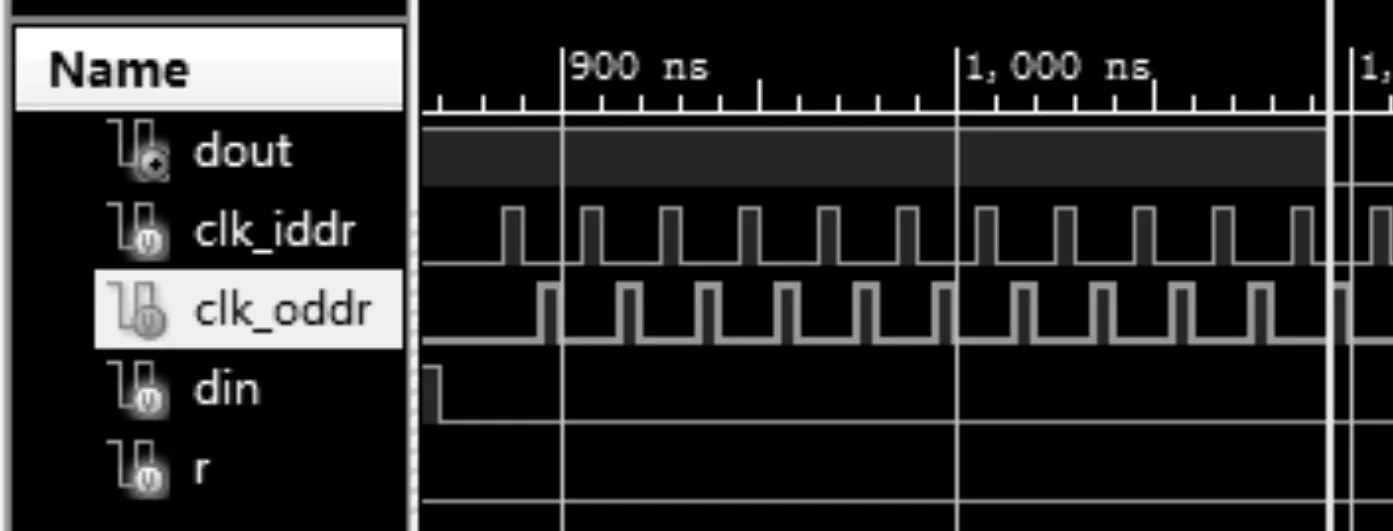

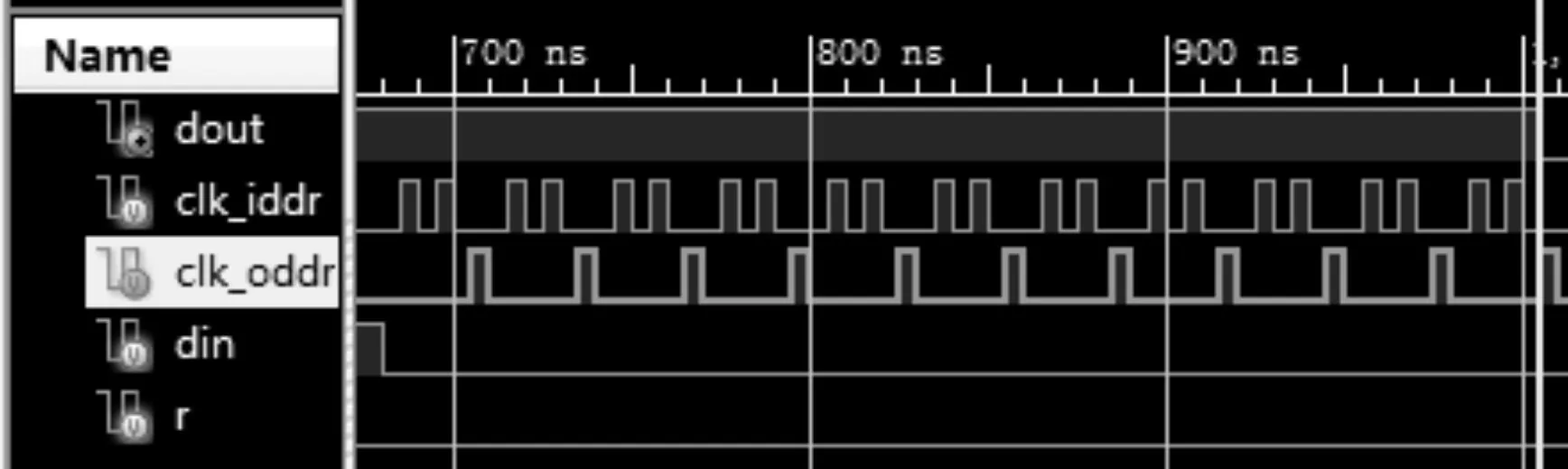

为便于分析,仿真中设定测试电路中串接的Select IO数量为10,分组1仿真波形如图10所示;分组2、3仿真波形如图11所示[6]。从波形状态可以看出,仿真结果与设计功能一致。

图10 OPPOSITE_EDGE模式仿真波形

图11 SAME_EDGE_PIPELINED模式仿真波形

4 基于ATE的自动化测试

DDR模块测试需要对FPGA进行6次配置,为提高效率,本文基于ATE搭建自动化测试平台,ATE型号为美国Teradyne的UltraFLEX系统[7]。

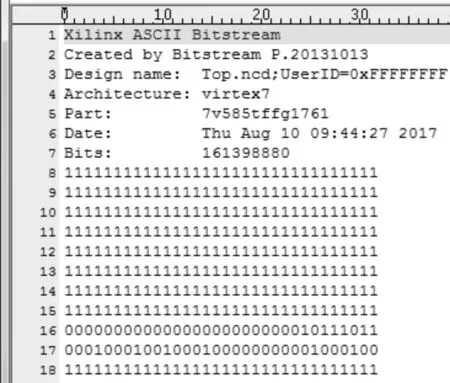

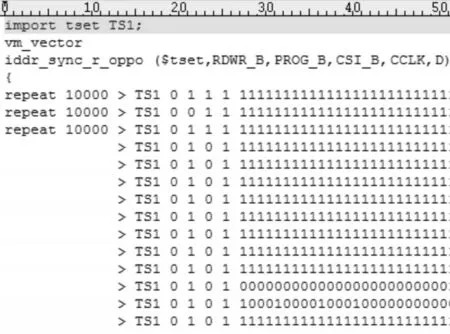

基于ATE的FPGA自动化测试包括位流配置与功能测试两部分,分别需要使用配置向量与测试向量[14]。其中测试向量可以参考图10与图11仿真波形编写,配置向量则需要通过软件转换产生,具体方法如下[9]:

UltraFLEX系统使用“*.pat”格式的二进制向量文件,它是由“*.atp”格式的文本向量文件经Pattern Complier软件编译后产生,而“*.atp”文件可由ISE软件生成的“*.rbt”文本位流文件经转换后得到。

图12 rbt位流文件

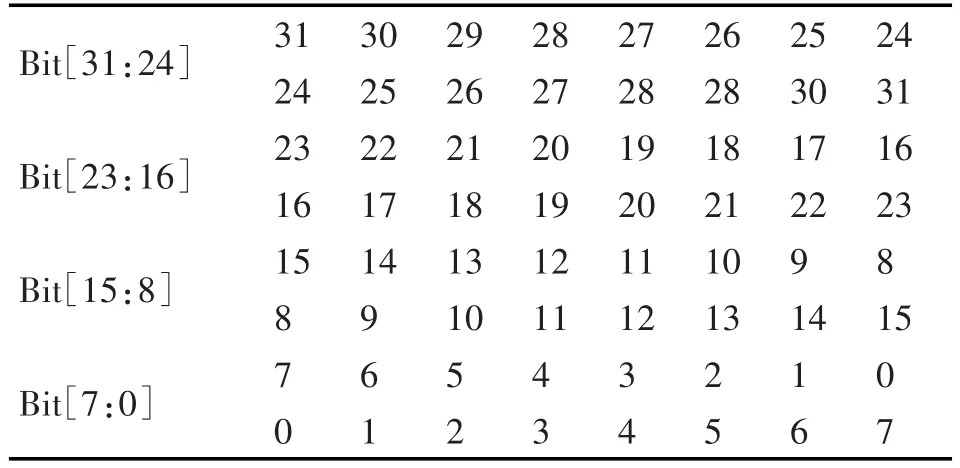

“*.rbt”位流文件内容如图12所示,从第8行开始为FPGA有效配置位流,每行由32个数据组成,对应SelectMap x32的数据总线D[31:0],但顺序并非按从高到低排列,而是以字节为单位按从低到高顺序排列,因此需要按Xilinx配置指南中要求进行“Bit定序”转换后才能使用[1],转换方法如表6所示。

表6 Bit定序对应关系(SelectMap x32)

此外,“*.rbt”文件中只提供了SelectMap配置所需的数据总线信号,用于ATE配置还需在向量文件中补充必要的控制信号(CCLK、CSI_B、PROGRAM_B与RDWR_B)及TimeSet信息。最终转换出的“*.atp”向量文件如图13所示。

图13 atp向量文件

5 结语

本文利用FPGA IOB中的IOBUF资源构建了测试环路,设计了一种结构简洁、占用资源少、便于移植的DDR模块片上Loopback串行测试方法,并在ATE上进行了测试验证。与传统并行测试方法相比,本文所述方法仅需使用12路测试仪通道与FPGA IO端口,同时将覆盖全部DDR模块测试所需的配置次数从16次减少到6次,可用于Virtex系列或其他类似结构FPGA的DDR模块测试。