一种基于RF芯片AS3911的非接触式CPU卡读卡器的设计

2019-02-11曾喜娟

曾喜娟

( 黎明职业大学, 福建 泉州 362000 )

0 引言

近年来随着物联网的迅速发展,射频识别(radio frequency identification,RFID)技术[1]已经在物流、智能交通、工业自动化、电子支付等领域得到广泛的应用.传统的读卡器通常采用NXP公司的PN512芯片[2]和RC531芯片[3]作为主控通信模块,如文献[2]和文献[3]分别采用PN512芯片和RC531芯片设计了一种读卡器,但该读卡器仅支持MIFare卡,待机电流高(6 mA)、通信速率慢(424 kbit/s);另外,该读卡器还需要定时发送REQA和REQB信号来检测卡片是否在位,待机功耗较大.为此,一些学者对传统的读卡器进行了改进.例如:周彦明[4]采用RC522 芯片设计了一种读卡器,该读卡器与主机间采用连线较少的串行进行通信,并且用户可根据需求选取SPI、I2C进行通信,且支持ISO14443A协议;虽然该读卡器的通信效能比传统的读卡器有了大幅提高,但其待机功耗仍较大,且所支持的非接触式卡片的类型仍较少.为了降低读卡器功耗,提高通信效率,本文基于非接触式CPU卡读卡器的工作原理,应用AMS公司的AS3911芯片,设计一种非接触式CPU卡读卡器,并通过实验验证本文设计方案的有效性.

1 非接触式CPU卡读卡器的组成

非接触式CPU卡读卡器系统[5]主要由射频卡、读卡器和PC上位机组成.射频卡由射频接口电路和数字电路组成,其主要功能是接收读卡器发射的射频信号,信号在卡内经过耦合、整流滤波与稳压3个过程后可得到直流工作电压.读卡器主要由控制器、射频卡接口电路和串口电路组成,其功能包括检测射频卡、读取射频卡应答信息以及与PC机通信.读卡时,读卡器先发送REQA和REQB信号检测射频卡是否在感应范围内,若射频卡接收到信号回复ATQ,读卡器读取回复信号后通过串口将其发送至PC上位机.PC上位机实时显示读卡器的当前状态及射频卡的应答信息,同时可向读卡器发送命令.

2 非接触式CPU卡读卡器硬件的设计

2.1 硬件系统结构

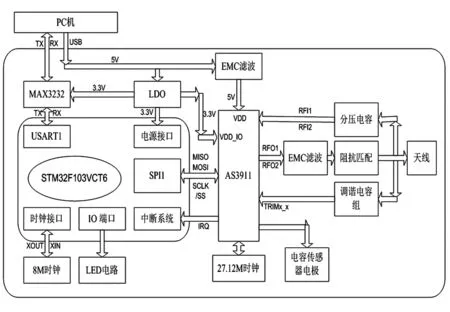

本文设计的读卡器硬件系统[6]包括电源管理模块LDO(采用AZ1117芯片)、AS3911射频卡模块、STM32F103VCT6的CPU模块、串口模块MAX3232以及PC机,如图1所示.

图1 读卡器硬件系统的结构图

2.1.1电源模块的设计 在图1所示的读卡器硬件系统中,LDO电源模块负责为串口通信电路和控制器STM32F103VCT6供电,其输入电压为5 V,输出电压为3.3 V,最小输出电流为100 mA.由MAX3232、LED、STM32F103VCT6、AS3911等元器件的数据手册可知,若使MAX3232、LED、ASTM32F103VCT6、S3911及外设保持正常工作,LDO电源模块需要供应的输出电流I1为:

I1=Istm外设+Istm32运行+Iled+Imax3232≥

6.2 +30.5+20+1=57.7 mA.

(1)

考虑到降额设计,本文按100 mA 的规格设计输出电流,即LDO模块可为上述控制器、外设及串口等提供100 mA的输出电流.AS3911模块的最大工作电流为I_AL=12.5 mA, AS3911内部发射器(射频模块)的最大工作电流I_(AS3911_RF)为300 mA,所以读卡器射频模块的最大总工作电流为312.5 mA.由此可知,LDO模块需要提供的总电流I总为412.5 mA.

采用AZ1117设计LDO电源模块,该芯片的设计指标为: ①输出电压为3.3 V,精度为±1%; ②输出电流为1 A,满足输出电流为412.5 mA的要求; ③输入输出压差为1.15 V,满足压差小于1.7 V的要求.LDO电源模块的电路如图2所示.

图2 LDO电源模块的电路图

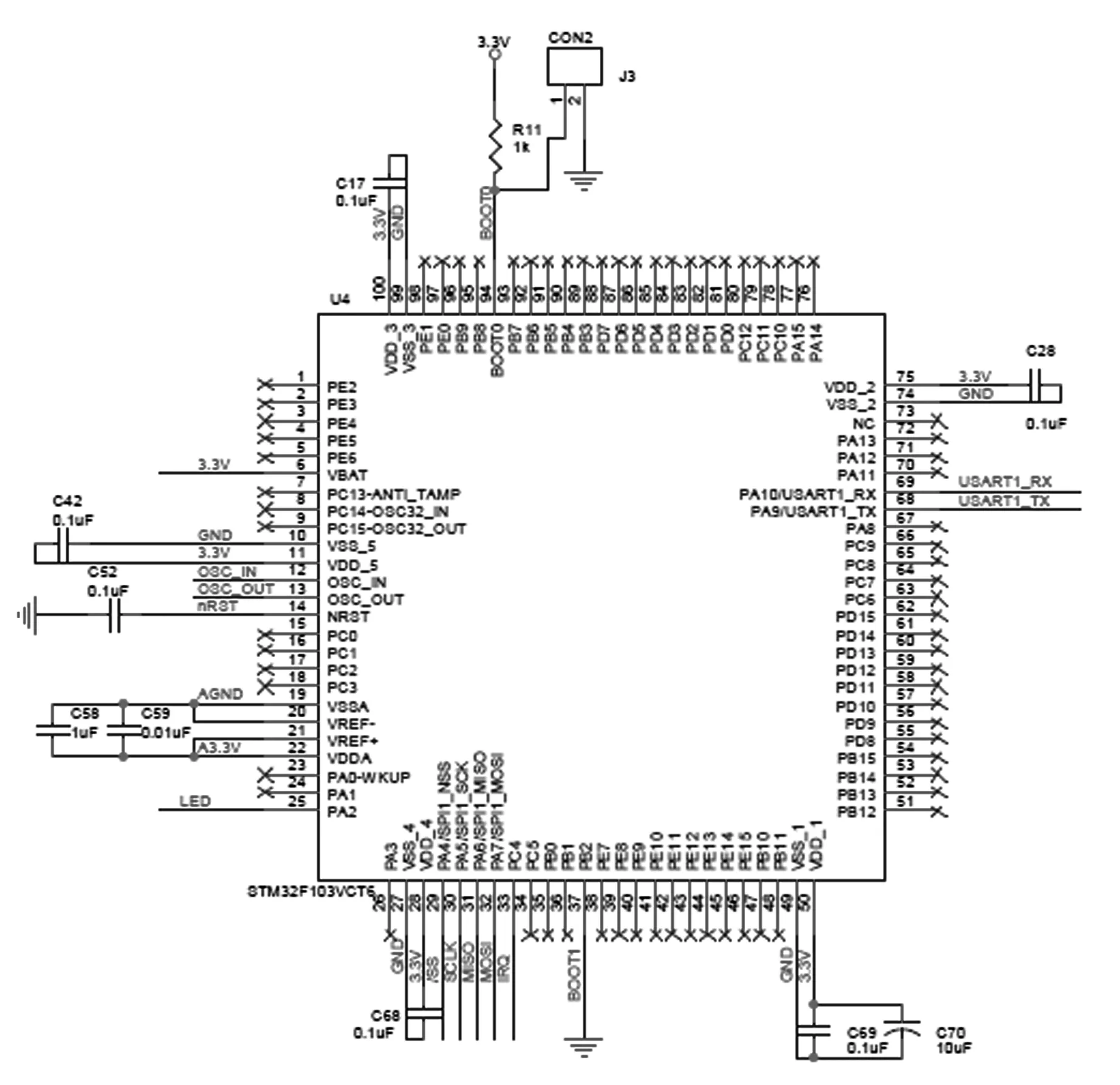

2.1.2非接触式CPU模块的设计 非接触式CPU模块作为系统的主控模块,其主要功能是控制AS3911和Led灯,并与PC机通信.本文采用ST公司的STM32F103VCT6作为非接触式CPU模块.STM32F103VCT6具有SPI接口、3个UART接口(UART1具有串口程序下载功能,还可以实现读卡器与PC机之间的通信)、80点通用IO和强大的中断系统,不仅能实现与AS3911的通信,还可满足设计中所需要控制I/O的数量.非接触式CPU模块的电路图如图3所示.

图3 非接触式CPU模块的电路图

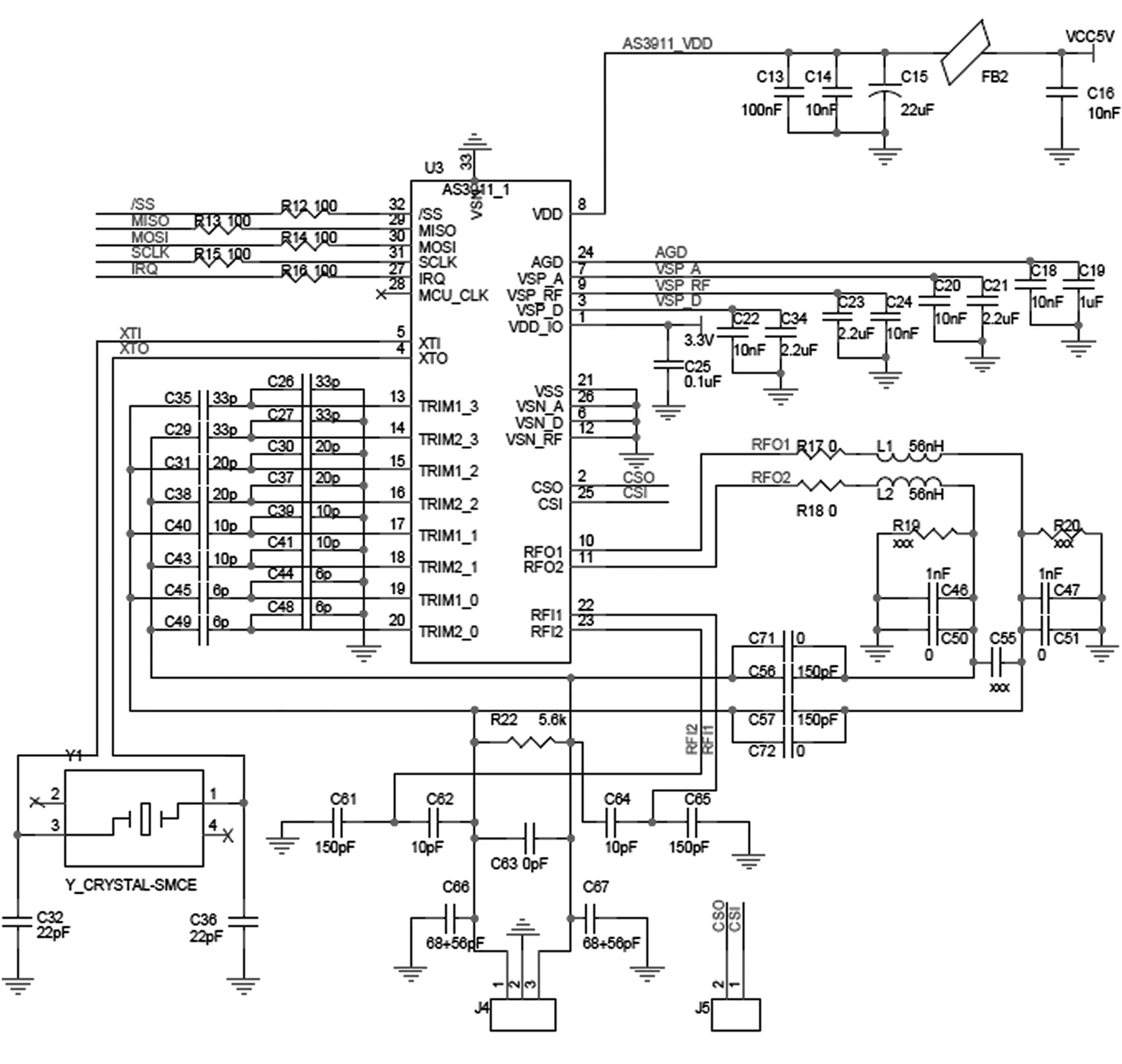

2.1.3AS3911射频卡模块的设计 射频卡模块采用AMS公司的AS3911射频芯片,其工作电路图如图4所示.图4中,AS3911芯片通过SPI总线与控制器通信,外接晶振电路、EMC滤波器、阻抗匹配电路、天线、调谐电容组、接收电路等,以此实现其与射频卡的通信任务.

图4 射频卡模块的电路图

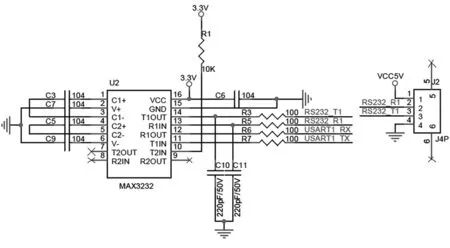

2.1.4串口模块的总体设计 STM32F103VCT6 的UART1具有ISP下载功能,所以本文选择UART1作为系统的串口通信电路.因读卡器与PC机间的电平不兼容,因此需要有一个电平转换电路.因MAX3232芯片能够支持3~5 V的宽电压,因此本文采用MAX3232芯片来实现RS232电平与CMOS电平间的转换,其转换原理如图5所示.

图5 RS232电平与CMOS电平间的转换原理图

2.2 测试分析

2.2.1电源、晶振指标的测试 1)指标要求.电源及晶振电路需达到的技术指标[7]如下:

①VDD由USB供电,供电电压范围为4.75~5.25 V.

②VDD_IO的电压范围为3.267~3.33 V.

③VAGD 的电压范围为1.4~1.6 V,典型值为1.5 V.

④待机模式为IVDD<2 μA;唤醒模式为IVDD<6 μA;关闭载波模式为IVDD<7.5 mA;读卡状态下,IVDD<200 mA.

⑤AS3911芯片的内部最大消耗电流I内部为7.5 mA.

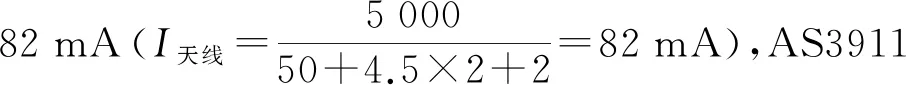

2) 测试方法及记录.电源及晶振电路的测试方法及测试结果如表1所示.由表1可以看出,各项指标均符合要求.

2.2.2射频信号指标的测试 根据信号发送和接收方式的不同,ISO/IEC14443-3定义了Type A和Type B两种卡型[8],其区别主要是载波的调制深度及二进制数的编码方式不同.

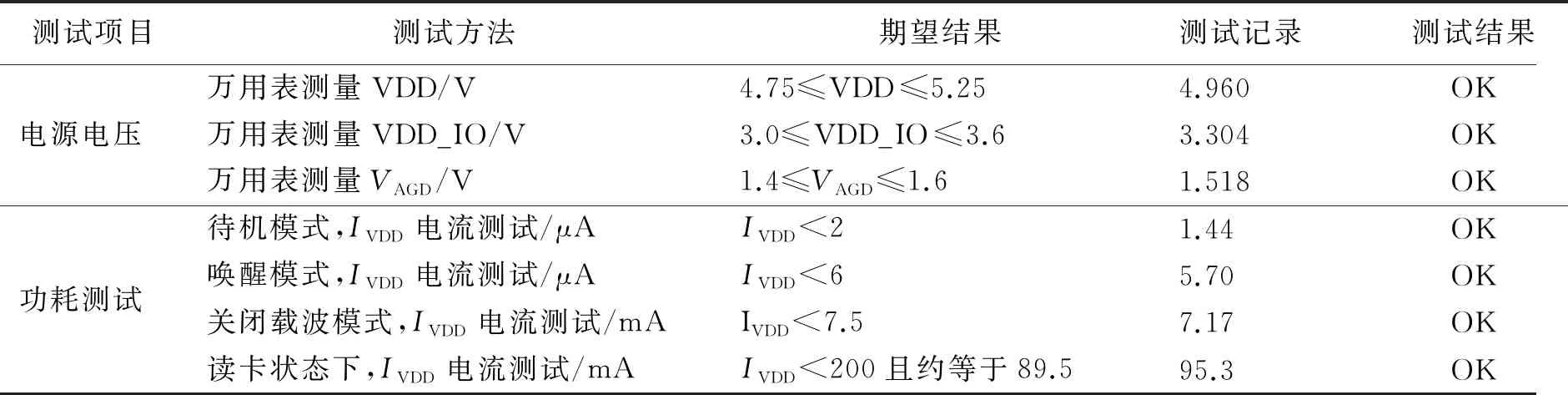

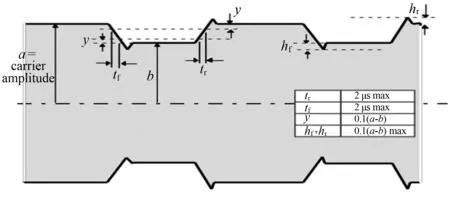

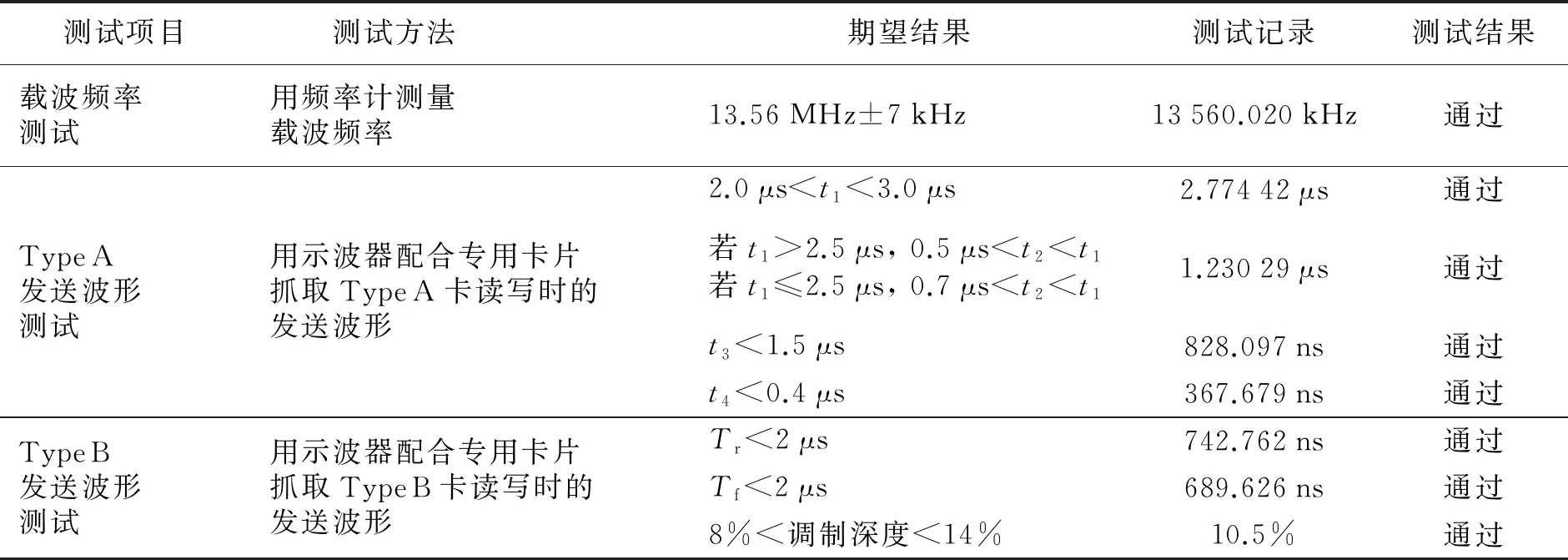

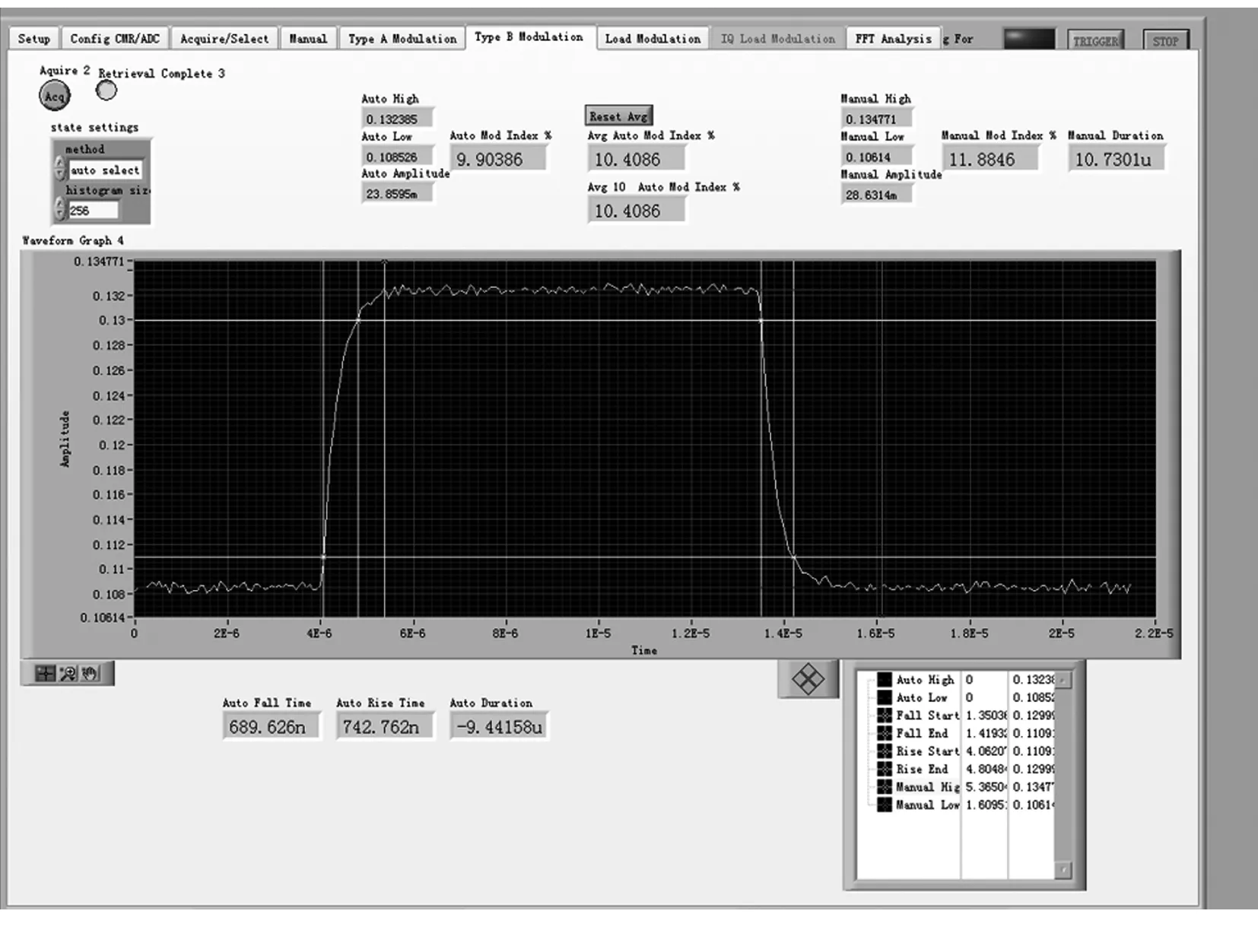

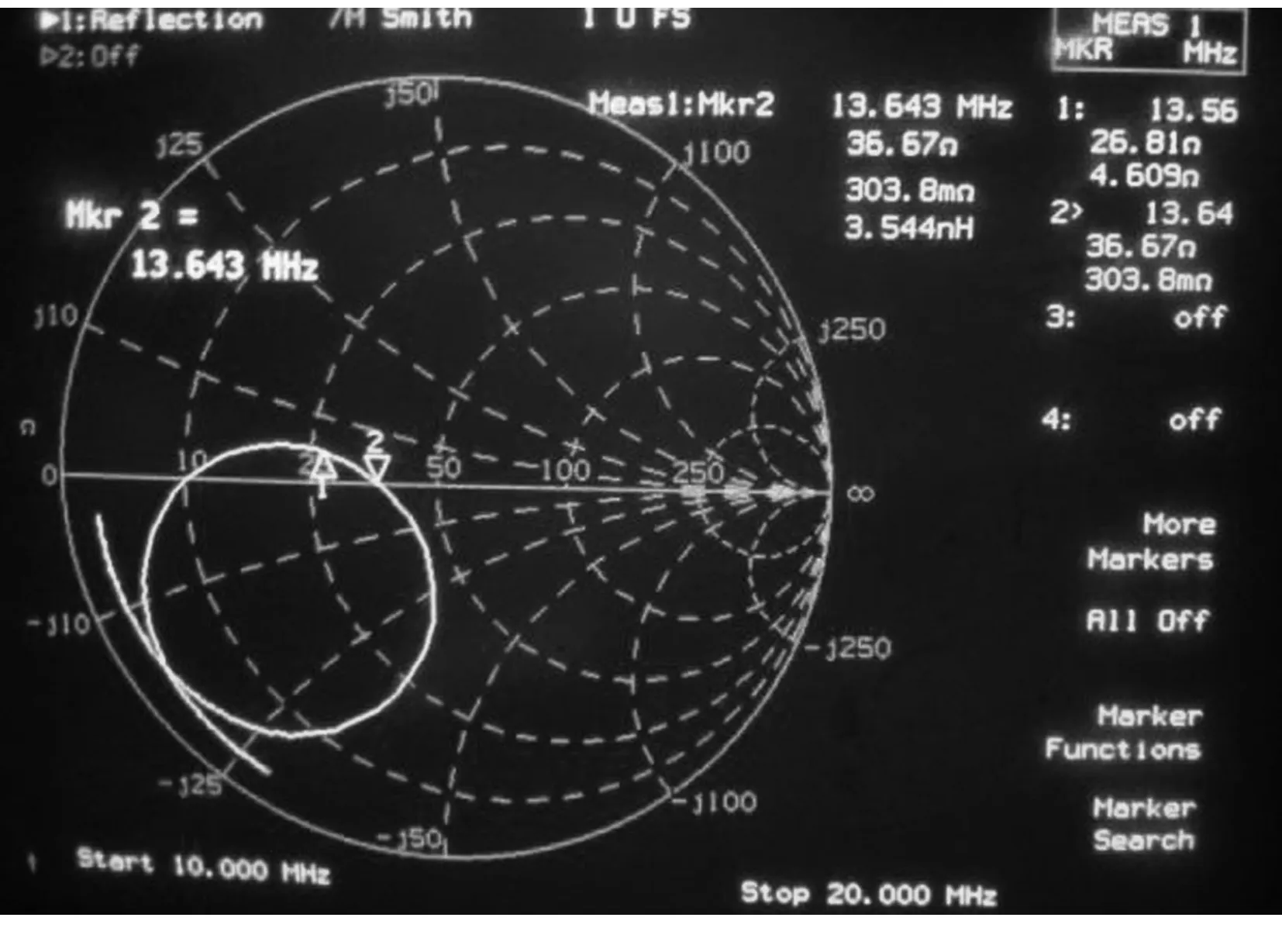

1) 指标要求.射频信号的载波频率应在13.553~13.567 MHz范围内.Type A调制信号的波形指标如图6所示.图6中,t1为信号下降时间,即信号幅值从90%下降至5%且保持在5%时所需的时间,其时间范围为2.0 μs 2) 测试方法及记录.射频信号指标的测试方法及测试结果如表2所示.由表2可以看出,各项测试结果均满足要求. 表1 电源及晶振电路的测试记录 图6 Type A调制信号的波形图 图7 Type B调制信号的波形图 表2 射频信号指标的测试记录 图8为Type A卡在2 cm处测试所得的调制信号波形图.由图8可以看出,t1=2.774 42 μs,t2=1.230 29 μs,t3=828.097 ns,t4=367.679 ns,该结果均满足表2中所期望的结果. 图9为Type B卡在2 cm处测试所得的调制信号波形图.由图9可以看出,波形上升时间Tr=742.762 ns,下降时间Tf=689.626 ns,均满足小于2 μs的指标要求. 图8 Type A卡在2 cm处测试所得的调制信号波形图 图9 Type B卡在2 cm处测试所得的调制信号波形图 2.2.3天线阻抗匹配的测试 读卡器天线的阻抗应与读卡器匹配,且需让天线谐振点保持在13.46 ~13.66 MHz范围内.本设计中测得的Smith圆图如图10所示.由图10可看出,阻抗虚部为0点的频率在13.643 MHz处,即谐振点在13.643 MHz处,满足指标要求. 图10 阻抗匹配波形图 通过以上测试可知: ①电源电压及其纹波均满足我国金融集成电路(IC)规范所要求的相关技术指标; ②在待机模式下,实测电流IVDD为1.44 μA,满足指标小于2 μA的要求; ③在唤醒模式下,实测电流IVDD为5.7 μA,满足指标小于6 μA的要求; ④在关闭载波模式下,实测电流IVDD为7.17 mA,满足IVDD< 7.5 mA的要求; ⑤在读卡模式下,实测电流(95.3 mA)虽然略大于理论电流值89.5 mA,但满足IVDD< 200 mA的要求. 另外,载波频率、载波波形和天线阻抗也均符合标准要求.由以上测试结果可判定本文设计的读卡器可满足应用要求,且具有待机功耗小、稳定性好的优点. 本文基于AS3911芯片的非接触式CPU卡设计的读卡器的各部分电路均满足设计要求,且该读卡器具有良好的稳定性、兼容性、灵敏性,待机功耗小,因此该读卡器在手持POS等行业中具有良好的应用前景.本文在研究时,未能充分考虑读卡器的抗干扰能力,今后将对此做进一步研究.

3 结论