应用Verilog HDL设计等占空比奇数分频器

2018-12-28孙长智

徐 雷,孙长智

(亳州学院电子与信息工程系,安徽亳州236800)

在数字系统设计中,时钟信号是最重要的信号之一,经常需要使用分频器对某个给定频率的时钟信号进行分频操作,得到所需频率的时钟信号。根据设计需要,会遇到偶数分频、奇数分频等。在某些设计中,系统不仅对频率有要求,而且对占空比也有严格的要求[1]。对于偶数分频器及非等占空比的奇数分频器,实现较为简单,但对等占空比的奇数分频器的实现较为困难[2],这是因为计数器为奇数,前半个和后半个周期所包含的不是整数个输入时钟脉冲的周期[3]。本文以等占空比的七分频器的设计为例,使用Verilog HDL(Hardware Description Language)实现了与逻辑关系法和或逻辑关系法七分频器的设计,并利用Quartus II进行仿真,验证了设计的正确性。

1 Verilog HDL语言

Verilog HDL是一种用文本方式描述的数字电路和数字系统的语言[4]。Verilog HDL类似于C语言,语法简洁,结构自由,入门较易,对底层电路描述能力较强,允许设计者在不同的抽象层次上对数字电路进行建模,同时还能够对所设计的数字电路进行逻辑综合、仿真以及时序分析。采用Verilog HDL设计的数字电路具有如下优点:可以直接嵌入到多种应用系统中;可以与其他电路一起设计在同一块FPGA上,提高系统集成度和FPGA的利用率;可以边设计边调试,有效提高设计效率,缩短设计周期[5]。

2 与逻辑关系法实现等占空比七分频器的设计

以设计2n+1分频器为目标(n为大于1的正整数),与逻辑关系法实现的等占空比奇数分频器的设计步骤如下:(1)定义两个2n+1进制的计数器对系统时钟的上升沿和下降沿分别进行计数;(2)定义两个一位的寄存器类型的中间变量,其中一个用于寄存上升沿的状态,另一个用于寄存下降沿的状态;(3)当上升沿计数器有连续n+1个上升沿时,用于寄存上升沿状态的寄存器变量为高电平,其余情况该寄存器变量的状态为低电平;当下降沿计数器有连续n+1个下降沿时,用于寄存下降沿状态的寄存器变量为高电平,其余情况为低电平;(4)把两个寄存器变量进行与逻辑关系运算,其结果就是等占空比2n+1分频器的输出。

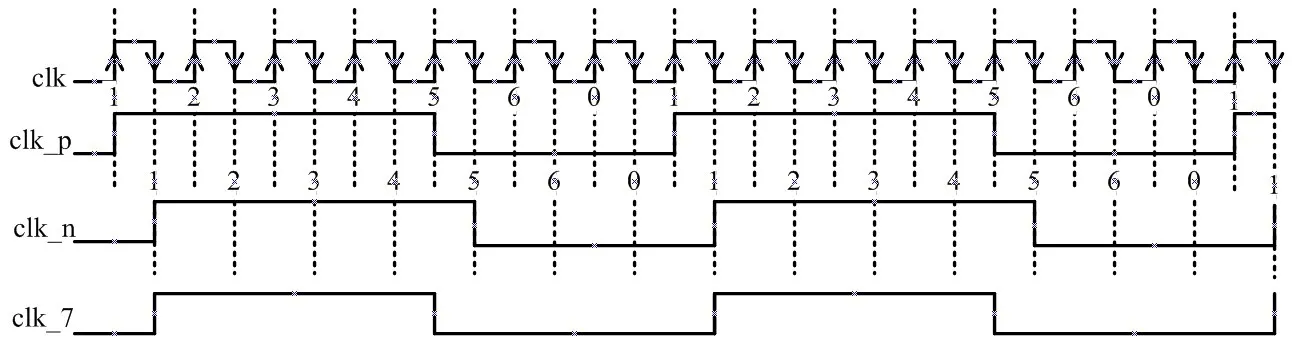

以七分频等占空比为例,验证与逻辑关系法的正确性。按照与逻辑关系法的设计步骤,利用两个七进制计数器分别对数字电路系统时钟clk的上升沿和下降沿分别进行计数,定义两个一位的寄存器变量clk_p和clk_n作为中间变量;当上升沿计数器为1、2、3、4时,clk_p为高电平,其余情况(5、6、0)clk_p为低电平;当下降沿计数器为1、2、3、4时,clk_n为高电平,其余情况(5、6、0)clk_n为低电平。寄存器变量clk_p和clk_n进行与逻辑关系运算得到的结果即为七分频器的输出结果clk_7,其原理如图1所示。

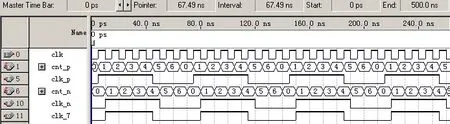

利用Quartus II9.0自带的仿真软件实现了上述与逻辑关系法设计的等占空比的七分频器,仿真结果如图2所示。

图1 与逻辑关系法实现等占空比七分频器原理图

图2 与逻辑关系法实现等占空比七分频器的设计仿真结果

3 或逻辑关系法实现等占空比七分频器的设计

以设计2n+1分频器为目标(n为大于1的正整数),或逻辑关系法设计等占空比奇数分频器的设计步骤如下:(1)定义两个2n+1进制的计数器分别对系统时钟clk的上升沿和下降沿进行计数;(2)定义两个一位的寄存器类型的变量,其中一个用于寄存上升沿的状态,另一个用于寄存下降沿的状态;(3)当上升沿计数器有连续n个上升沿时,用于寄存上升沿状态的寄存器变量为高电平,其余情况该寄存器变量的状态为低电平;当下降沿计数器有连续n个下降沿时,用于寄存下降沿状态的寄存器变量为高电平,其余情况该寄存器变量的状态为低电平;(4)把两个寄存器变量进行或逻辑关系运算,其结果就是等占空比2n+1分频器的输出。

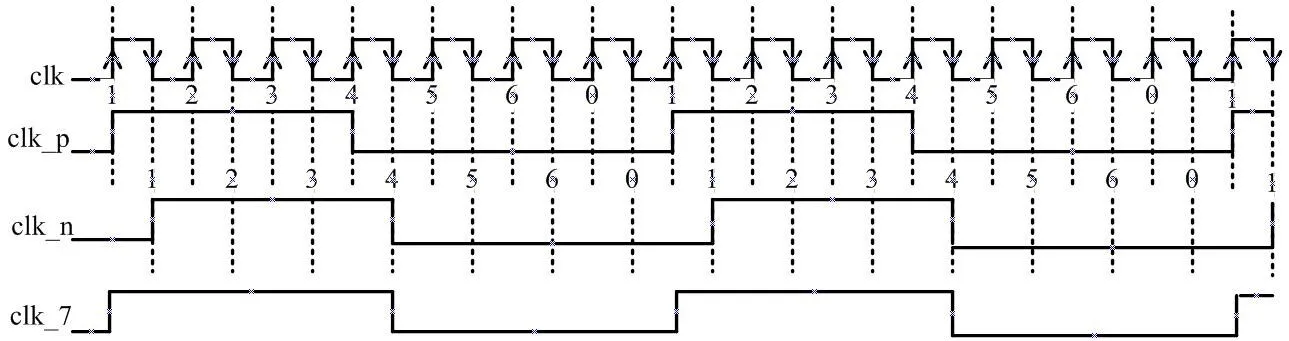

以七分频等占空比为例,验证或逻辑关系法的正确性。按照或逻辑关系法设计步骤,利用两个七进制计数器分别对数字电路系统时钟clk的上升沿和下降沿进行计数,定义两个一位的寄存器变量clk_p和clk_n作为中间变量,当上升沿计数器为1、2、3时,clk_p为高电平,其余情况(4、5、6、0)clk_p为低电平;当下降沿计数器为1、2、3时,clk_n为高电平,其余情况(4、5、6、0)clk_n为低电平。寄存器变量clk_p和clk_n进行或逻辑关系运算的结果即为七分频器的输出结果clk_7,其原理如图3所示。

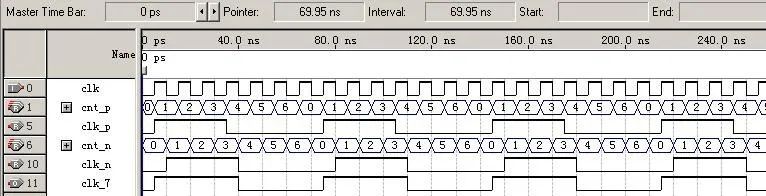

利用Quartus II9.0软件自带的仿真工具实现了或逻辑关系法设计的等占空比的七分频器,仿真结果如图4所示。

图3 或逻辑关系法实现等占空比的七分频器原理图

图4 或逻辑关系法实现等占空比的七分频器的设计仿真结果

4 总结

本文在介绍了与逻辑关系法和或逻辑关系法实现等占空比奇数分频器设计方法的基础上,分别以等占空比七分频器的设计为例,利用Quartus II9.0自带的仿真工具对两种方法设计的七分频器进行了功能仿真,仿真结果证明了两种设计方法都能够实现等占空比七分频器,从而说明利用这两种方法可以实现任意等占空比的奇数分频器设计。