一种高精度多通道USB地震数据采集器设计

2018-11-26韩智明李亚南郭丽丽

孟 娟,洪 利,韩智明,李亚南,郭丽丽

(防灾科技学院,河北 三河 065201)

0 引 言

精确、可靠的获取地震信号是进行地震观测、地震速报、地震预报及研究的重要前提,因此,地震数据采集器的设计与研发成为业界关注焦点。目前,有多种方案实现地震数据采集器,如基于嵌入式[1-2]、FPGA[2-4]、及Labview[5-6]等。近年来,地震数据采集器的实际应用要求不断提升,如采样通道数更多,采集速度更快,采样精度更高,成本更低廉等。尤其是随着城市化进程的加剧,测试环境背景噪声愈发复杂,在提高采集信号的抗干扰能力的同时,还要采用更高效的数字信号处理算法以得到理想的采集数据。传统的基于嵌入式微处理器技术的采集器,运算速度较低、存储容量少,不利于高复杂度高性能信号处理算法,也不利于提高地震数据采集的精度。基于Labview技术的采集系统的精度和成本严重依赖于数据采集卡,且不利于复杂信号处理算法的实施。FPGA具有运行速度快、支持高速I/O、实时性高等特点,采用并行处理的工作方式,便于进行高速信号处理,更适合高速、多通道、高精度的地震信号采集系统设计。

本课题以高精度、多通道、高速为目标,设计了一种基于FPGA的高速8通道地震动信号采集器。相比以往传统采集器通过提高数据转换精度提高地震信号检测性能,该采集器基于前端调理电路提高地震信号的抗干扰能力,并采用24位高精度ADC芯片ADS1278,以FPGA为主控芯片实现8路地震信号的同步准确采集;同时设计了FPGA与PC的USB接口,便于采集数据的快速传输、处理与存储,可极大提高地震数据采集系统性能。

1 系统模型

如图1所示,传感器信号在AD转换前先进行调理,使其信号幅度匹配ADC芯片量程,并尽可能减少干扰和噪声;ADC选用ADS1278芯片,其采样分辨率24 位,8路同步采样率为128 Ks/s,可满足地震采集需求。为提高信号抗干扰能力,采用差分输入方式。综合考虑性能、IO资源、成本等要求,选用CycloneII系列的EP2C8Q208C8作为主控芯片,控制ADS1278采集数据并将数据保存至FPGA内部的FIFO缓存,并利用USB微控制器CY7C68013A将数据实时传输至PC,CY7C68013A工作在Slave FIFO模式,可实现采集数据的快速传输存储。由于各芯片电压需求不一样,为使系统稳定工作,通过电源转换芯片获取芯片所需电压。

图1 地震数据采集系统架构

2 系统硬件设计

系统硬件主要包括前端调理电路、AD转换电路、FPGA控制电路、USB接口电路等。

2.1 前端调理电路

地震传感器获取的地震信号较微弱,通常为毫伏甚至为微伏级,且采集信号中易混入噪声和干扰,因此无法直接进行A/D转换,必须进行滤波和放大,使调理后的地震信号的幅度匹配ADC电压输入量程,同时尽可能去除噪声。

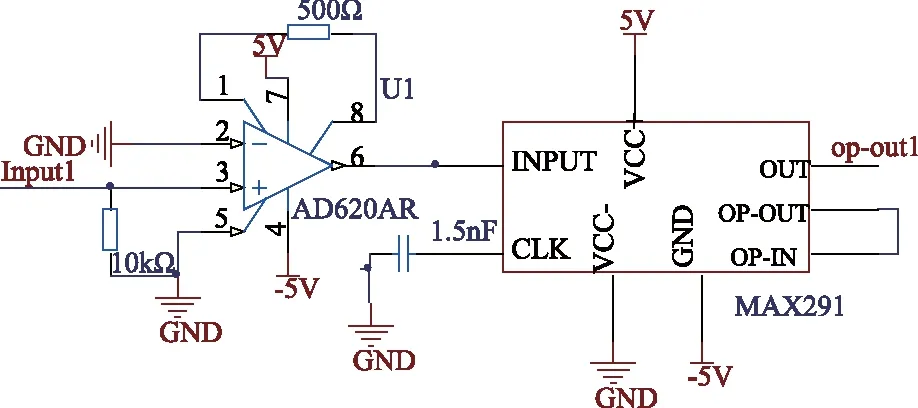

在滤波前先进行前置放大,采用失真度小的仪表放大器AD620放大,并利用八阶开关电容低通滤波芯片MAX291进行滤波。一般地震仪记录的地震波频带范围在200 Hz以内,因此设计截止频率为200 Hz的低通滤波器,以滤除信号中高频噪声,电路如图2。

图2 前置放大与滤波电路

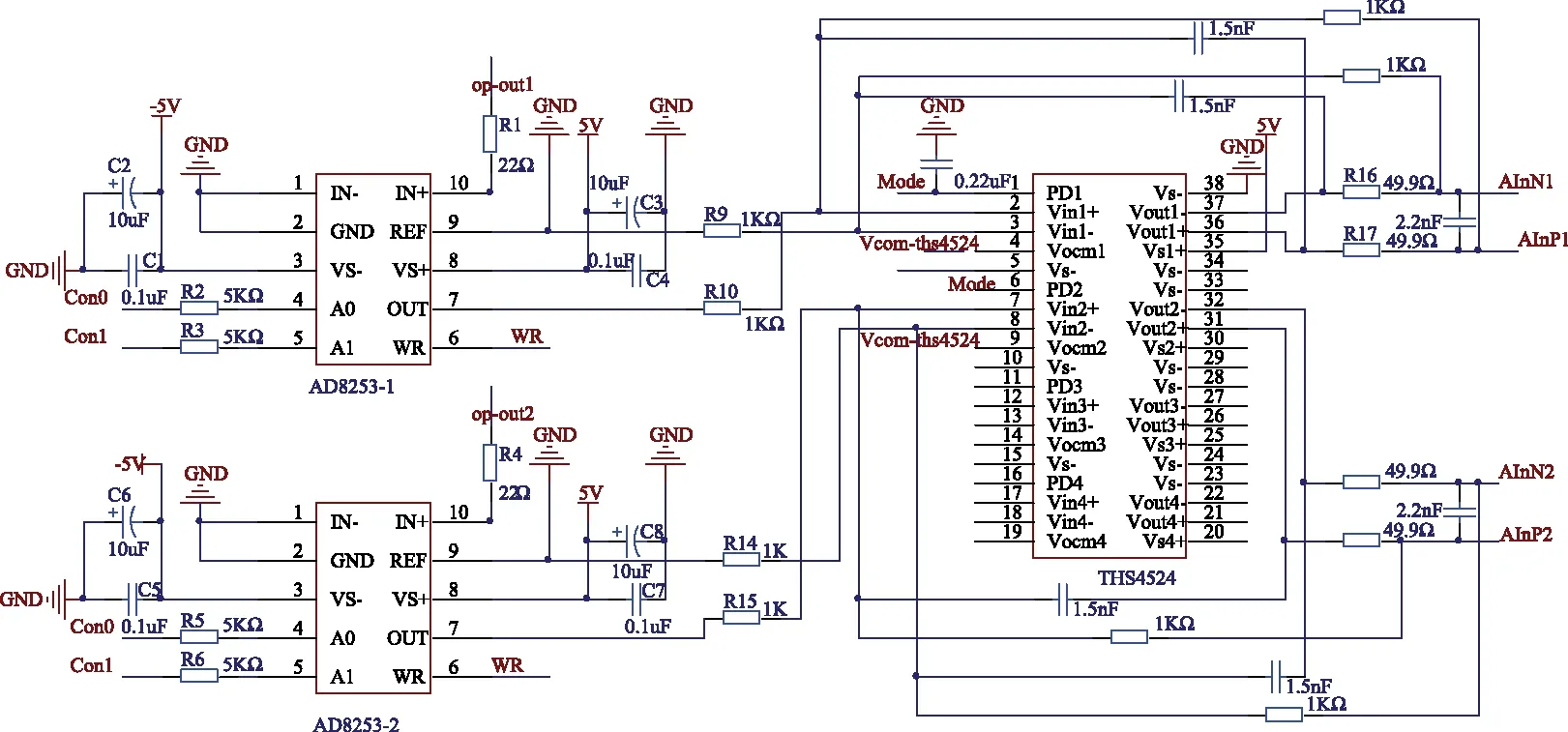

图3 二级放大与差分电路

为匹配ADC量程,需对滤波信号进行二级放大,同时为提高信号在传输过程中的抗干扰能力,采用差分方式采集。如图3所示,选用可设置增益仪表放大器AD8253放大,该芯片可灵活设置增益(1~1000),能适应不同地震传感器的输出幅度和灵敏度;同时,利用差分放大器THS4524将单端输入信号转换为差分信号,以消除干扰,高效驱动ADC。

2.2 AD转换电路

因同时采集8路传感器信号,因此选用8通道,24位ADC芯片ADS1278进行AD转换。ADS1278芯片的AD转换输出值与D=Vin/Vref0x7fffff,其中Vref为参考电压,Vin为输入电压,Vref精度和稳定性很重要,选用REF5025和OPA2350来提供稳定参考电压源,如图4。

ADS1278采用二进制补码输出,有高速、高分辨率、低功耗、低速等4种工作模式,通过配置MODE[1:0]来确定;其数据输出的接口协议和输出格式,通过FORMAT[2:0]来设置,SCLK通过FPGA时钟分频得到,SYNC控制内部8个转换器是否处于同步,PWDN[8:1]控制是否打开该通道[7]。设置ADS1278的FORMAT[2:0]= 001b,MODE [1:0]=00b,PWDN[8:1]=11111111b,Test[1:0]=00b,则ADS1278打开8个通道,在高速模式下,基于SPI协议通过DOUT1引脚(TDM模式)移位输出转换数据。ADS 1278转换电路如图5,由FPGA提供控制所需的控制信号。

图5 基于ADS1278的AD转换电路

2.3 FPGA控制电路

FPGA是整个系统的控制核心,负责提供AD转换所需的时序信号,及转换数据到FPGA内部 FIFO所需控制信号,完成数据采集控制,实现采集数据到PC的传输。

ADS1278工作所需的相关控制信号由FPGA提供,如设置工作模式/数据输出格式,进行通道选择等,FPGA与ADS1278间关键端口的连接如图6所示。

图6 FPGA 与ADS1278控制接口电路

FPGA为EP2C8Q208C8,工作时钟为48 MHZ,采用3.3V/48MHZ有源晶振,其输出连接至FPGA的时钟CLK,其配置芯片为EPCS4N,用于保存FPGA的配置信息,程序启动代码。系统内存选用64M/SDRAM芯片HY57V641620ETP-7,用作程序运行空间,其地址、数据、控制信号都直接连接到FPGA的IO引脚,由FPGA内部的SDRAM控制核控制。

依赖于FPGA强大的计算能力,能够实现复杂高性能信号处理算法在地震数据采集系统中的应用,从而克服了单纯依赖ADC精度进行地震信号检测存在的瓶颈,有利于整个系统检测精度的提高。

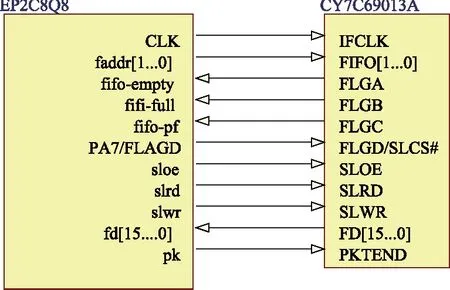

2.4 USB接口电路

USB接口具有高速、即插即用的特点,在高速数据采集系统中使用广泛。系统采用Cypress公司的CY7C68013A芯片进行USB接口设计,在Salve FIFO模式下,可选择同步或异步方式,为使数据传输更有效和可靠,采用异步方式。此时,CY7C68013A与FPGA完成如图7所示的关键引脚信号的连接,通过片选、写入/读取信号实现双向通信[8]。

图7 CY7C68013A与FPGA的USB接口电路

其中,IFCLK是时钟信号,由CY7C68013A芯片内部提供,FD[15…0]为16位双向数据总线,FLAGA/FLAGB/FLAGC为CY7C68013A内FIFO标志管脚,SLOE使能数据总线FD的输出,FIFOADR[1…0]用于选择和数据总线FO连接的端点缓冲区,SLRD和SLWR为FIFO的读写选通信号,FLAGD/SLCS# 为FIFO模式状态标志位/Slave FIFO模式使能引脚。

CY7C68013A使用24 MHZ晶振作为时钟输入,采用E2PROM芯片24LC64作为存储器,用于存放固件程序。需要注意的是,USB协议采用端点作为数据收发器,本系统使用EP2为上位PC机OUT端点,接收PC机传送的数据;EP6为IN端点,往PC机发送采集数据,将二者配置为1024 B的双缓冲、块传输模式。

3 软件设计

系统软件部分主要包括FPGA程序设计、系统固件程序设计、USB驱动程序设计、应用程序设计。

3.1 FPGA程序设计

FPGA程序主要完成AD转换的时序控制,以及FPGA和USB接口的传输控制。

3.1.1 AD转换时序控制

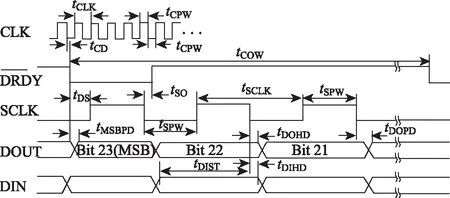

AD转换控制主要完成对ADS1278的时序控制,以读取ADS1278输出的数据。在SPI模式下,ADS1278的时序逻辑如图8。

图8 ADS1278工作时序图

当ADS1278数据转换完成,/DRDY变为低电平,通过SPI串行时钟SCLK的控制,FPGA从ADS1278的DOUT1引脚读取24位数据。具体的,在SCLK的第1个上升沿读取第1位数据;SCLK第1个下降沿后, /DRDY变为高电平,直至下一个数据准备好。在SCLK的下降沿后,第2位数据准备好,SCLK变上升沿,第2个上升沿时读取第2位数据,如此反复,直到数据的24位全被读取。据此时序图,将FPGA系统时钟分频,得到ADS1278需要的时钟,将时钟送入ADS1278即可实现FPGA对ADS1278的控制。

3.1.2 USB接口程序设计

由于ADS1278、FPGA、CY7C68013A的数据处理速度不同,为防止数据丢失,将数据暂存到FIFO中。本系统设计的AD转换数据随时被送到USB接口传送到PC,因此,不需要大的缓存FIFO,利用FPGA内部资源定制即可。本设计中,定制的异步FIFO是8bit×1024的存储单元,采用Altera的宏功能,通过quartus II中的MegaWizard管理器完成FIFO模块的配置。当FIFO中存储满1K字节数据时,USB接口即将数据传送至PC,直到把FIFO读空为止,停止读取数据,直到下一次FIFO满。

USB接口程序需要将FPGA内FIFO数据传给USB芯片,因此需要产生读/写控制信号实现双方通信。在异步Slave FIFO模式下,FPGA对USB微控制器的操作实际是对CY7C68013A提供的FIFO存储器的操作,采用读/写2个有限状态机完成对FIFO的读写操作[8]。

异步Slave FIFO写和读的操作类似,其中写操作的状态机设计如下:

S0:S0为初始化状态,当写事件发生,跳到S1;

S1:使FIFOADR[1…0]指向FIFO IN,即将FIFOADR[1…0]配置为’ 10’指向EP6,跳到S2;

S2: 若 “FIFO满”标志为假,即FIFO没满,则跳到S3,否则停在S2;

S3:送数据到数据总线,使SLWR有效,再置为无效,使FIFO写指针递增,跳到S4;

S4:若有更多数据传输,跳到S2,否则跳到S0。

3.2 USB固件设计

USB固件程序是CY7C68013A内部8051单片机工作程序,负责设备初始化、处理PC端各种设备请求,并与外围电路进行数据传输。Cypress公司提供了固件开发框架,只需在框架上完成USB描述符表,添加接收/发送数据及相关控制外围电路的代码即可[9]。固件框架提供了如初始化函数TD_Init(),重复调用函数TD_Poll(),设备工作状态配置函数TD_Suspend()等接口函数,在固件程序中添加这些函数,并在对应函数中添加代码就可实现相关功能。

根据固件程序开发流程[10],在TD_Init()中添加初始化代码,设置USB工作模式、选择端点、配置FIFO大小等。在异步slave FIFO模式下,为实现高速传输,CY7C68013A内部低速CPU不参与数据传输,端点在接收到FPGA的AD转换数据后,等待PC读取,USB芯片仅作为一个数据传输通道,读写 FIFO 由 FPGA 来完成,因此在TD_Poll()中无需添加用户代码[11]。

3.3 USB驱动程序设计

USB驱动程序是用户访问设备的接口,利用Cypress的驱动程序Cyusb.sys简化驱动程序编写。通过编写相应的安装信息向导文件,即.INF文件,用于查找合适USB设备的驱动程序。具体的,在CyUSB.INF中修改自己的PID/VID代码;当USB设备连接时,系统将根据硬件PID/VID代码查找INF文件中对应驱动,若未找到,则提示用户自己安装支持该USB的驱动程序。

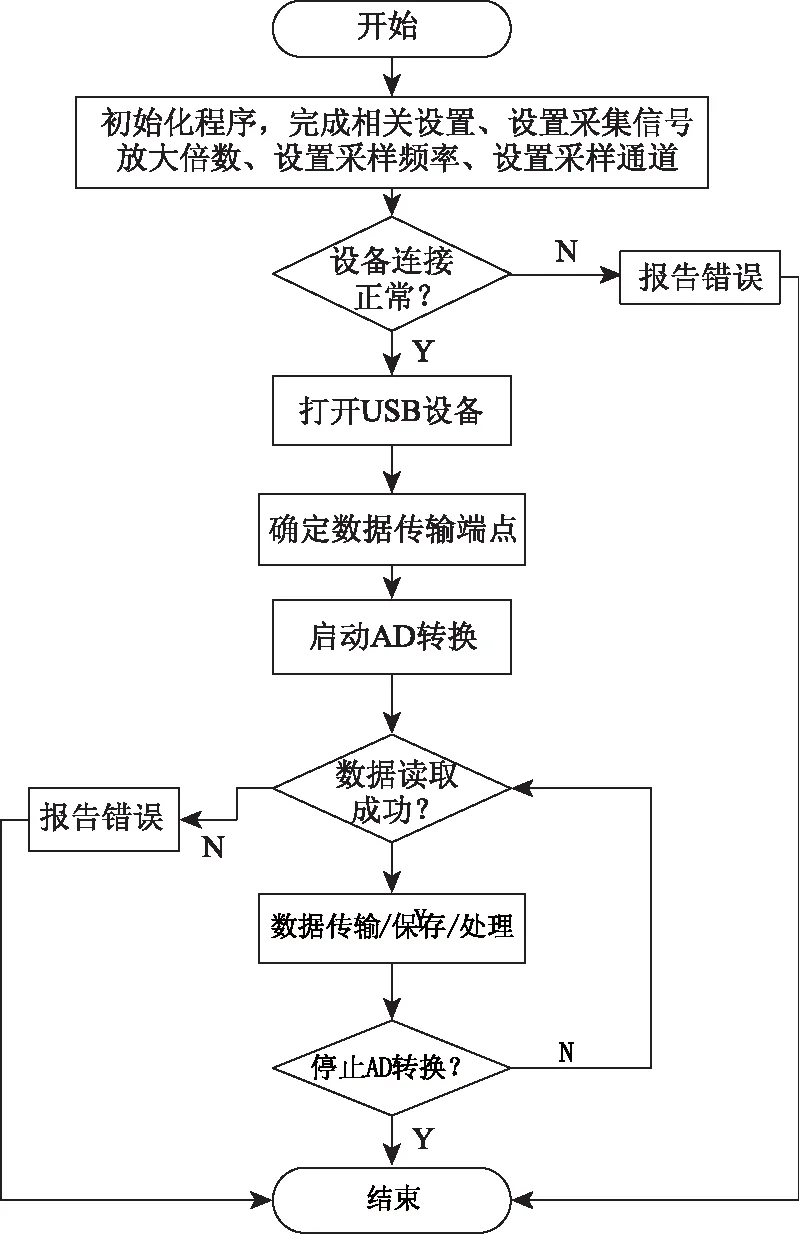

3.4 应用程序设计

应用程序以驱动程序为桥梁,实现对USB设备的控制和数据采集,具体流程如图9。应用程序是基于VC++,利用Cypress提供的CyAPI控制函数类库方法完成。在程序中加入CyAPI.h和CyAPI.lib,再调用CyAPI函数库中的基础函数完成USB应用程序的编程[12]。

图9 应用程序流程图

在该程序流程中,主要使用的是设备控制类CCyUSBDevice()下的open()函数打开USB设备,读取二进制数据,并对接收数据进行处理,而对USB的FIFO读写控制主要使用CCyUSBEndPoint类下的BeginDataXfer(),TimeOut(),WaitForXfer()函数,结束调用CCyUSBDevice()下的Close()函数。

4 系统测试

为测试系统的性能和可靠性,本文首先对系统短路噪声进行了测试;同时对函数发生器产生的对典型正弦信号进行采集,测量系统误差范围,并对通道间的一致性进行了测试;最后对实际的地震动信号进行了采集和显示。

4.1 系统噪声测试

为测试系统噪声,将系统输入端口直接接地采集系统短路噪声,并用Matlab 对短路噪声数据进行处理,单通道所采集的短路噪声序如图10所示,噪声均匀分布,系统短路噪声峰峰值在 70 μV以内,无明显直流偏移,且通道间的噪声峰峰值差异在20 μV 以内。

图10 单通道短路噪声序列

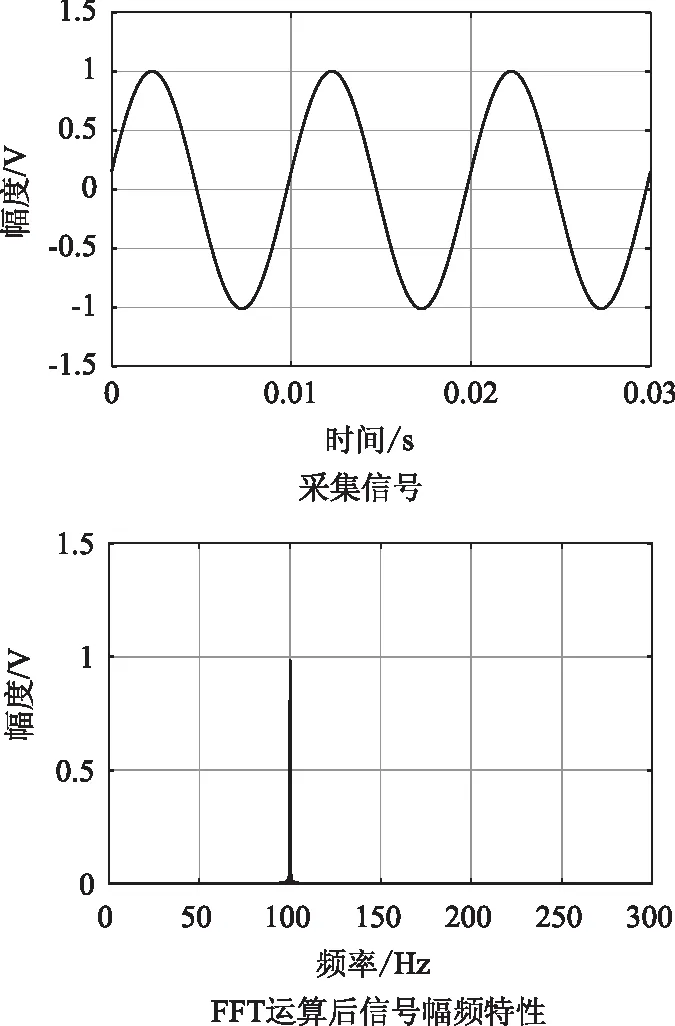

4.2 典型正弦信号测试

使用本系统采集函数发生器产生的典型正弦波进行测试,信号频率为100 Hz,输入信号范围为±1 V。如图11左侧所示,采集到的波形与信源波形一致,图11右侧是采集信号经FFT运算后的信号幅频特性图,如图所示,频率准确度高,表明系统可进行准确的信号采集。

图11 正弦波采集信号及FFT运算后信号幅频特性

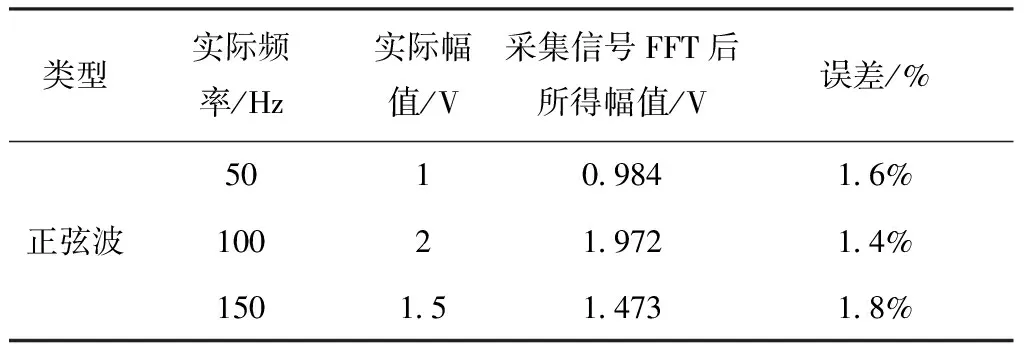

为测试系统误差,对函数发生器产生的正弦波信号进行采集,对采集信号FFT和求模值后的幅频特性,如表1所示,信号幅值的误差在1.8%以内,,表明系统具有较高的精度。

为测试通道间的幅值差异,对同一信号源,不同通道采集到的幅值最大差值为0.12 mV,表明多通道间具有较好的一致性。

表1 正弦波信号采集幅值误差

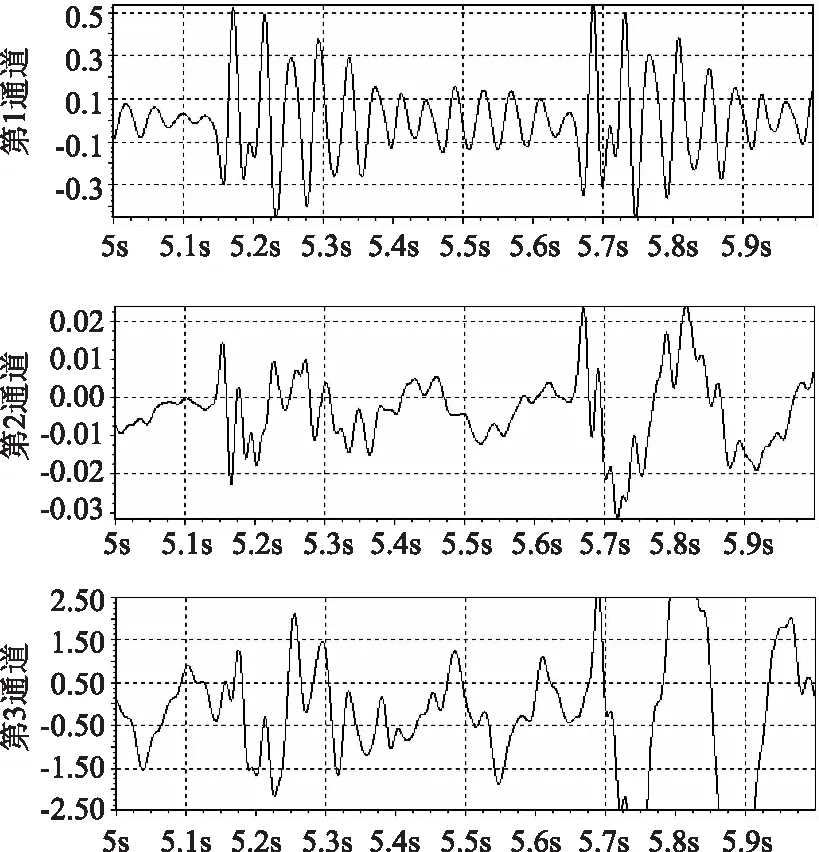

4.3 实际地震动信号测试

为进一步测试系统可靠性及性能,基于中国地震局工程力学研究所的三分量拾震器及本文设计的采集器,获取地面震动信号。如图12,当有人员经过时,采集器可实时获取地面震动信号,并清晰识别出地震动信号的波形幅度随脚步落地的变化。

图12 人员经过时的地面震动波形图

多次实验证明,研制的地震数据采集器可同步采集8通道数据,且该系统作为自研实验设备已被本校防灾减灾装备实验室的研究生用于实际的地震信号采集,采集数据准确可靠,可作为后续地震资料分析的基础,具有较强的实用价值。

5 结 语

基于FPGA的USB多通道地震数据采集器,提高了采集信号的抗干扰能力,以准确拾取微弱信号,并可实现多通道同时采集,大大提高传输速率。系统根据ADS1278的工作特性,以FPGA为主控制器,实现数据采集和控制;同时基于CY7C68013A,采用Slave FIFO模式,实现了PC与外设间USB接口的数据传输。系统可满足设计需求,不仅为高速、低成本、多通道的地震数据采集器研发提供参考,还可进行实际的地震动信号采集,具有较强的实用价值。需要注意的是,本系统侧重数据采集,下一步将对采集数据进行滤波和去噪,以进一步提升采集数据的精度。