基于ARM的嵌入式数据录取设备研制*

2018-10-08周明进卢再奇

周明进,卢再奇

(1.陆军装备部装备质量审价中心,北京 100072;2.国防科技大学自动目标识别国家重点实验室,湖南 长沙 410073)

1 引言

某型装备随装配置的文件记录设备,可实时记录装备工作和状态信息,用于事后分析评估装备操作和性能,类似飞机的黑匣子。因该设备存在存储器容量小(记录时间短)、数据易丢失、无通用数据输出接口、事后判读分析数据依赖人工(周期长)等弊端,极大地妨碍了装备能力的发挥。为提高数据记录可靠性和实时掌握装备技术状态,研制了嵌入式系统,对该设备进行信息化改造。研制过程中需考虑:(1)电气兼容及信号时序;(2)联机检查;(3)实时数据传输和海量存储;(4)关键数据记录完整性;(5)输出信息实时解析(另文涉及)等问题。针对上述问题进行了系统方案设计和实现,经实装使用,该系统达到了设计要求。

2 嵌入式系统方案设计

FPGA(Field-Programmable Gate Array)由于使用的灵活性,功能可重构,接口配置可在线修改,已越来越多地用于系统原型机开发和嵌入式系统中。ARM微处理器已被广泛用于许多嵌入式系统中,具有功能全面、设计开发资源众多、性价比高的优点。ARM微处理器与嵌入式操作系统配套,可以完成板上独立功能系统,不需要外部控制,即可以自主实现任务规划[1]。本设计采用FPGA+ARM的体系结构,配以必要的外部器件,构成了嵌入式系统,实现了数据的完整正确录取处理。其总体结构如图1所示,包括电源部分、FPGA电路、嵌入式处理模块和上位机等。

Figure 2 Signal timing sequence of data reads and writes by chipscope图2 chipscope观察数据读写时的信号时序关系

Figure 1 System structure diagram图1 系统总体结构框图

来自装备的电源向嵌入式系统和备用电池供电。在电源非正常中断时,掉电保护控制电路打开备用电池,维持嵌入式系统供电一段时间,确保装备数据完整存储。FPGA模块对输入信号进行采样、整形处理;内置数据缓存模块用于系统联机检查及数据收发;内置测试单元,方便系统开发过程中参数测试和故障定位。嵌入式处理模块上运行嵌入式操作系统,完成输入数据的本地存储处理、远程网络交互等工作。上位机实现系统控制、数据分析和可视化处理。

针对系统资源要求,ARM芯片选择了基于ARM920T内核的S3C2440微处理器[2],FPGA芯片选定VIRTEX-II系列的XC2V250[3]。

3 系统设计

3.1 随装设备接口信号分析

随装记录设备接口由数百根引线组成,包括多种类型电源线、数据信号线、控制信号线等。由于缺乏设备接口详细的参数资料,因此需要通过在线测试才能确定设备接口各管脚的功能和时序。

对于数据线和控制信号线,为了掌握其在各种逻辑状态下的相互关系,搞清楚其功能作用,需要对其时序进行分析。传统上,我们利用示波器或者逻辑分析仪测试,在几百根信号线中测试,信号接线实非易事。另外,也不可能同时测量各种工作条件下信号之间的时序关系。使用chipscope在线逻辑分析仪软件,无需进行任何的外部探测或修改便可获取FPGA中任意的内部节点或I/O 引脚的状态,在整个设计过程中以零成本和系统级的速度实时捕获和显示FPGA中的信号,对系统进行观测和调试[4]。使用chipscope观察的部分信号之间的关系如图2所示。图2a是chipscope显示的装备读取存储器数据时的部分总线信号波形,图2b是chipscope显示的装备写存储器时的部分总线信号波形。

我们利用chipscope软件,通过在线测试,获取了大量的波形和数据,为掌握接口信号之间的时序关系、数据的正确录取打下了良好基础。

3.2 信号采样整形和时序逻辑设计

装备的接口电路由分立元器件和小规模集成电路组成,与随装数据记录设备通过线缆连接。从测量结果看,信号受噪声影响大,波形畸变严重、时间摆幅大。为保证研制设备正确接收数据,设计与装备信号电平兼容的接口驱动电路,根据测试结果在FPGA中研制信号采样整形和时序电路。信号采样整形包括输入输出信号的正确采样成形;时序电路保证数据记录时,与装备交互逻辑正确。输入信号采样要求正确采集到输入信号的稳定电平,形成适合FPGA内部处理的逻辑电平和宽度,排除由于信号畸变和噪声引起的信号误判。这里采用双边沿检测方式,只有符合一定宽度的输入脉冲才被FPGA采样,形成有效信号;输出信号的形成需要保持正确的时序,且时序余量保证在设备允许的偏差范围之内。因此,使用FPGA产生时序信号时,要留有足够的时序余量,适应原设备的时序偏差,同时又要保证数据传输正确。数据记录设备时序操作包括工作和检查状态下读写存储器、记录和读写当前存储器地址、存储器检查、存储器空满指示等。

根据各输入输出信号之间的时序关系,部分信号的状态机如图3所示。

Figure 3 State machine of interface control signals图3 接口控制信号状态机

该状态机在FPGA内部实现,完成装备与记录设备之间的信息交互和数据的输入输出。对于有效数据,将按序存储,同时更新服务单元地址内容;对于测试数据,按序存储但不更新服务单元地址内容。

分为多个状态,各状态功能如下:

(1)memidle:判断双沿检测电路中是否送来有效脉冲,进行状态切换;

(2)ho_state:检测WR信号,高时进入写状态;低时,准备好地址和使能信号,进入读状态;

(3)write_mem:准备好地址、数据、控制信号,进行数据缓存写操作;

(4)pabtest:在PAB为高电平时,为工作状态,更新服务单元;为低时,为检查状态,返回到memidle状态;

(5)write_surv:工作状态时,将当前地址写入服务单元;

(6)read_hold:当检测为读数据状态时,将缓冲存储器的地址和控制信号延迟1个脉冲周期送出;

(7)read_mem:读FPGA中缓存内容,更新输出寄存器;

(8)addr_state:当地址计数脉冲信号到来时,更新地址寄存器,存储器满指示信号及半满指示信号依据地址寄存器数据更新;

(9)send:数据有效信号,向设备指示有效数据已输出到数据线上。

3.3 联机检查功能设计

通过测试和功能分析可知,装备联机检查分为存储器自检和记录功能检查两个部分。首先,装备输出互补的固定数据填充存储器每一位,然后回读比较存储器数据,如一致,则装备接口控制电路向中心计算机报告存储器正常;第二步,在存储器正常的情况下,中心计算机发出特定编码数据组到存储器,回读并译码该信息,中心计算机确认时间及内容无误后,向系统发出记录设备正常指示。研制设备必须兼容该过程,以保证与中心计算机进行有效的数据交换。随装记录设备的存储器容量为几十KB,在每次开机前可做到每位检查。研制设备将数据实时输出,外接存储器已扩展为海量存储器。故中心计算机已不可能对扩展后的存储器每一位进行检查,也没有必要。因此,在FPGA中开辟一块缓存区,用于装备数据记录功能正确性检查。该块缓冲区的设置考虑了FPGA芯片存储资源和数据流特点,为保证输入和输出互相不影响,缓存区设置为FIFO(First Input First Output)模式。

3.4 多速率数据传输存储模块设计

研制设备除保留原系统的数据存储功能外,信息化改造过程中,还增加了实时输出、远程网络输出和海量存储功能。鉴于研制系统各组成部分数据传输速率差别大,从数据传输稳定性和提高系统工作效率考虑,将数据传输模式设计为非同步模式,不同速率数据流采用存储器缓存结构实现连接。为适应多级传输速率需求,系统使用了多个数据缓存区。数据缓存模块包括:中心计算机与FPGA的数据缓存模块;FPGA与ARM的数据缓存模块;FPGA中串口收发数据缓存模块;网络传输数据缓存模块;USB(Universal Serial Bus)存储器和板载固态存储器NAND flash数据缓存模块等。如图4所示。

Figure 4 Distribution of data storage图4 数据存储分布图

图4中,FIFO为装备联机检查及实时数据输出缓存区。联机检查时,FIFO用于装备数据传输及存储正确性检查。工作时,当FIFO检测到数据输入时,通过串口实时输出数据;FPGA中的双口存储器,一端接装备总线,一端接ARM数据总线。双口存储器划分为两个数据缓冲区,采用乒乓访问机制,当一个缓存区数据写满时,通知ARM取数,同时,装备写另外一个缓存区。FIFO和双口存储器的设置解决了装备和研制系统数据传输速率不一致的矛盾,实现了数据操作隔离,提高了传输可靠性。由于串口和ARM读取数据速率大于装备平均输出数据速率,因此能够保证存取数据逻辑正确进行,不会丢失数据;ARM内部的数据缓存区也设置为双口存储器形式,作为USB海量存储器和远程网络输出的数据缓存,USB存储和网络传输均按帧操作,一帧数据量设计为双口存储器乒乓操作一次数据输出量。当双口存储器数据量达到一帧后,驱动USB接口存储数据及网络传输。NAND flash存储器为板载大容量非易失存储器,可根据需要存储设备数据,事后读取。SDRAM(SynchronousDRAM)用于大数据量存储和系统扩展。

3.5 串口输出模块设计

图4中,串口输出模块与网络和USB接口控制模块一起,构成研制系统数据输出的3个通用接口。串口输出模块在FPGA中实现,独立于ARM系统。当ARM系统由于某种原因造成网络和USB模块不能正常工作时,还能够保证装备数据通过串口正常录取,极大地保证了研制设备的应急使用能力。

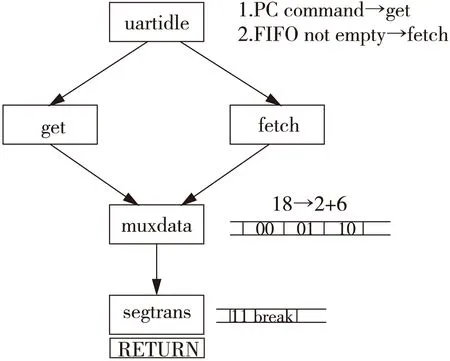

由于设备输出为18 bit的数据格式,串口将18 bit数据分成三次发送。该串口实现状态机如图5所示。

Figure 5 State machine of transmit-receive data of UART图5 串口收发状态机

各状态功能如下:

(1)uartidle:等待状态。当检测到从计算机传输过来的数据时,进入通信测试状态,当检测到FIFO非空时,启动FIFO中传数过程。

(2)get:通信测试状态。用于串口通信调试和测试,具有校验和传输测试功能,正常时,向计算机返回功能状态码。

(3)fetch:取数状态。从FIFO口中取出18 bit数据,进入数据组装状态。

(4)muxdata:多段数据准备状态。由于输入数据为18 bit,需要3次才能传输完一个数据,根据次序码,进行数据区段设置。当次序码为11时停止数据传输。

(5)segtrans:判断次序码内容,触发UART传输数据。

3.6 掉电保护电路设计

当装备非正常断电时,有时意味出现严重问题,断电时刻的数据是正确有效分析装备故障原因的重要保证。原设备采用干电池供电,当电池电量不足或者接触不良将导致存储器数据丢失。我们设计了断电保护电路,在供电中断时,仍然能够为研制设备提供超过15 s的供电时间,用于数据存储和传输。断电保护电路中的备用电池采用大容量法拉电容模组实现,使用寿命长,可靠性高,直接焊接于电路板上。当设备工作时,在线向法拉电容模组充电,解决了原设备电池容量下降和接触不良的问题。

掉电保护电路框图如图6示。当供电中断时,切换到备用电池供电状态。此时,FPGA检测到处于备用电池供电状态,产生中断信号,触发中断服务程序,完成缓存区数据存储。

Figure 6 Principle diagram of power-fail protection图6 掉电保护电路原理图

图6中,掉电保护电路分为掉电检测、电源切换、备用电池控制、数据保存等几个功能部分。当电压比较电路检测到VCC-IN下降到阈值电压时,输出掉电信号到FPGA。此时,DC-DC输入端切换到大容量电容供电阶段,保证在备用电池供电前,DC-DC模块正常工作。在FPGA中,掉电信号通过整形及与其他信号逻辑合成,形成备用电源切换命令及到ARM的数据保存中断信号。收到电源切换命令后,备用电池与DC-DC模块连通。ARM识别到中断信号后,将缓存中数据及时传输转存。经测试,大容量电容有效放电时间约200 ms左右,满足电源切换时间要求;备用电池能够提供15 s以上的有效供电时间,保证系统将数据安全转存。

3.7 嵌入式处理模块设计

嵌入式处理模块由硬件平台和相应的嵌入式操作系统及应用软件组成,硬件平台基于ARM920T内核的S3C2440A微处理器设计,外置相应的数据和程序存储器及其他外围器件。嵌入式操作系统移植了U-Boot[5],应用软件实现了USB和网络接口及其他功能。嵌入式处理模块组成如图7示。

Figure 7 Block diagram of embedded processing modules图7 嵌入式处理模块组成框图

本系统在U-Boot的基础上采用以无限循环轮转形式运行的管理调度程序作为后台程序,以中断方式来发送数据准备就绪信号,通过调用中断服务程序ISR(Interrupt Service Routine)来处理具体应用的操作模式,保证系统的实时性,如图8示。

Figure 8 Software working flow chart图8 软件工作流程图

软件开发主要包括以下几个方面工作[6 - 8]:

(1)U-boot移植;

(2)USB主机接口;

(3)网络传输。

4 系统测试

4.1 实验室测试

利用模拟板模拟装备数据输出过程,测试研制设备功能是否正确。这里使用两套系统测试数据记录和系统联网功能,系统连接如图9所示。图9中,每套系统由数据模拟板和主板组成,主板上连接USB存储器、网线及串口数据线。两套系统的网络线连接到一台上位机上。

Figure 9 Picture of real products in the network test图9 联网测试实物图

实验结果显示在上位机上,如图10所示。

Figure 10 Data receive results图10 数据接收结果显示

图10a显示设备工作状态及工作时间,显示U盘和数据接收正常;图10b为记录的数据文件,通过分析比较,文件命名规则与要求一致,文件内容与模拟电路发送数据一致,表明研制设备数据记录功能正确,设备满足联网要求。

4.2 实装测试

实装测试包括接口电气兼容性测试和数据记录完整性测试两个部分。研制设备与装备的122针输出电缆连接,装备加电,确认装备能够正常启动;装备开机进入工作前检查状态,存储器自检灯和记录设备检查灯亮,显示研制设备电气兼容性测试和功能检查通过。

装备先后与原记录设备和研制设备连接,设定相同的测试程序和测试数据;将两者记录的数据进行比较,记录数据个数和数据判读结果均一致。这表明研制设备在功能上可完全取代原设备。

通过实验室和使用单位实装测试,表明研制设备完全达到了信息化改造目标,实现了多装备输出数据的实时、可靠录取和传输存储。

5 结束语

本文针对某装备信息化改造的特殊要求,结合ARM和FPGA 各自的优势,研制成功嵌入式实时数据记录处理系统。该系统实现了接口灵活可靠、数据传输格式多样、数据掉电保存等功能,保证了数据的正确录取和传输。该系统已应用于实装,完全达到了设计要求。其中,数据输出通道冗余设计和掉电保护电路在系统出现意外情况下的数据保全中发挥了突出作用。文中相关设计思想对已有设备的信息化改造工作具有参考意义。