基于等效采样的交流毫伏表实现

2018-09-27刘凛韦邓文迪

刘凛韦, 邓文迪

(华中师范大学 物理科学与技术学院,湖北 武汉 430079)

0 引 言

随着测量仪器的不断发展,对仪器的测量频率要求越来越高。虽然交流毫伏表对频率的要求较低,但也会时常测量超过1 MHz频率的交流信号。如果按照传统采样方法设计10 MHz的交流毫伏表,则需要采样速率很高的模/数转换器(analog-to-digital converter,ADC)芯片满足采样需求,将使得交流毫伏表的制作成本大大提高。目前市场上主要有2种方法设计交流毫伏表:采用模拟电路的方式直接对信号进行滤波得到直流分量进而得到交流信号有效值;通过模/数(analog-to-digital,A/D)转换对模拟信号数字化,算出交流信号有效值。2种方案均不能对较高频率的交流信号进行测量,本文选用顺序等效采样的方式,将采样信号的频率提高到10 MHz,提高交流毫伏表测量频率。

1 方法对比

1.1 计算有效值方法

计算交流信号有效值主要有:直接求得交流信号的峰峰值,通过峰峰值来转化计算交流信号的有效值;通过一组有序的采样点进行积分求交流信号的有效值。积分的方法需先将采样点按照相对Trig信号时间间隔大小进行排序,再对采样点围成的区域进行积分运算求出面积,进而求得交流信号的有效值[1]。具体原理如图1所示。

图1 积分求有效值原理

2)通过采样点和采样时间求出分割区域面积为

(1)

3)通过求和得出正弦波的有效值为

(2)

考虑到在采样的过程中会出现一些噪声,直接采样求峰峰值可能会产生较大的误差,因此,选用积分求有效值的方法来计算交流信号的有效值[2,3]。

1.2 等效采样方法

等效采样主要包括等效随机采样和等效顺序采样,原理参见文献[4~12]。由于等效随机采样在采样时没有规律性,在后期需要对采样点进行重新排序,且需要求出排序后相邻采样点的时间间隔,才能够积分计算出交流信号的面积,使后期数据处理的工作量过大。而采用等效顺序采样的方式,虽然在采样时需要控制精准的采样起始时间,但后期数据处理时不仅免去对采样点排序的麻烦,且由于等效顺序采样的采样点间距相同的特性,可将式(2)简化为

(3)

可知,在等效顺序采样的方式下,仅需要得到1个正弦波的周期内的采样点和采样点数即可求出信号的有效值,大大减小了数据处理的工作量。因此,系统选用了等效顺序的采样方式。

2 系统设计

2.1 系统总体设计

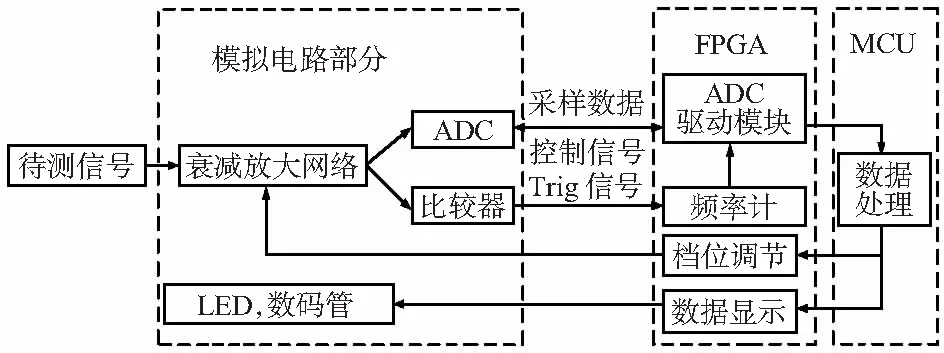

整个系统采用了FPGA+MCU的方式来实现交流毫伏表的功能[13]。FPGA用于控制时序逻辑,外部电路等[13],如驱动ADC芯片,控制前端衰减放大网络等;MCU用于对采样后的数据进行处理,包括对采样得到的数据进行积分求平均值,求DB值等[15]。整体框图如图2所示。

图2 系统整体框图

待测信号首先通过衰减放大网络后,得到一个合适的幅度的信号,信号分成2路,一路送给ADC芯片进行采样,得到ADC的采样值,一路送给比较器产生方波信号。方波信号作为FPGA部分的触发信号,以实现等效采样的算法,同时实现FPGA对待测信号频率的测量。ADC采样到的数据经MCU处理后,得到待测信号的有效值,再判断是否需要切换档位等,最后将档位值,有效值反馈到FPGA,FPGA对衰减放大网络的档位进行调节并最终显示结果。

2.2 等效顺序采样实现

2.2.1 等效顺序采样在不同频率时的处理

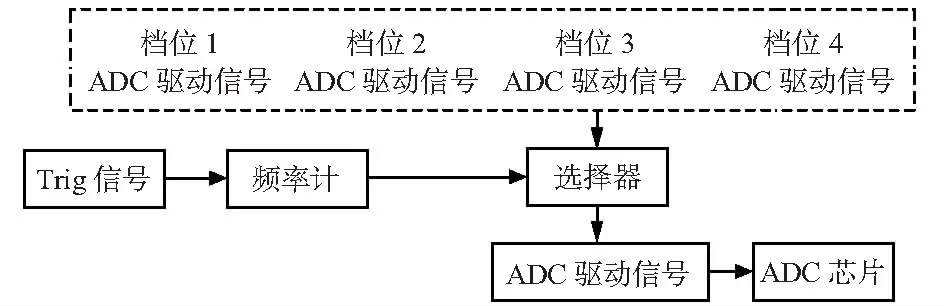

等效顺序采样在每个周期仅采样1个点,时间利用率很低。当测量高频信号的时候,需要将两个等效采样点的时间差td设置很小,而测量低频信号时,如果还采用高频时的方式,则会导致采样结果的更新率过慢。假设1个周期需要采样20点才能精确算出最终的采样结果,那么测量10 MHz的信号需要将td设置成为5 ns,此时计算待测信号的有效值仅需要20个待测信号周期,即2 μs,但测量1 kHz的待测信号时,则1周期会等效采样200×103个点,此时计算待测信号的有效值则需要200 s的时间,更新率过慢。因此,ADC的采样驱动需要根据待测信号的频率来分档位处理,当待测信号频率较高时,选择用等效顺序采样的方式,当待测信号频率较低时,选择直接采样的方式,换挡部分结构框图如图3所示。

图3 ADC驱动档位选择示意

ADC驱动的档位选择主要由FPGA部分完成,FPGA对比较器产生的方波信号进行频率计算,测得的频率值作为选择器的判断依据,其中产生了4路不同档位的ADC驱动信号,选择器选择合适的一个档位作为当前的ADC驱动输出。

2.2.2 等效顺序采样驱动

等效顺序采样驱动如图4所示。

图4 等效顺序采样驱动

等效顺序采样所需要的最高采样时钟为200 MHz,所以先通过锁相环(phase locking loop,PLL)将系统时钟进行倍频处理。用其作为等效顺序采样驱动模块的时钟,以控制精准延时。当ADC芯片进入正常工作模式后,则等待触发信号。当触发信号到来后,计数器对开始200 MHz时钟计数并不断与cnt2比较,当满足cnt1≥cnt2时,ADC芯片开始采样,cnt1清零,cnt2加1。每次采样结束后再次等待Trig信号,以此实现了采样点与Trig信号时间间隔依次增大的效果。

2.3 采样数据的处理

由式(3)可知,测量待测信号的有效值需要已知1个周期内的采样值和采样点数。采样点的采样值可由FPGA读出后直接传给MCU,而1个周期内的采样点数则需要通过计算求得。由于等效采样相邻的2个点的时间差td相同,则可以通过频率计测得的频率f和时间差td求得一个周期内的点数,即n=1/ftd,将n代入式(3)中后可以求得最终待测信号有效值结果。

3 测试与结果分析

3.1 等效顺序采样验证

在输入信号频率为1 MHz时,将采得数据提取后,用打点的方式还原波形,发现除了有少量噪声点外,整体达到了等效采样的目的,打点还原的波形如图5。

图5 还原波形

3.2 有效值精度测试

本文采用的是8位ADC,所以系统的精度不是很高。实际测量数据发现在不同频率档位切换时,会导致误差偏大,分析原因由于此时采样点数过少,误差导致偏大,但是所有误差均满足在3 %以下。500 mVrms信号在不同频率下测量值如表1所示。

表1 500 mVrms在不同频率下测量值

4 结 论

用等效顺序采样的方法实现了交流毫伏表的功能,可以大幅度减小ADC芯片的成本,使采样率1 MHz的AD芯片等效达到10 MHz的等效采样率;用积分的方法求有效值,可以有效避免噪声,相比于随机等效采样而言,准确度大大提高,且可以测得各种不规则形状信号的有效值。