应用于硅微机械谐振式传感器的频率计

2018-09-19黄荣玉牛文举韩建强

黄荣玉,牛文举,韩建强

(中国计量大学机电工程学院,杭州 310018)

0 引言

目前,MEMS传感器由于其巨大的经济效益和广阔前景正处于快速发展时期。MEMS传感器具有重量轻、体积小、成本和功耗低,易于集成和可以大规模批量生产等优点。广泛应用于武器装备、惯性导航和汽车安全等领域,是关系国家安全和经济建设的基础元器件之一[1]。微型传感器按照敏感信号的测量方式不同,分为压阻式[2],电容式[3],压电式[4]和谐振式[5]等不同类型。在这些微传感器中,硅微谐振式传感器具有精度和分辨率高、功耗小、动态范围宽以及输出信号为数字信号的优点。硅微谐振式传感器直接输出频率信号,在传输过程中不易产生失真误差,可以直接和数字接口连接。由于谐振式传感器输出为频率信号,这对频率信号的测量精度提出很高的要求,而测量精度的提高依赖于频率计性能的提高。

目前测量频率的方法一般有周期测量法,频率测量法和等精度测量法等[6]。周期测量法是在待测信号的一个周期内,通过测量标准信号的上升沿个数来计算出待测的频率。这样会引入标准信号个数的±1个字误差[7]。同时周期测量法只适用于低频、中频下的测量。在高频下,测量的误差非常大。频率测量法是通过在设定的闸门时间内,测量待测信号与标准信号的上升沿个数来计算出待测频率。由于闸门时间不是待测频率和标准信号周期的整数倍,这会引入待测信号和标准信号上升沿个数的±1个字误差。等精度测量法[8]是先给定一个预置闸门时间,当待测信号的上升沿或者下降沿到来时,打开预置闸门开始对待测信号和标准信号同时计数。当预置闸门时间结束后,只有待测信号上升沿或下降沿到来时,才同时停止对待测信号和标准信号的计数。频率的测量开始与停止都是在待测信号的上升沿或者下降沿完成,消除了待测频率计数的±1个字的误差,只有标准信号的±1个字的误差。但是等精度法只适用于测量高频,若要测量低频,预置闸门时间需要设置很长的时间。例如要测1 Hz的频率,预置闸门时间至少要设置1 s,这样增大了测频响应时间,大大降低了测频的效率。

由于周期测量只测量待测信号的一个周期或多个周期,但是测的周期个数是一个定值,不随待测信号的频率变化而变化。因此随着待测频率的升高,测量精度下降,所以限制了测量频率的范围。针对这一弊端,设计了一种基于FPGA的测频周期自调整频率计。

本文设计的频率计先在一个待测信号周期内,对标准信号的上升沿进行计数,粗略计算出待测信号频率和周期。然后对待测信号的周期进行调整,对标准信号的上升沿重新计数,精确测量出待测信号的频率。该频率计不仅提高了测量频率的精度,而且体积小,价格便宜,具有非常好的应用前景。

1 系统结构和原理

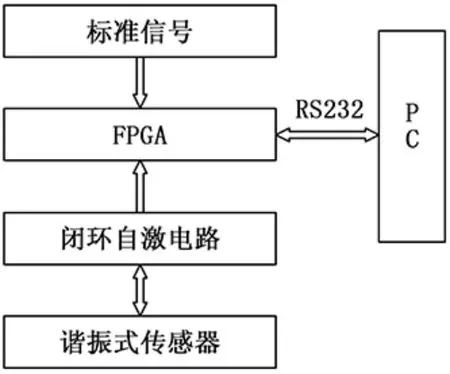

测试系统由谐振式传感器、闭环自激测量电路、FPGA采集模块以及PC上位机四部分组成,系统组成框图如图1所示。

图1 频率计结构框图

谐振式传感器使用微桥谐振器作为敏感元件。采用电热激励,压阻检测的激励检测方式。即给在位于谐振梁中间位置的激励电阻上加热,通过局部加热使谐振梁的结构产生形变,引起谐振梁的振动。当谐振梁振动后,位于谐振梁根部的惠斯通电桥上的电阻会因为振动产生形变,从而导致阻值发生改变,通过检测压敏电阻的阻值变化来检测振动。

测试过程中,先使用闭环自激电路[9]让谐振器处于闭环自激状态,闭环自激电路的输出信号为频率信号。利用FPGA对输出频率信号进行测量和采集,最后将测量的频率信号经过RS-232串行通信接口送入PC上位机。上位机使用Visual C#进行操作界面的软件设计,实现频率数值的实时显示和储存。

本文设计的频率计测量范围为1 Hz~2 MHz。由于频率计测量频率的精度直接决定谐振式传感器的测量精度,该频率计全量程内测量精度可以达到10-7数量级,相比于六位半万用表等传统测频工具,测频精度有了明显的提升。

2 系统硬件设计

2.1 FPGA开发板

FPGA(现场可编程门阵列)的开发区别于单片机,它是通过硬件语言来描述的,并且以并行运算为主。FPGA是在CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路 (ASIC)领域中一种半定制电路出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。它是当今数字系统设计的主要硬件平台。本文设计的频率计采用的FPGA控制模块是型号为AX301的黑金开发板平台。此款开发板搭载的主芯片是ALERA公司的CYCLONE IV系列型号为EP4CE6F17C8的FPGA主芯片。AX301开发板通过USB供电,用MINI USB线将开发板跟电脑的USB连接,按键电源开关,可以给开发板供电。其数字工作电压为3.3 V和1.2 V,板载晶振为50 MHz,晶振输出连接到FPGA的全局输入时钟管脚 (CLK1管脚E1),这个CLK1可以用来驱动 FPGA内的用户逻辑电路,用户可以通过配置FPGA内部的锁相环来分频或倍频实现其他频率的时钟,从而提高工作速度。

2.2 RS-232串行通信

RS-232是现在主流的串行通信接口之一,它被定义为一种在低速率串行通信中增加通信距离的单端标准。当它传送数据时,只需要一条传输线就能正确的将数据顺利传送到对方,因此叫做异步传输。由于RS-232是一种串行通信,故需要在软件中设置包括波特率、奇偶校验和停止位等多项设置。本设计波特率为128000、奇偶校验位为NONE和停止位为1。采用FPGA与PC机通信的主要程序模块如表1所示。

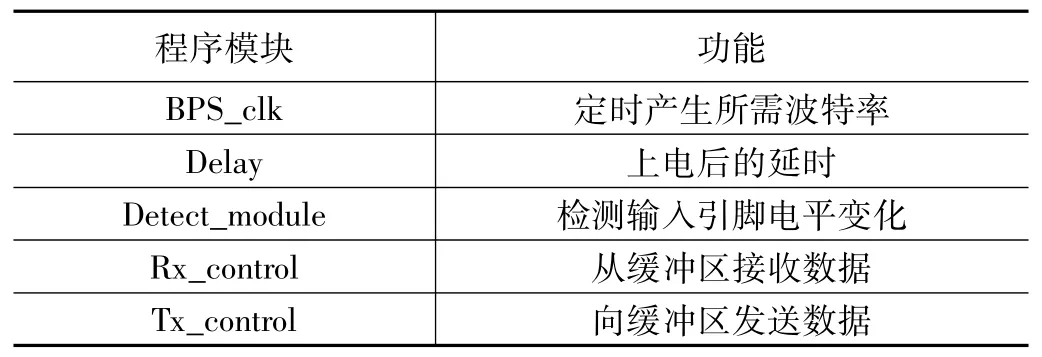

表1 FPGA与PC机通信的主要程序模块

向缓冲区发送数据通过与RS232接口相连,将从闭环自激电路中输出的频率信号数据传输到PC上位机,并实时显示出来。

3 系统软件设计

3.1 软件设计思路和编程方法

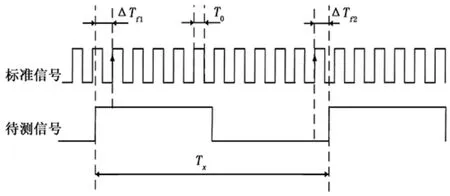

先用标准信号对待测信号的一个周期进行计数,预估算出待测频率大小,原理如图2所示。

图2 周期测频原理图

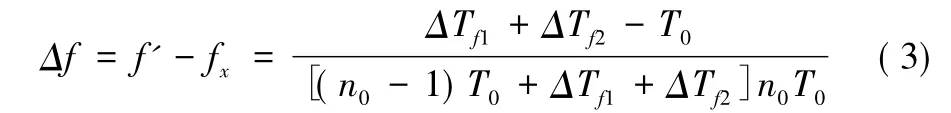

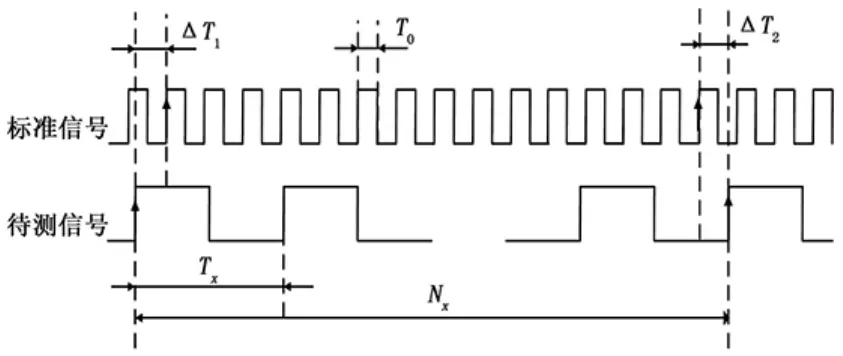

假设标准信号的周期为T0,在待测信号的一个周期内,标准信号的上升沿个数为n0,待测信号的周期为Tx,因此待测频率fx为:

其中,ΔTf1和ΔTf2为测量时的误差。调整后的待测信号频率f'为:

频率的误差为:

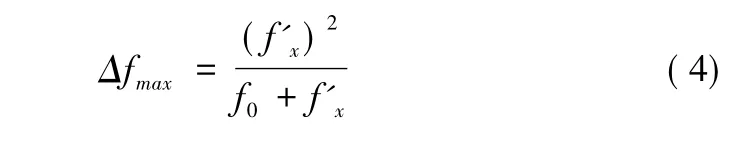

由 (3)式可得调整后的预估算频率的最大误差和最小误差分别为:

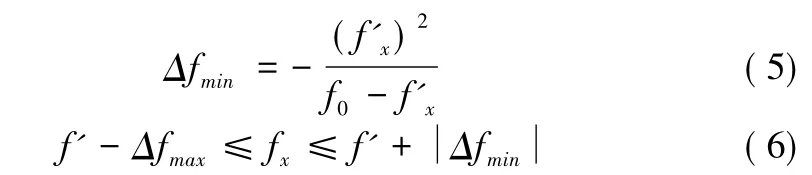

预估算待测频率的大小后,程序开始进行对待测信号的频率精确的测量,其测量频率时序图如图3所示。

图3 精确测量频率时序图

Nx是调整后需要测量的待测信号的上升沿个数,标准信号的上升沿的个数设为N0。

待测信号的真值为:

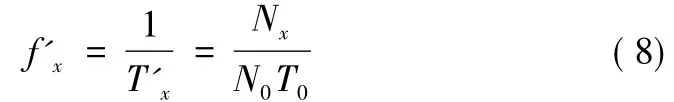

其中,ΔT=ΔT1+ΔT2调整后的待测信号的频率f'x为:

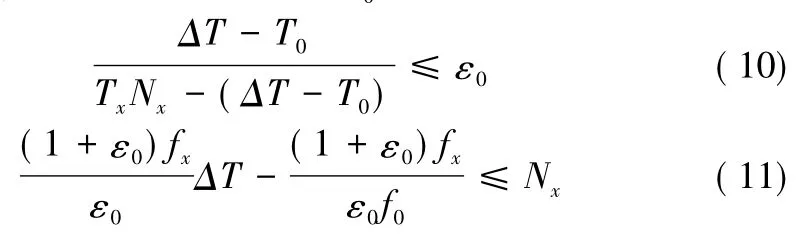

待测信号的频率的相对误差为:

设频率计测量的相对误差为ε0

由 (11)可知,Nx随ΔT的增大而增大,ΔT最大值为2T0。因此可得出调整后需要测量的待测信号的上升沿个数Nx,待测频率的真值fx、频率f0和在待测信号一个周期内标准信号的上升沿个数n0的关系,如式 (12)所示:

3.2 软件实现流程图

FPGA程序使用verilog语言进行编写,使用quartusⅡ软件进行编译。Quartus II是 Altera公司的综合性 PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Descrip-tion Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

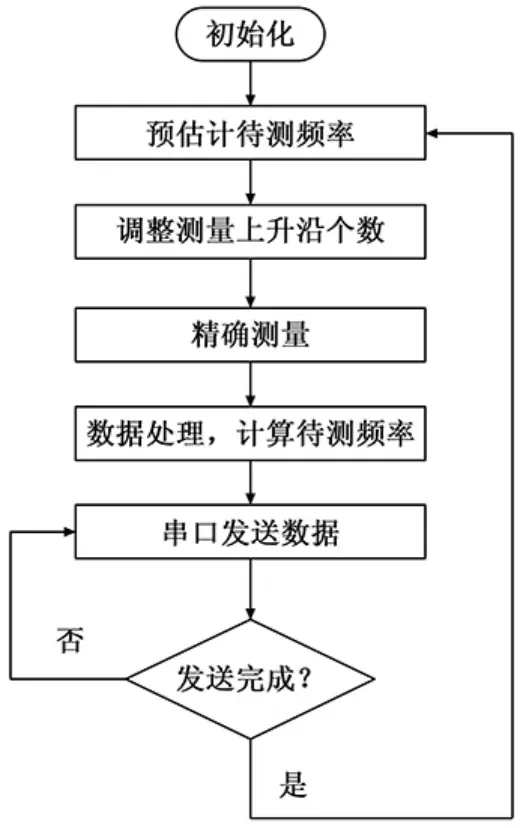

程序的流程图如图4所示。软件程序主要由四大模块组成,分别为预估算待测信号模块,自调整待测信号周期模块,精测量频率模块,数据处理和串口数据输出模块。首先是对程序进行初始化。然后预估算待测信号模块初步测量待测信号的频率和周期,在待测信号一个周期内,对标准信号的上升沿进行粗略地计数。所测出的上升沿个数n0再传输到自调整模块中。自调整模块根据n0的大小,计算出需要测量的待测信号周期个数Nx。然后再把Nx传递到精测量模块。在待测信号的Nx个周期内,精测量模块对标准信号的N0上升沿进行计数,计数结束之后。再把标准上升沿个数N0传递到数据处理模块,通过对Nx和N0两个数据进行处理,计算出待测的频率。然后将待测的频率传递到串口数据输出模块将频率传输到上位机并显示和储存待测信号的频率。发送结束后,程序再次对待测信号进行预估算,进入下一次的频率测量。

图4 FPGA测频程序流程图

3.3 PC上位机设计

为了实时的显示出采集的频率,FPGA将计算的频率数据传输到上位机,通过上位机对接收的频率进行处理后实时的显示出来。该设计的上位机采用Microsoft公司的Visual C#开发平台进行开发。设计的频率系统操作界面如图5所示。该上位机操作简单界面简洁,不仅能将采集的频率实时显示出来,也能将采集的频率进行缓存或者保存为TXT文档进行后期查看等操作。

图5 频率显示窗口

4 实验结果与分析

4.1 测量方波信号

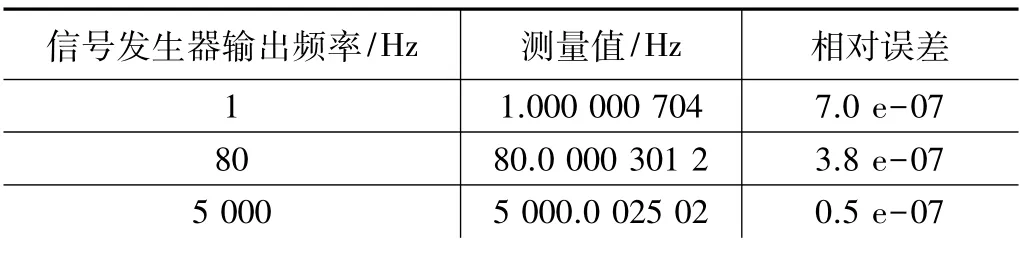

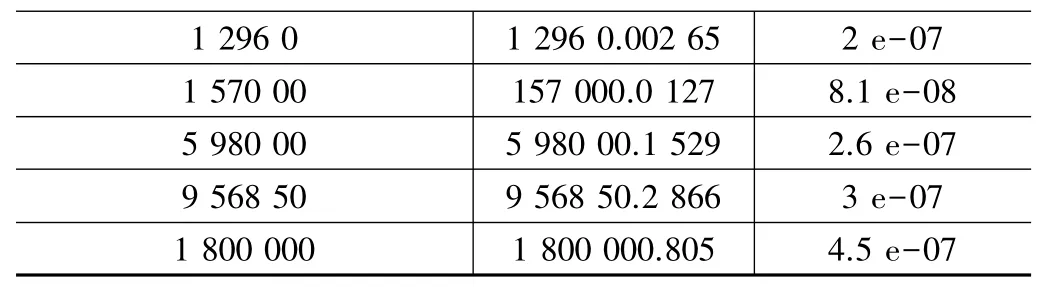

为了测试本文设计的频率计精度,使用频率计对安捷伦33521A信号发生器发出的不同频率的方波信号进行测量,测量结果如表2所示。通过测量结果可以看出:本文设计的自调整频率计精度在全量程范围内达到精度要求,采用该频率计测量1 Hz~2 MHz方波信号的频率的相对误差的数量级可以达到10-7。

表2 方波信号测试结果

__________1 296 0 1 296 0.002 65 2 e-07_________1 570 00 157 000.0 127 8.1 e-08_________5 980 00 5 980 00.1 529 2.6 e-07_________9 568 50 9 568 50.2 866 3 e-07_________1 800 000 1 800 000.805 4.5 e-07

4.2 测量谐振式加速度传感器的输出信号

将设计的频率计应用到实验室研制的谐振式加速度传感器测试过程中。该加速度传感器设计用来检测面内加速度。由谐振梁、蟹腿型支撑梁、质量块、激励电阻、惠斯登电桥和金属引线组成。在X方向加速度作用下,质量块在X方向运动。X方向的其中一个谐振梁所受的轴向应力发生改变,谐振频率发生变化,该谐振频率变化的差值反映了X方向加速度的大小和方向;同样地,在Y方向加速度作用下,质量块在Y方向运动,Y方向的谐振梁之一轴向应力发生改变,谐振频率变化。该谐振梁谐振频率变化的差值反映Y方向加速度的大小和方向。

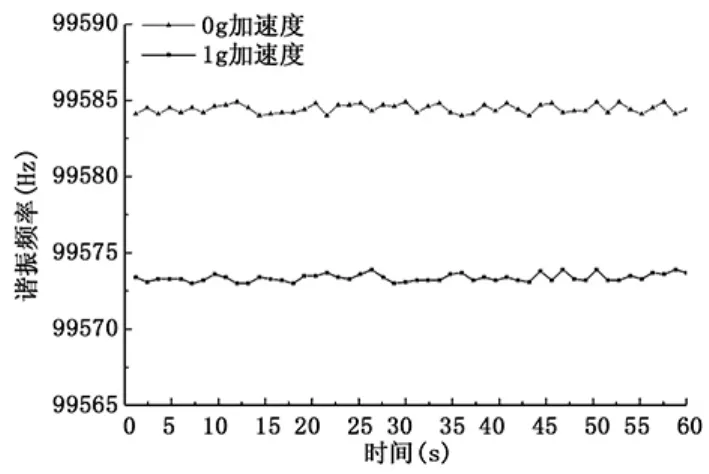

由于重力加速度精确度高,同时很容易获得,便于应用到实验中。因此实验室采用重力场翻滚试验来对制作出的加速度计样片进行测试[10]。实验使用装置为精密型手动角度旋转台。测试时,将加速度计样片置于角度旋转工作台上,使用闭环自激电路让测试的谐振梁处于闭环自激状态,通过旋转精密型角度旋转台来调节被测谐振梁与重力加速度之间的夹角,从而来给样片提供不同大小的加速度。谐振梁的谐振频率随着不同的加速度变化而变化,以此来测试该加速度计样片的性能。在0 g和1 g X方向加速度下,使用安捷伦六位半万用表34401采集1分钟X方向谐振梁的输出谐振频率如图6所示,本文设计的频率计采集1分钟X方向谐振梁的输出谐振频率如图7所示。

图6 安捷伦万用表采集的输出频率

图7 本文设计的频率计采集的输出频率

分析两组数据可以得到:对于使用安捷伦六位半万用表采集的数据,当加速度计受到1 g加速度时,谐振频率的平均值下降约为11.07 Hz。对于本文设计的频率采集的数据,当加速度计受到1 g加速度时,谐振频率的平均值下降约为11.12 Hz。比较两者发现:与安捷伦万用表相比,本文设计的频率计在1分钟内采样数据个数约是安捷伦万用表采样数据个数的10倍,更加全面的反映出不同时间谐振梁的振动状态。两者在1分钟内采集的谐振频率的平均值存在一定的误差,这是因为本文设计的频率计采集的点更加全面。同时,该频率计具有体积小,成本低等不可忽视的优势,拥有广阔的市场前景。后续工作可以围绕进一步提高采集速度、减噪进行,从而提高系统稳定性。

5 结束语

该频率计是基于FPGA设计的,使用quartus编译后,写入到FPGA芯片中。通过对信号发生器产生的标准频率信号进行测量,结果证明,采用该频率计测量1 Hz~2 MHz标准信号的频率的相对误差数量级可以达到10-7,达到设计要求。将其应用到硅微谐振式加速度传感器的性能测试中,测得谐振式加速度传感器在闭环时输出频率的变化稳定在1 Hz以内,同时测试了加速度计的灵敏度为11.12 Hz/g。由于FPGA体积小,结构简单、灵活性高、可编程,造价较低,因此被广泛应用在数据采集等方面。本文设计的频率计其测量精度与响应时间成正比,在一些测量精度要求不高的工作中可适当降低精度提高测量的响应速度。