基于SoC技术的嵌入式软件无线电平台设计

2018-09-13李元帅

李元帅

摘要:文章以双核SoC、低功耗FPGA芯片和自适应射频处理前端为核心,构建并实现了一种新型的软件无线电信号处理硬件平台,设计了SCA架构的软件,满足便携式宽频带无线通信设备对低功耗、高性能、多通信波形加载的应用需求。

关键词:软件无线电;SoC; SCA

随着大规模集成电路技术的不断进步,软件无线电作为一种接近理想化的通信技术越来越成熟。软件无线电的核心是把硬件作为无线通信的基本平台,把尽可能多的无线通信功能用软件实现[1],其决定性的部分在于通用高速数字信号处理能力和中频信号的高速A/D,D/A变换,这之后整个处理都可用通用可编程数字器件特别是软件来实现。针对便携设备的嵌入式软件无线电信号处理平台主要受到功耗、体积和成本的制约,因此,结合近期集成电路技术的发展,利用新的处理器开发新的平台以降低功耗、减少体积是软件无线电便携设备的必经之路。本文结合TI公司的低功耗多核双核系统级芯片(System of Chip,SoC)OMAP138和xilinx公司的低功耗现场可编程门阵列(Field Programmable GateArray,FPGA)芯片,设计了满足宽频段便携无线通信设备需求的信号处理平台及软件架构。

1 软件无线电信号处理平台方案设计

传统的宽频段软件无线电平台为了满足信号处理能力和多波形软件加载能力,一般需要独立的CPU芯片、FPGA芯片、DSP芯片和AD/DA中频前端处理电路来实现,造成在体积、功耗、成本等方面一直较高,在便携设备上一般难以适用。随着半导体工艺的发展,多核集成芯片已经相当成熟,便携设备的软件无线电设备成为可能。

按照设计需求,无线便携设备需要支持80?500 MHz的频段,在射频前端混频到56 MHz的中频信号后,由本平台完成中频采样和信号处理工作。工作带宽支持窄带通信200 kHz带宽以及宽带通信20 MHz带宽的自动切换,支持多种通信波形的动态加载,因此,需要考虑信号处理能力与功耗之间的平衡以及AD/DA的高速采样能力。该设计以低功耗SoC芯片OMAPL138为核心,以低功耗FPGA芯片XC7A100T为上下变频协处理器,构建低功耗硬件平台。整体设计如图1所示,接收通路中,中频信号经过中频调理滤波处理后模數转换采样,经FPGA的数字下变频到基带信号,送到OMAP L138的DSP处理核心进行解调解码,然后送到ARM内核进行协议解析,识别语音或数据后送到语音处理电路或送到数据显示终端。

发射流程与接收流程反向,信息经数字信号处理后转模拟中频输出。

2 信号处理平台的硬件系统设计

2.1 控制及信号处理部分设计

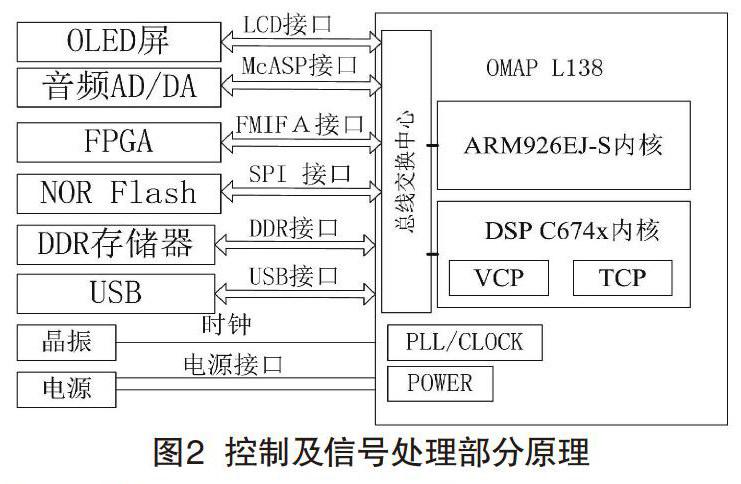

控制及信号处理部分以双核嵌入式处理器OMAP L138为核心,设计了OMAP L138的周边系统,包括Flash存储、双倍内存(Double Data Rate,DDR)内存、以太网接口以及调试串口等,OMAP L138的硬件系统设计如图2所示。

2.1.1 核心处理器OMAP L138的应用

核心处理器采用TI的达芬奇(Davinci)架构的双核嵌入式处理器OMAP L138。OMAP L138是理想的便携式、低功耗和高性能适用于通信算法的多核SoC集成了ARM内核的微处理器和适用于通信算法处理的DSP内核及通信算法中常用的维特比译码(Viterbi Decoder Coprocessor,VCP)和Turbo译码协处理器(Turbo Decoder Coprocessor,TCP),最大功耗只有840 MW,通过对定时不用的功能的冻结,可以进一步降低运行功耗,提升便携设备的运行时间。

其中的ARM内核兼容ARM926ET-S系列,其时钟频率最高500 MHz,主要用于进行设备的集中控制处理,完成分组网络协议处理,数据话音业务的处理功能以及LCD屏的显示控制等。

内嵌的DSP内核兼容TI的DSP C674x系列的高性能浮点DSP,采用C674TM内核,其中的VCP和VCP能够大大提升无线通信算法的执行效率,简化程序设计。DSP内核主要完成基带信号进行信号调制解调、信道编解码、信号检测估计、收发同步抗干扰处理等复杂算法功能。

OMAP L138通过内部的交换中心实现外部接口与ARM内核和DSP内核之间以及ARM与DSP两个内核之间的交互。

本设计通过GMII接口实现以太网接口,通过DDR接口扩展1 GB的运行内存,通过SPI接口扩展512 MB的Flash存储器,满足多波形算法存储空间需求;通过多通道音频串口(Multichannel Audio Serial Port,McASP)实现语音AD/DA的通道,利用LCD接口外挂OLED显示屏,与FPGA的接口则利用外部存储接口来实现。

2.1.2 OMAP L138最小系统设计

OMAP L138的最小系统包括外围的电源、时钟、DDR内存、Flash存储器等。

电源控制是低功耗设计的重要组成部分,本设计通过高集成电源稳压芯片TPS65070实现OMAP 138以及外围电路的电源供给和控制。TPS65070具有3路DC-DC转换器、2个低压差线性稳压器(Low Dropout Regulator,LDO);具备IIC电源管理接口和充电管理接口,在电源通路的管理下可以为移动设备的锂电池进行充电。3个高效的降压转换器可以提供核心电压、内存及10口的电压;在轻载的时候可通过调整PWM频率使得降压转换器进入低功耗模式;如果对低噪要求较高,可以通过IIC接口对芯片编程使芯片强制工作在定频PWM模式下。此芯片还提供了 2路通用LDO电源,可以提供200 mA的输出电流。LDO口的输入电压可以由DC/DC电源或电池提供,LDO具有相对DC/DC电源更低的电源噪声,用于音频处理等对噪声敏感的电路供电。

时钟部分采用外部贴片晶振提供24 MHz的源时钟,通过内部DLL倍频后作为ARM内核和DSP内核的运行时钟以及作为DDR接口时钟。

DDR芯片选用Micron公司的MT46H64M16-6L-IT,具备DDR接口和SDRAM接口,可作为先进先出(First Input FirstOutput,FIFO)应用。FPGA可以通过SDRAM存储器控制器访问控制访问存储空间;OMAP L138通过DDR2接口控制器来访问控制存储空间,从而实现二者之间的快速数据交互,满足多路通信数据交互需求,减少FPGA内部存储器资源的消耗。

Flash程序存储器采用ST的低功耗小体积SPI接口的非遗失存储器M25P128,封装兼容容量256 MB?1 GB的同系列存储器,方便扩展和更新迭代。

2.2 中频前端设计

中频前端处理包括中频收通路处理和中频发通路处理。中频收通路处理主要作用是对射频前端一次变频处理后的中频信号进行模拟滤波处理、低噪声放大、AD采样后,由FPGA进行数字滤波和二次变频,转化成数字基带信号,送到控制及信号处理系统进行解调和协议解析。中频发通路

正好相反,把数字基带信号在FPGA内上变频到中频信号,然后送DA芯片进行模拟化后通过放大滤波送给射频前端进一步变频处理成射频信号。

中频收发通路采用多通道声表滤波器在200 kHz窄带和20 MHz宽带可切换模式,满足宽窄带无线同通道的不同业务需求。声表滤波器相较于传统的LC滤波器,具有体积小、重量轻、传输损耗小、阻抗误差小等优点,能实现电子器件的超小型化设计,灵活性高,同时具有很好的一致性、极高的温度稳定性,动态范围也很大,频率选择性优良。利用声表滤波器这些优良特性实现对收发信号的带外噪声抑制,提高中频接收的灵敏度和发射信号的带外辐射。

FPGA采用XC7A100T完成收发通路的数字上下变频。XC7A100T针对低功耗应用进行优化,与Spartan-6系列性相比,性能提高30%,成本降低35%,功耗降低50%,占用面积缩减50%,能满足便携软件无线电通信设备对大小、重量、功耗和成本的要求。

3 软件设计

软件无线电的设计思想需要在硬件平台资源能够支撑算法需求的同时,软件架构也要能够对多种无线通信算法的灵活支持,必然需要标准化的开发架构,方便的软件接口。因此,软件设计上采用服务组件框架(Service Component Architecture,SCA)架构进行设计。设计分层如图3所示。

操作系统选择高实时性的VxWorks,驱动软件主要包括外部的LCD接口、USB接口以及内部的DDR接口、SPI接口、McASP 接口等。

第二层的硬件抽象层的主要功能是封装底层驱动、屏蔽操作系统,为上层提供统一接口并实现数据传输,根据不同的计算单元可分为通用目标处理器(General Purpose Processor,GPP)通用微处理器硬件抽象层和FPGA硬件抽象层。

3.1 GPP内核硬件抽象层

GPP硬件抽象层通常指能够在支持SCA定义的中间件的计算单元中运行的硬件抽象层[2],这里主要指的是OMAPL138中ARM处理器的硬件抽象层。它由设备模块、端口模块、映射模块和驱动适配模块组成,软件框架如图4所示。

3.1.1设备模块

GPP硬件抽象层实现了核心框架的设备接口,由核心框架统一管理。设备模块主要功能就是提供GPP硬件抽象层被SCA核心框架管理时所需的方法和接口,以及中间件初始化、注册、服务等功能。

3.1.2 端口模块

端口模块主要实现标准所规定的接口,是GPP硬件抽象层核心功能的实现部分[3]。它为上层组件提供了读取数据、写入数据、配置映射等功能方法。

该模块与映射模块以及驱动适配模块相关联,其先访问映射模块获取相应的地址映射信息、信号量信息和标志信息,然后据此调用驱动模块完成具体的数据收发功能。

3.1.3 映射模块

映射模块提供与组件读写操作相关的映射信息的增、删、改、查等功能。该模块设计了地址映射表、信号量映射表和标志映射表等,用于存储硬件抽象层所需的所有映射信息。

3.1.4 驱动适配模块

驱动适配模块是GPP硬件抽象层与底层驱动接口的交互部分,其主要功能是对GPP硬件抽象层所需的底层驱动进行封装。

3.2 FPGA硬件抽象层

FPGA硬件抽象层的主要功能是封装底层驱动,提供统一接口供算法波形组件使用,提高算法波形组件的可移植性。它由驱动适配模块、接收管理模块、发送管理模块、接收端口和发送端口组成,软件框架如图5所示。

3.2.1 驱动适配模块

驱动适配模块用于封装驱动接口,使FPGA抽象层适配不同的底层传输方式。它接收底层驱动信号并将其转换成硬件抽象层收发信号。

3.2.2 接收管理模块

接收管理模块是将由驱动适配模块适配后的接收信号作进一步解析,转换成接收总线供接收端口使用。

3.2.3 发送管理模块

发送管理模块用于分发FPGA硬件抽象層的发送数据,其主要功能是:根据发送机制响应发送请求将算法组件的数据通过底层驱动发送到GPP侧。

3.2.4 接收端口

接收端口的主要功能是存储已接收到的数据并将其转发到算法波形组件中。首先,根据硬件抽象层运行时钟将接收到的数据写入到FIFO中,然后给波形组件接收信号,最后根据波形组件运行时钟从FIFO中读出数据并传送到波形组件中。

3.2.5发送端口

发送端口的主要功能是存储波形组件的待发送数据并由发送管理模块分发发送数据。

应用服务层主要包括通信控制软件、通信算法软件和人机接口服务。通信控制软件和通信算法软件作为组件通过调用硬件抽象层实现与底层硬件的完全隔离,保持算法软件、控制软件和服务软件的独立性。人机接口服务软件由初始化模块、按键控制模块和菜单显示模块组成。

整个软件按照小型化SCA架构剪裁简化,以方便波形组件开发和加载,同时满足便携设备的资源要求。

4 结语

结合新的SoC技术,实现了便携式无线通信设备中频信号处理平台设计和软件架构设计,具备了软件无线电性能和SCA标准的软件灵活性。本设计在某型便携设备中得到实际应用,相较于前一代设备在运算性能上提升一倍,功耗却降低了 1/3,同时实现了3种算法波形的快速切换和加载,有效提升了设备性能。

[参考文献]

[1]杨小牛.软件无线电原理与应用[M].北京:电子工业出版社,2014.

[2]周新.SCA在通信系统中的应用研究[D].成都:电子科技大学,2014.

[3]赵秋明.基于SCA的小型化核心框架研究[J].计算机测量与控制,2010(5):1145-1147.