基于FPGA的微型SAR成像信号处理技术

2018-05-24,,,

, , ,

(南京航空航天大学电子信息工程学院, 江苏南京 211106)

0 引言

合成孔径雷达(Synthetic Aperture Radar, SAR)能够实现全天候、全天时和高分辨率对地成像,在军事侦察、环境监测、应急救援等领域均具有广泛应用,始终是雷达技术领域的研究热点。微型SAR(MiniSAR)成像系统因其体积小、重量轻、功耗低等优势,已成为SAR技术发展的重要方向。

我国MiniSAR系统的研制在2010年左右才开始进行,起步时间相对较晚,但进展迅速,目前已经完成了多个MiniSAR系统的研制工作[1-3]。这些处理系统主要在DSP基础上进行搭建,虽然目前DSP采用了多重流水线的方式提高运算速度,但是DSP在本质上还是一种串行数字信号处理器,其处理速度受限于时钟频率、流水线级数等因素。FPGA内部集成的寄存器(Register)、查找表(LUT)、存储单元(BRAM)、运算单元(DSP)、缓存(Buffer)和时钟单元(PLL/MMCM)等硬件资源可显著提升其运算能力。FPGA为进一步提高处理速度,采用逻辑门的电路结构,且线路延迟小,高工艺的发展使得成本与功耗更低的同时,性能大幅提升。FPGA完全不同于DSP的固有硬件结构[4],使其成为实现大数据量、高速雷达信号处理的理想选择。

2004年,Sandia实验室针对去斜率(Dechirp)信号接收系统,利用FPGA实现了基于极坐标格式算法(PFA)的聚束MiniSAR成像系统,成像场景大小为2 048 ×2 048个采样点,采用较高精度、高性能的惯导系统进行运动补偿,但综合成本较高且成像场景较小。文献[5]同样采用PFA算法,提出了一种联合FPGA和DSP实现8位数据的机载SAR成像处理方案,距离向和方位向重采样均通过7点插值实现,而且主要由DSP完成运动误差估计、补偿以及数据转置存储部分,因此处理数据精度和速度均可进一步提高。文献[6]研究了基于SPECAN算法的斜视机载SAR成像处理方法,采用Sinc插值进一步校正图像畸变,给出了机载SAR的实测数据处理结果,但是并未给出MiniSAR成像结果的验证。文献[7]以8核DSP及FPGA为核心,设计了一种MiniSAR成像处理体系架构,利用FPGA完成底层数据流控制,顶层算法处理由DSP完成,处理速度有限,不能满足较大数据量时的处理要求。本文中实现的MiniSAR成像系统完全基于FPGA实现高分辨率成像处理,该系统在PFA基础上进行了改进,针对聚束模式下的去斜率信号,分别应用尺度变换原理(PCS)和Sinc插值算法实现对距离向和方位向的数据域重采样,再由相位梯度自聚焦(PGA)实现任意阶相位误差的估计和补偿,具有处理控制流程简洁、成像精度高和处理速度快等优势。

1 成像信号处理算法

聚束SAR成像的几何模型[8-9],如图1所示,以场景中心O为坐标原点,航迹近似平行于轴Ox,Rc为航迹到场景中心的最短距离。载体平台速度v,天线相位中心(Antenna Phase Center, APC)的瞬时方位角、俯仰角分别为θ和φ,场景中点目标坐标为(xp,yp,0)。

雷达发射线性调频信号(Linear Frequency Modulation, LFM)形式为

(1)

式中,τ为快时间,Tr为雷达脉冲宽度,k为调频斜率。对点目标回波信号进行去斜率处理后为

(2)

式中,c为光速,t为方位慢时间,fc为载波频率,Rt为天线相位中心到目标的瞬时距离值,对于条带模式参考距离Rref=Rc,RΔ=Rt-Rc。

由于本系统的雷达回波数据是按照条带模式采集的,转为聚束模式进行处理时,参考距离不是固定的Rc,而是雷达APC与坐标轴原点O的距离Ra,随着飞机的位置而变化,此时RΔ=Rt-Ra。首先用参考距离对距离向每一脉冲进行补偿,等同于乘以一个参考相位:

(3)

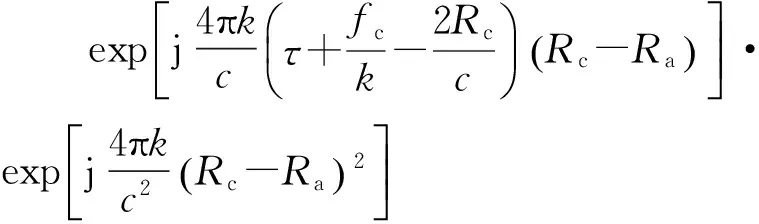

接下来对参考距离补偿后数据分别进行距离向、方位向处理。利用PCS对回波信号距离向进行处理,首先对距离补偿后数据乘以二次相位 函数:

(4)

式中,δr为距离向尺度变换因子:

(5)

对所得数据进行FFT操作,再乘以匹配滤波函数:

(6)

式中,fτ表示距离向采样频率。对得到的数据作IFFT运算,最后再对得到的数据作乘以二次相位函数:

(7)

距离向处理后,方位向采用Keystone变换进行重采样,等同于作如下变换:

(8)

目前常用的插值算法有线性插值、多项式插值、三次样条插值和Sinc插值等。线性插值简单方便,但其精度较低,成像效果不理想;多项式插值和样条插值结构涉及除法和循环迭代,实现结构复杂,利用FPGA实现时程序复杂度较高;Sinc插值的点目标聚焦效果较好,而且Sinc插值本身结构基于卷积架构,核心为乘和累加,适合FPGA实现。综合考虑资源、精度和算法复杂度,本系统选用Sinc插值进行PFA成像。Sinc插值公式为

(9)

式中,gd(i)为已知采样信号,sinc为卷积核。

由于MiniSAR飞行平台非理想运动和易受气流扰动等因素使得回波误差不可避免,导致图像发生散焦。一般而言,先利用惯导系统记录的数据进行运动补偿,当惯导精度无法满足要求时,必须从回波数据中提取并补偿相位误差,即自聚焦处理,本系统采用相位梯度自聚焦算法[10-11]。

2 硬件实现方案

该系统架构如图2所示,处理系统包括3个核心子模块:数据传输子模块,通过以太网实现FPGA板与上位机的数据传输;算法处理子模块,对数据进行两维压缩成像处理;DDR3 SDRAM读写子模块,实现两维数据的转置以及连续地址的高速读写。

2.1 数据传输模块

本系统采用以太网实现主机与板卡之间通信,在网络层和传输层的协议控制上选择UDP/IP协议来实现[12]。FPGA实现UDP/IP设计相对简单,资源利用较少。在开始处理数据之前,上位机负责把基本雷达参数以及回波数据通过以太网传送到FPGA处理模块内,将回波数据写入DDR3 SDRAM中。等待处理结束后再将成像结果发送回上位机显示。

2.2 算法处理模块

图3为算法具体实现流程图,整个算法模块由参数计算模块、距离向PCS模块、FFT模块、方位向插值模块以及PGA模块组成。

具体实现方式由图3可以看出,首先将雷达回波数据写入到DDR内存中,同时传入雷达信号的基本参数到参数计算模块。采用64位高精度浮点计算分别得到距离向、方位向以及自聚焦处理所需的具体参数,然后对回波信号进行距离向PCS处理并转置写入DDR。参考距离补偿也是针对每一个脉冲进行,因此可与距离向重采样同时进行处理,操作简化且节省反复读写DDR的时间,从而提高系统处理速度。然后实现方位向处理,转置读取每一个距离门的回波数据进行Sinc插值实现重采样。最后通过自聚焦模块得到MiniSAR聚焦后的图像。

图4为距离向实现的具体模块图,处理过程中需要两次FFT(或IFFT)操作,虽然同时例化若干FFT 的IP核能简化代码设计,但是极大地占用FPGA片上资源。而本系统中FFT模块和IFFT模块采用时分复用同一个FFT模块的方式,只需要例化一个FFT的IP核,可以保证运算速度的同时大大减少FPGA板内资源消耗。

方位向插值模块实现框图如图5所示,主要有两个子模块:待插值点判断模块和Sinc卷积模块。插值过程先根据待插点坐标寻找出相邻8个点的坐标位置,将坐标系数与输入的雷达回波数据对应相乘得到插值结果。针对处于样本边界外或不存在相邻8个点的待插值点,本设计中采用标识信号进行判断,使特殊点和正常点处理一体化,从而模块设计更简单、稳定。

图6为PGA模块流程图,遍历输入散焦图像的每一个距离门,首先对数据取模选出部分能量最大的距离单元,计算选出的每一个距离门的相位梯度;再根据当前迭代次数设置窗宽,实现加窗操作,对相位误差梯度进行累加得到相位误差;最后实现对成像结果更高精度的相位补偿,得到MiniSAR聚焦良好的结果。

2.3 DDR3读写转置模块

DDR3模块主要用来存储雷达回波数据以及算法处理中间结果[13-14],内置的读写控制模块可实现数据处理时所需的连续、转置读写操作,单通道内存有4 GB,开启双通道后可实现8 GB存储,满足实时处理的大数据量需求。

本系统只利用一片DDR3内存条,矩阵转置采用直接式分段存储方法。将距离向脉冲分段存储,一段数据按线性地址存放在DDR3中,然后跳变存入下一段。具体存储过程如图7所示。此方式是一种读写速率平衡的转置方式,其本质是在SDRAM的同一行中存放相同分量的列数据和行数据,在略微增加写操作换行次数的同时大大减少读操作换行次数,从而提高转置效率。

3 实验结果分析

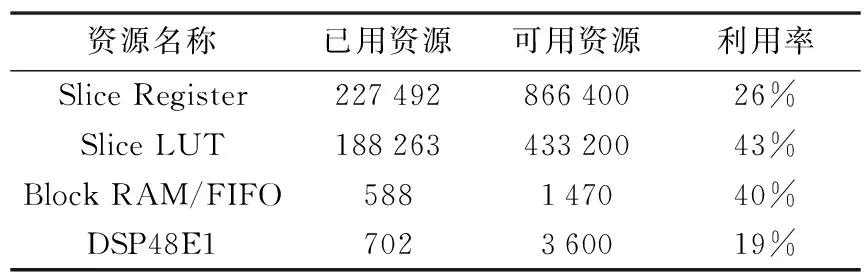

本成像系统在Xilinx公司的开发平台上进行算法验证。该板集成了一片Virtex7-XC7VX6907 的FPGA颗粒、8 GB的DDR3、三态以太网PHY和100 MHz的差分时钟。应用文中提出的系统设计对实测数据进行参考距离补偿、距离向PCS、方位向Sinc插值和PGA处理,最后通过上位机显示成像结果。表1给出了实际成像大小为距离向 8 192个采样点、方位向4 096个采样点时的资源利用情况。

表1 资源利用情况

片内DSP48E1资源用来提高复乘、复加和FFT等计算模块的处理速度。Block RAM中包括BRAM18E1,BRAM36E1,前者作为存储资源的使用量远远低于后者,主要用于对大数据量处理的缓存FIFO拓展性的增强。LUT作为核心资源,利用率较高,主要负责FPGA处理流程控制。

本成像处理系统主要用于去斜率信号的MiniSAR系统,表2给出了实测数据的主要雷达参数。

当系统工作频率为200 MHz,处理8 192× 4 096个采样点的32位单精度浮点数据时,系统处理时间为5.10 s,且成像效率高,可满足实时成像的要求。图8为MiniSAR实测数据的有效目标场景截取结果,地点为南京方山,图9为同一场景的Google光学图像。从结果可以看出,本系统能够清晰地展现地物信息。图10(a)和图 10(b)分别为成像结果局部放大图,显然场景细节丰富,地物轮廓分明,对比度和信噪比较高,聚焦和成像效果优良。

表2 MiniSAR系统实测数据主要雷达参数

4 结束语

本系统实现了基于FPGA的8 192×4 096个采样点的微型SAR成像并行信号处理,并通过Xilinx公司的Virtex7-XC7VX6907 FPGA芯片进行了验证。本文首先介绍改进后的PFA成像算法的具体实现,然后详细陈述硬件实现模块的设计过程,并对硬件资源利用率进行分析。本系统具有自动补偿雷达平台运动误差的能力,显著改善了MiniSAR在平台大机动条件下的成像效果。实测数据处理结果表明系统稳定可靠,处理时间和成像精度均能满足实时和高分辨率的要求。

参考文献:

[1] 高许岗, 雍延梅. 无人机载微型SAR系统设计与实现[J]. 雷达科学与技术, 2014, 12(1):35-38.

GAO Xugang, YONG Yanmei. Design and Realization of UAV High Resolution Miniature SAR[J]. Radar Science and Technology, 2014, 12(1):35-38.(in Chinese)

[2] WANG Hui, JIANG Man, ZHENG Shichao. Airborne Ka FMCW MiSAR System and Real Data Processing[C]∥ 17th International Radar Symposium, Krakow: IEEE, 2016:1-5.

[3] 李俊慧, 王洪, 汪学刚, 等. 步进频、脉冲和连续波SAR的对比研究[J]. 雷达科学与技术, 2016, 14(1): 45-53.

[5] 周芳, 唐禹, 张佳佳, 等. 机载高分辨聚束式SAR实时成像处理系统的FPGA实现[J]. 电子与信息学报, 2011, 33(5):1248-1252.

[6] 李学仕, 梁毅, 李蓓蕾, 等. 基于SPECAN处理的斜视SAR实时成像算法及其FPGA实现[J]. 系统工程与电子技术, 2011, 33(12):2618-2622.

[7] 洪峰, 韩荣桂, 胡骁, 等. 一种高效的微型SAR实时成像系统架构设计[J]. 系统工程与电子技术, 2014, 36(4):672-678.

[8] ZHU Daiyin, YE Shaohua, ZHU Zhaoda. Polar Format Algorithm Using Chirp Scaling for Spotlight SAR Image Formation[J]. IEEE Trans on Aerospace and Electronic Systems, 2008, 44(4):1433-1448.

[9] 曾乐天, 梁毅, 邢孟道. 一种基于极坐标格式算法的高分辨SAR成像自聚焦算法[J]. 电子与信息学报, 2015, 37(6):1409-1415.

[10] ZENG Letian, LIANG Yi, XING Mengdao, etc. A Novel Motion Compensation Approach for Airborne Spotlight SAR of High-Resolution and High-Squint

Mode[J]. IEEE Geoscience and Remote Sensing Letters, 2016, 13(3):429-433.

[11] 郭江哲, 朱岱寅, 毛新华. 一种SAR两维自聚焦算法的FPGA实现[J]. 雷达学报, 2016, 5(4):444-452.

[12] ZHU Daiyin, ZHANG Jindong, MAO Xinhua, et al. A Miniaturized High Resolution SAR Processor Using FPGA[C]∥ 11th European Conference on Synthetic Aperture Radar, Hamburg: VDE, 2016:343-346.

[13] TIAN Haishan, CHANG Wenge, LI Xiangyang. Integrated System of Mini-SAR Real-Time Signal Processing and Data Storage[C]∥ IEEE Radar Conference, Johannesburg: IEEE, 2015:354-358.

[14] 杨宇宸, 向海生. 一种高速数据采集系统的设计与实现[J]. 雷达科学与技术, 2016, 14(5):526-530.

YANG Yuchen, XIANG Haisheng. Design and Implementation of High Speed Data Acquisition System[J]. Radar Science and Technology, 2016, 14(5):526-530.(in Chinese)