Ka波段低相噪锁相倍频源设计

2018-05-11庞春辉王绍东

庞春辉,王绍东

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引言

从20世纪50年代开始,空间技术的发展极大地推动了频率源技术的发展,我国在此时也开始了对相关技术的研究和应用工作[1]。迄今为止,频率源技术已广泛应用到航天及通信等领域,对其提出了更高的要求。捷变频、小步进、高频率和低相噪等指标越来越受到工程的青睐。但是上述各个指标会互相制约[2],如何选择合适的频率合成方案使其整体性能达到最优成为工程设计的难题[3]。为了解决这一难题,已有技术人员提出了采用DDS和PLL相结合的技术实现高性能频率源[3]。本文提出了结合直接频率合成和间接频率合成优点对频率源进行设计的思路,实现Ka波段频率输出,具有低相噪、快速跳频和高杂散抑制的特点。

1 频率源实现原理

频率源的实现主要有直接频率合成、直接数字(DDS)频率合成、间接(锁相)频率合成3种方式。直接频率合成频率源的优点是频率跳变速度快、相位噪声低;其缺点是体积较大、杂散成本高。直接数字频率合成频率源的优点是频率跳变速度快、频率分辨力高;缺点是输出频率不高、杂散高。间接频率合成频率源的优点是输出频率范围宽、杂散低和电路简单;缺点是频率跳变速度慢[4]。

由以上分析可得,如果用单一方式设计频率源,跳频时间和频率步进相互制约,同时也较难实现低相位噪声和高频率输出。从电路简单、小体积考虑,锁相是最好的实现方式,但是输出频率要达到Ka波段,直接锁相输出没有合适的压控振荡器,且无法满足快速跳频要求,所以本次设计采用直接频率合成和锁相频率合成相组合的方法,综合二者的优点,实现了低相位噪声、快速跳频和小步进的技术指标。

频率源要实现输出频率为30~31 GHz,倍频前的频率需为15~15.5 GHz。如果此频率用一个单环实现,无法实现低相位噪声和快速跳频,所以用一个大步进锁相源和一个小步进锁相源混频得到15~15.5 GHz信号。

用2个信号相加方式得到倍频所需的基频信号,相加信号频率的选择非常关键,需要考虑混频杂波抑制、相位噪声和跳频步进等因素。经综合考虑,选择小步进锁相源输出信号频率为1~1.1 GHz,步进为10 MHz;大步进锁相源输出频率为14~14.4 GHz,步进为100 MHz。2个信号混频后得到跳频步进为10 MHz的15~15.5 GHz信号,倍频后最终得到跳频步进为20 MHz,频率为30~31 GHz的信号。

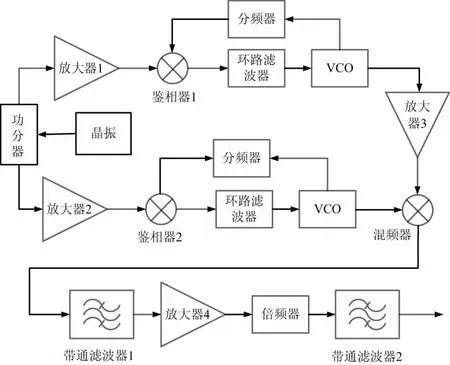

频率源实现原理如图1所示。

图1 频率源实现原理

2 频率源电路设计

整个频率源系统指标实现的关键在于锁相电路设计和电磁兼容设计。

2.1 锁相电路设计

锁相电路在环路带宽内,系统输出的相位噪声主要取决于参考信号和数字鉴相器基底噪声,在环路带宽外,相位噪声则主要由VCO决定[5],所以环路器件的选取非常重要。

参考信号选用国产定制低相噪晶振,相位噪声为-160 dBc/Hz@1 kHz。

小步进锁相源鉴相器选用AD公司的ADF4106[6],该鉴相器有6 GHz带宽,独立的电荷泵(VP)可在3 V系统中提供扩展的调谐电压。大步进锁相源鉴相器选用AD公司的HMC704LP4E[7],该鉴相器是一款低相噪锁相环芯片,其最高工作频率可达8 GHz,具有整数模式和小数模式,噪声基底在整数模式下为-233 dBc/Hz,最高参考输入频率高达350 MHz,在整数模式下鉴相频率最高位115 MHz。

小步进锁相源和大步进锁相源均选用国产定制VCO,小步进锁相源VCO相位噪声为-119 dBc/Hz@100 kHz,大步进锁相源VCO相位噪声为-112 dBc/Hz@100 kHz。

对环路内相位噪声进行推导[6],

PNSYNTH=PNTOT+10lgFPFD+20lgN,

(1)

式中,PNSYNTH为环路内相位噪声;PNTOT为鉴相器归一化相位噪声;FPFD为鉴相频率;N为分频比。

小步进锁相源输出信号最高频率为1.1 GHz,鉴相频率为10 MHz,分频比为110,鉴相器ADF4106噪声基底为-219 dBc/Hz,由式(1)可得小步进锁相源环路带宽内相位噪声理论值为:

PN(1.1 GHz)= -219+10lg107+20lg110=

-108.2 dBc/Hz。

大步进锁相源输出信号最高频率为14.4 GHz,鉴相频率为100 MHz,分频比为144,鉴相器HMC704LP4E噪声基底为-233 dBc/Hz,由式(1)可得大步进锁相源环路带宽内相位噪声理论值为:

PN(14.4 GHz)= -233+10lg108+20lg144=

-109.8 dBc/Hz。

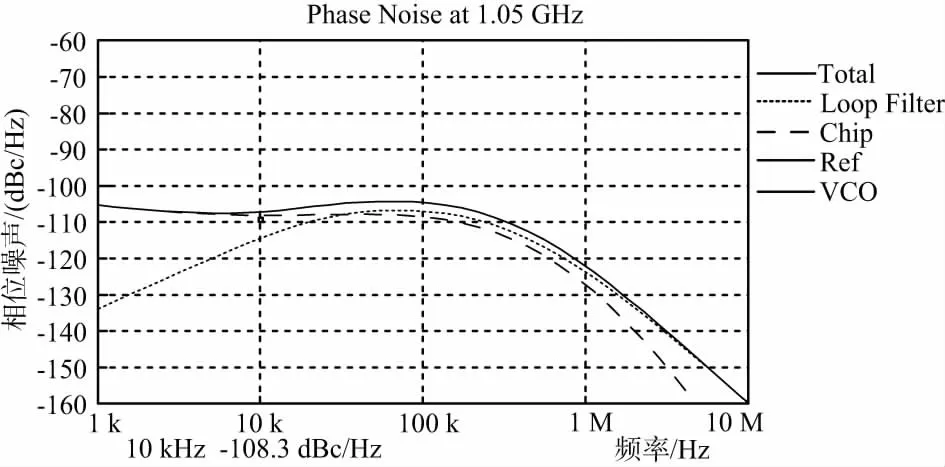

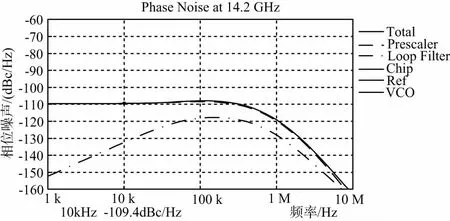

利用软件对锁相环路进行仿真,得到小步进锁相源环路滤波器电路如图2所示,相位噪声仿真结果如图3所示,结果为-108.3 dBc/Hz@10 kHz;得到大步进锁相源环路滤波器电路如图4所示,相位噪声仿真结果如图5所示,结果为-109.4 dBc/Hz@10 kHz。二者的相位噪声理论计算结果和仿真结果相近。系统最终输出信号相位噪声取决于最差信号,倍频后相噪恶化理论计算为6 dB,实际会更高,最终信号相位噪声预计为-100 dBc/Hz@10 kHz左右。

图2 小步进锁相源环路滤波器电路图

图3 小步进锁相源相位噪声仿真结果

图4 大步进锁相源环路滤波器电路

图5 大步进锁相源相位噪声仿真结果

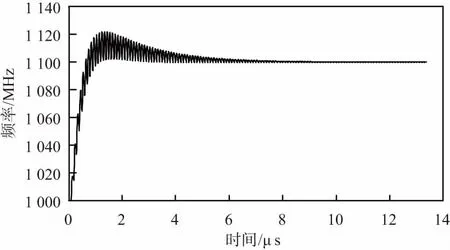

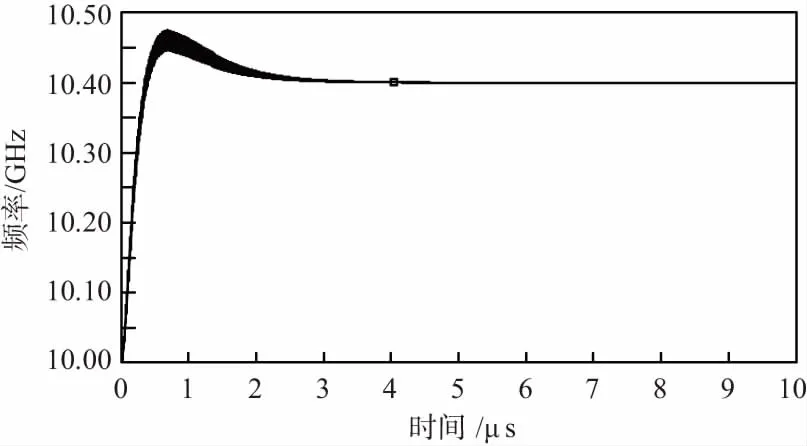

环路的锁定时间取决于跳变频率间隔和环路宽度[8],一般跳频频率间隔由系统决定,在兼顾鉴相泄露指标情况下,尽量设计较大的环路带宽。锁定时间的理论计算较为繁琐,一般利用软件进行仿真。由图6可得小步进锁相源锁定时间仿真结果为10 μs左右,加上单片机10 μs发数时间,总跳频时间为20 μs。由图7可得大步进锁相源锁定时间仿真结果为4 μs左右,加上单片机10 μs发数时间,总跳频时间为14 μs。系统总跳频时间由最慢的环路决定,所以系统总跳频时间分析结果约为20 μs。

图6 小步进锁相源锁定时间仿真结果

图7 大步进锁相源锁定时间仿真结果

2.2 电磁兼容设计

在频率源设计过程中,电磁兼容设计举足轻重,特别是在频率源性能指标要求十分高的情况下,电磁兼容设计的好坏,往往是设计成败的关键因素[9]。

射频电路为分布参数电路,当电路工作时,会受到趋肤效应和耦合效应的影响,产生干扰辐射,本系统主要从PCB设计、接地设计和屏蔽设计等几个方面进行电磁兼容设计[10]。

PCB设计是频率源设计的最初步骤,布局的关键是使RF路径上的元器件定位,通过调整元器件方向,使RF路径的长度最小,使输入与输出、高功率电路与低功率电路、数字信号和射频信号有效隔离[11]。

接地设计是使接地阻抗接近于零,以使信号回流路径阻抗最小。合理的接地设计可抑制电磁噪声、减少电磁对电路的干扰。

屏蔽设计是通过切断场之间的耦合方式来提高射频电路之间的隔离度,可抑制高频电磁场之间互相干扰。频率源设计依照电路功能的不同分开几个单元进行屏蔽,如小步进锁相源采用管壳封装,大步进锁相源采用铝合金盒体,混频、倍频电路采用局部镀金的铝合金盒体进行屏蔽。

3 频率源电路实现

频率源设计主要依靠工艺进行电路的实现,本设计中应用了3种工艺:表面组装工艺(SMT)、高温共烧陶瓷工艺(HTCC)和多芯片组件工艺(MCM)。

3.1 表面贴装工艺

SMT是指通过一定的工艺、设备、材料将表面安装器件贴装在PCB(或其他基板)表面,并进行焊接、清洗、测试而最终完成组装。SMT工艺按组装方式可分为全表面组装、单面组装和双面组装[12]。

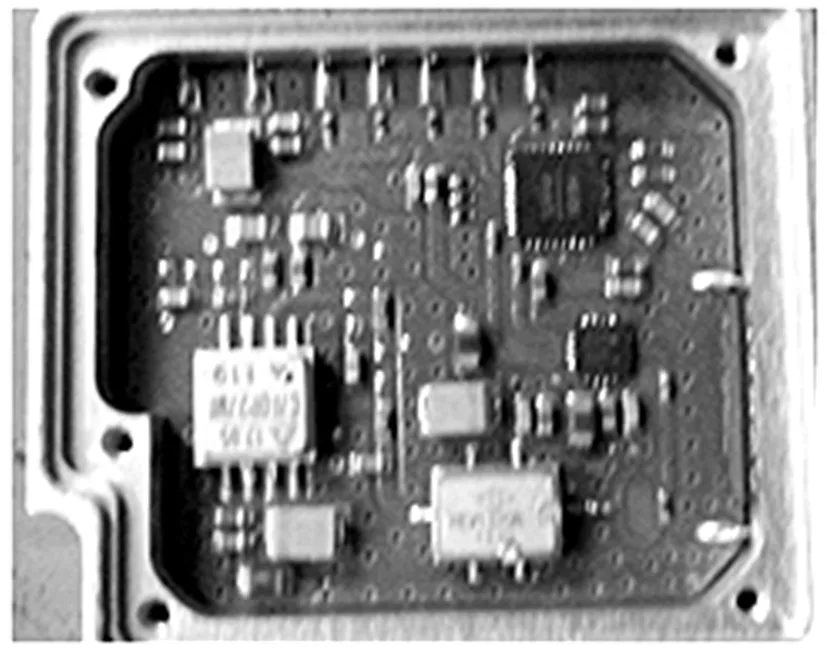

大步进锁相源使用了较多表贴元器件,适合采用SMT工艺,因其发热量较大,所以采用单面组装,底面烧焊在盒体上,以利于散热,实物图如图8所示。

图8 小步进锁相源实物

3.2 高温共烧陶瓷工艺

氮化铝陶瓷作为一种典型的高温共烧陶瓷,是一种新型的高导热基板和封装材料,具有高热导率、低热膨胀系数、低介电常数、低介质损耗和高机械强度等特点[13]。HTCC是MCM中的多层布线基板技术,利用该技术将多个集成电路芯片和其他元器件高密度组装在多层互连基板上,然后封装在同一壳体内,以形成高密度、高可靠的专用电子产品。

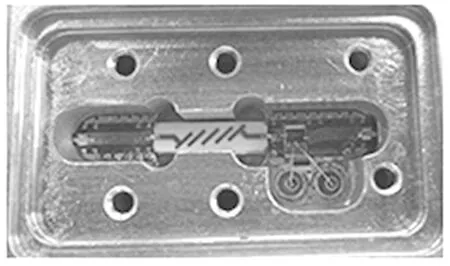

小步进锁相源采用HTCC工艺,版图和管壳一体化设计,将VCO、鉴相器和环路滤波器集成,使其小型化。锁相源内有参考信号、分频信号、射频信号和数字信号等多种信号,小型化后信号容易相互串扰。在频率源设计时,将电源信号、数字信号和射频信号分布在不同的层,通过过孔层压技术实现电气及微波互连,实现了较高的杂散抑制。小步进锁相源电路的实物图如图9所示。

图9 小步进锁相源实物

3.3 多芯片组件工艺

MCM是将多块未封装的芯片高密度安装在同一块基板上构成的部件,省去了芯片的封装材料和工艺,节约了原材料,减少了制造工艺,缩小了组件封装尺寸和重量。MCM是高密度组装产品,其互连长度极大缩短,与封装好的表贴元器件相比,减少了外引线寄生效应对电路高频、高速性能的影响,芯片间的延迟减少了75%[14]。

本设计中的倍频、滤波等电路工作频率较高,器件之间的连通需要良好的匹配,必须减少连通过程中寄生效应的影响,所以该部分电路实现采用多芯片组件工艺。此部分实物图如图10所示。

图10 倍频、滤波电路实物

4 频率源测试结果分析

4.1 相位噪声测试结果分析

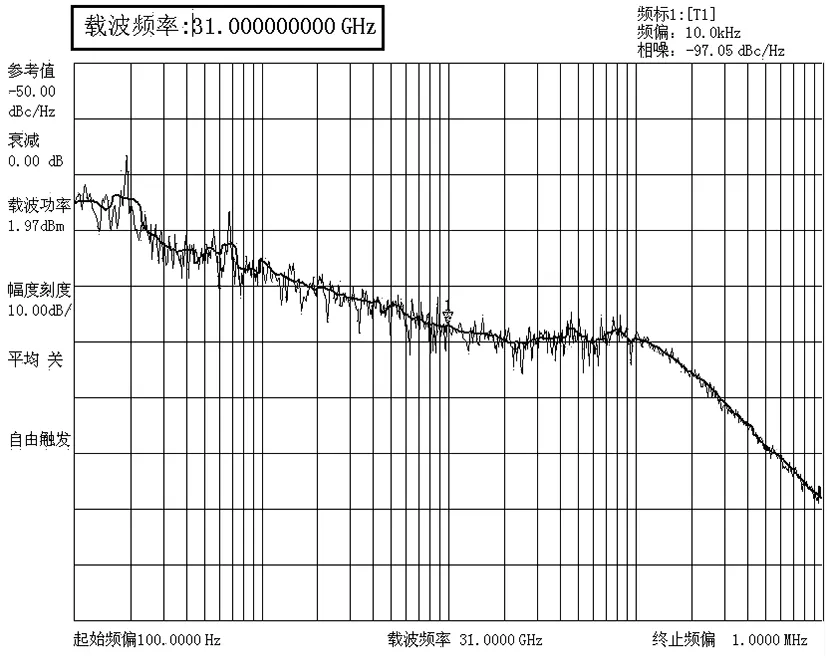

最终输出信号偏离主频10 kHz处的相位噪声测试结果如图11所示。

图11 最终输出信号相位噪声测试结果

由图11可得,最终输出信号实测相位噪声为-97.0 dBc/Hz@10 kHz,与理论计算结果相差3 dB。这是因为理论计算及仿真都是在理想情况下进行的,而实际阻容元器件等会带入热噪声,电源噪声也会使有用信号相位噪声恶化。

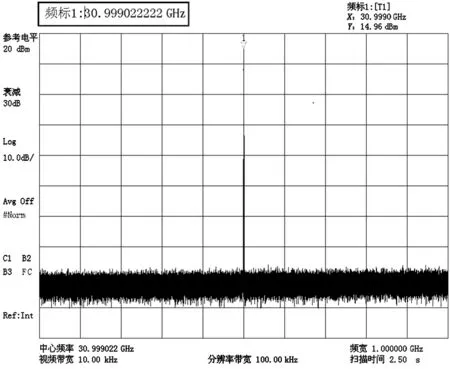

4.2 杂散抑制测试结果分析

最终输出信号杂散抑制测试结果如图12所示。由图12可得,输出信号功率为14.96 dBm,杂散抑制在75 dB左右,这表明各单元电路电磁兼容设计良好,未有互相串扰现象,混频频率选取比较恰当,混频后和倍频后的滤波效果比较好。

图12 杂散抑制测试结果

4.3 跳频时间测试结果分析

用示波器对跳频时间进行测试,单片机发数时间为6 μs,这是因为单片机使用了SPI技术,使其实际发数时间与预测值比有了提高。最终输出信号跳频时间是小步进锁相源和大步进锁相源混频后的结果,测试值为16 μs,全温下全带宽总跳频时间为22 μs。

目前国内公布的同频段频率源产品,相位噪声大多在-92 dBc/Hz@10 kHz,本设计与之对比有了5 dB左右的提高,优势明显。杂散抑制和跳频时间达到了同类型设计较高水平。本设计使用锁相实现跳频并不是最快跳频方式,要实现高速跳频必须使用DDS技术,但是DDS有其局限性,并不适合应用在某些系统。

5 结束语

本文综合直接频率合成和锁相2种方式的优点,通过合理分配小步进锁相源和大步进锁相源的

频率,采用高性能的元器件、合理的电路设计和电磁兼容设计,实现了系统低相位噪声、快速跳频和高杂散抑制的信号输出。测试结果表明,采用综合方式设计的频率源比采用单一方式实现的频率源具有更高的指标优势。今后在混频环锁相、VCO电压预置和DDS技术等方面进一步探索,使频率源实现更低相位噪声、更快速度跳频,以满足电子设备发展的需要。

[1] 张建斌.锁相与频率合成[M].北京:科学出版社,2011.

[2] 王福昌,鲁昆生.锁相技术[M].武汉:华中科技大学出版社,1997.

[3] 冯占群,李洪涛,宋旸.基于DDS的Ka频段小步进捷变频频率综合器设计[J].无线电工程,2017,47(7):86-89.

[4] 弋稳.雷达接收机技术[M].北京:电子工业出版社,2005:128-129.

[5] 彭志华,周存麒.C波段低相噪频率合成器设计[J].无线电工程,2012,42(3):44-46.

[6] Analog Devices Inc.ADF4106 Datasheet[R],2015.

[7] Analog Devices Inc.HMC704LP4E Datasheet[R],2015.

[8] 徐建华,陈静,丁海春.低相噪捷变频毫米波频率源的研制[J].固体电子学研究与进展,2016,36(4):274-278.

[9] 高玉良.现代频率合成与控制技术[M].北京:航空工业出版社,2002.

[10] 代宪菊.射频电路抗干扰设计方法研究[J].通信技术,2012(8):51

[11] 李雷.高频电路PCB设计[J].安徽电子信息职业技术学院学报,2013(2):65-67.

[12] 刘星星,许雪娟.表面组装技术SMT及其工艺探讨[J].信息通信,2015 (1):284.

[13] 余雷,揭海,王安劳.基于高温共烧陶瓷基板的三维互连技术[J].电子科技,2013,26(7):157-159.

[14] 鲜飞.多芯片组件(MCM)技术的发展及应用[J].印制电路信息,2005(10):65-68.