检测PLL稳定的方法

2018-04-26杨卫平

杨卫平

(珠海格力电器股份有限公司,广东 珠海 519070)

1 PLL简介

锁相环(Phase Locked Loop,PLL)是一种反馈控制电路,主要用于产生时钟。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。按照架构来分,锁相环可分为模拟锁相环、 数字锁相环、数模混合型锁相环。

模拟PLL中所有电路由模拟电路实现,主要包括鉴相器(Phase Detector,PD)、环路滤波器(Loop Filter,LF)和压控振荡器(Voltage Controlled Oscillator,VCO)3部分。一般情况下,模拟锁相环精度较高,起振和稳定的时间较短,适用于对时钟性能要求较高的场景。

数字PLL中所有电路由数字电路实现,结构包括鉴相器、低通滤波器(Low Pass Filter,LPF)、数字振荡器(Digital Controlled Oscillator,DCO)与分频器(Dividor,DIV),其中LPF输出控制字(Control Word,CW)对DCO进行控制,如图1所示。随着数字电路的发展,数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点,此外还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。

数模混合锁相环则由数字电路与模拟电路混合实现。例如LPF与VCO由模拟电路实现,而PD与DIV由数字电路实现。

图1 数字PLL结构

2 PLL稳定检测方法分析

PLL是时钟的供给源,一般只有当PLL稳定后才能输出使用,不然可能导致应用逻辑混乱,因此PLL是否稳定对判断十分重要。判断PLL稳定的方法有多种,根据较常见的电路,通常可以有如下几种。

2.1 直接计数法

PLL设计一般有RESET(复位)或POWER DOWN(断电)的控制功能。当PLL从复位或断电的状态转到工作状态时,由PLL输出时钟CLK_OUT或外部输入的参考时钟REF_CLK作为计数器时钟开始计数,当计数器达到门限即认为PLL振荡已经稳定。这样做的好处是算法简单,但不同条件下PLL电路达到稳定的计数门限不好把握:如果门限取太小,则可能出现虚假的PLL稳定结论;如果门限太大,则等待时间较长,影响系统使用;甚至出现严重的误判,那就是PLL根本就不会稳定,但计数器满后,误报PLL稳定。因此直接计数法具有较大的局限性,就算计数器门限可配,也只适用于一定会稳定并且稳定时间有确定范围的PLL。

2.2 借助UP/DOWN判断法

PLL电路中包含PD模块,一般PD模块会输出UP/DOWN两个信号,UP=1表示REF_CLK比DIV_CLK相位领先,DOWN=1表示REF_CLK比DIV_CLK相位落后,或者根据实际电路反过来。从PLL起振到稳定,一般UP/DOWN有如下规律。

(1)随着PLL起振,UP=1/DOWN=0,如果PLL能稳定,则UP=1宽度会逐步减小;(2)到某时刻,UP由1->0,DOWN由0->1,并且DOWN=1宽度会逐步增大然后逐步减小;(3)到某时刻,DOWN由1->0,UP由0->1,并且UP=1宽度会逐步增大然后逐步减小;(4)按2,3特点循环,但UP/DOWN交替变化逐渐频繁并且UP/DOWN最大宽度会逐步变小;(5)如果有外界因素干扰,UP/DOWN会重复2,3,4过程。因实际硬件电路存在延时,UP/DOWN可能存在短暂同时为0或1的情况。

根据UP/DOWN的以上规律,设计电路判断UP/DOWN的变化趋势,当达到某条件时可以认为PLL达到稳定状态,例如:UP/DOWN交替变化达到一定次数,或者UP/DOWN最大脉冲宽度小于设定的某门限值等。具体电路不一样,但电路原理与总体框图类似。

相比直接计数法,借助UP/DOWN判断PLL稳定的方法更加准确,确保PLL已经达到稳定状态,并且反映PLL稳定状态也较及时。但复杂应用环境,UP/DOWN判断算法可能会比较复杂。

3 本文PLL稳定检测方法

本文提出一种基于CW规律检测PLL是否稳定的方法。一般数字PLL中,LPF输出CW来控制DCO,因此CW可以从PLL电路直接获取。一般的SoC设计中都会包含ADC(模数转换模块),利用该模块,可以将模拟PLL或混合型PLL中LF输出的模拟控制信号数字化得到CW,用于PLL稳定的判断。因此,基于CW检测法在数字PLL、模拟PLL和混合型PLL均可应用。

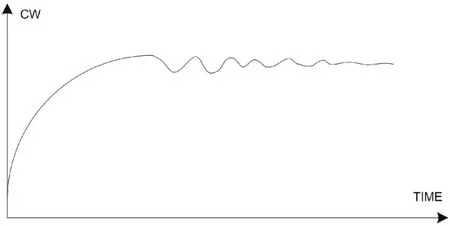

如果PLL能稳定,一般CW的变化趋势如图2所示。PLL开始工作之后,CW会随之增大(或减小,取决于实际电路),趋于稳定时会出现振荡,但会逐步收敛并最终趋于稳定。因此,CW的振荡变化就成了PLL稳定的判断因素。

图2 CW变化趋势

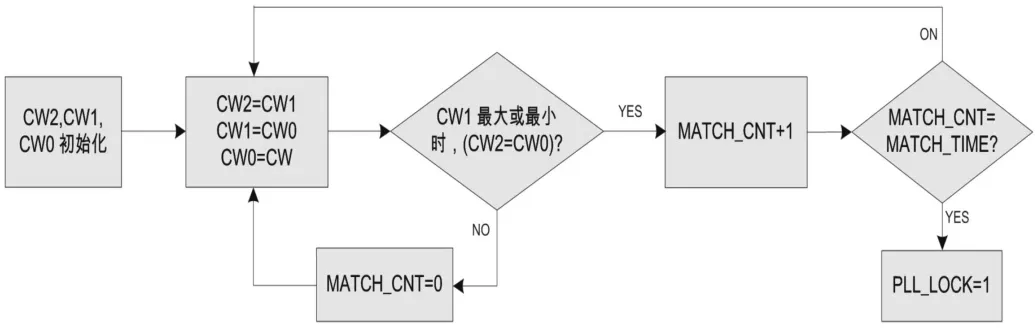

基于CW的这一规律,本文设计一种PLL稳定检测电路。电路输入信号主要有参考始终REF_CLK、复位信号RESET、配置信号CONFIG以及CW信号,输出信号为PLL_LOCK. 定义3个数字信号CW0,CW1与CW2,用于记录连续的3个CW。定义数字信号MATCH_CNT,用于记录满足条件的次数,条件是CW1处于最高点(CW1>CW2且CW1>CW0)或最低点(CW1<CW2且CW1<CW0)时CW2=CW0。定义数字信号MATCH_TIME,用于表示要求达到条件的次数,条件是CW1处于最高点或最低点时CW2=CW0。电路主要包括4个模块。

(1)初始化模块INIT_REG.INIT_REG模块获取配置的信息,包括CW0~CW2的初始值、MATCH_TIME值。

(2)CW获取与比较模块LATCH&COMPARE.LATCH&COMPARE模块获取连续的CW0~CW2,并进行比较判断,看是否满足条件,即CW1处于最高点(CW1>CW2且CW1>CW0)或最低点(CW1<CW2且CW1<CW0)时CW2=CW0.

(3)匹配记录模块MATH_CNT_GEN. MATH_CNT_GEN模块对MATH_CNT进行判断并记录。

(4)稳定判断模块LOCK_JUDGE. LOCK_JUDGE模块判断MATH_CNT值是否达到MATCH_TIME要求,并输出PLL_LOCK状态。其中MATCH_TIME值是可配置的,值越大表示稳定判断越严格。

完整的PLL稳定判断流程如图3所示。对CW0~CW2赋予3个极限初值,随着PLL起振,在REF_CLK的上升沿或下降沿时,CW0~CW2不断被赋予连续3个时刻的CW.CW1处于最高点或最低点时,若出现CW2=CW0的情况,则将MATCH_CNT的值加1,不然将MATCH_CNT清0。若MATCH_CNT达到要求次数MATCH_TIME,则表示PLL达到稳定状态,输出PLL_LOCK=1.

图3 PLL稳定判断流程

4 实际仿真结果及分析

运用本文推荐基于CW检测PLL稳定的方法与电路,在数字PLL稳定进行判断,效果如图4所示。在图中,随着CW变化,当CW1处于最高点时并出现CW2=CW0的情况,则将MATCH_CNT的值加1,很快MATCH_CNT值达到MATCH_TIME,PLL_LOCK=1。另外,仿真过程中发现,MATCH_TIME越大,由于条件更严格,PLL_LOCK=1时间变长。由仿真结果可见,PLL稳定结果准确并且用时较短。

5 结语

本文提出基于CW检测PLL稳定的方法相比直接计数法与借助UP/DOWN判断法,判断结果准确,算法简单,应用于任何含有PLL的芯片或电路中,特别适用于数字PLL、系统中同时含有ADC电路的模拟PLL或混合PLL。

图4 PLL稳定判断仿真

[参考文献]

[1]DEN DULK R C.Digital PLL lock-detection circuit[J].Electronics Letters,1988(24):14.

[2]VOLODYMYR K,PAVAN K HANUMOLU,K et al.Moon school of the EECS,a digital PLL with a stochastic time-to-digital converter[D].Oregon:Oregon State University,2006.

[3]STENSBY J.A new lock detector for phase-lock receivers[J].Symposium System Theory,2001(1):215-219.

[4]文武,魏慧婷,文治平,等.一种基于全数字动态加速锁定技术的PLL频率综合器[P].2014-04-23.