基于FPGA+STM32的多通道数据采集系统设计

2018-01-04范君健吴国东王志军朱嫣霞

范君健,吴国东,王志军,朱嫣霞,张 冲,纪 录

(中北大学 机电工程学院, 太原 030051)

【基础研究】

基于FPGA+STM32的多通道数据采集系统设计

范君健,吴国东,王志军,朱嫣霞,张 冲,纪 录

(中北大学 机电工程学院, 太原 030051)

针对武器测试系统中数据采集的高速与实时性要求,提出了一种基于FPGA+ARM的数据采集系统设计方案。该数据采集系统采用FPGA+STM32的协处理器+主控制器方案设计多通道模拟量采集模块,利用FPGA灵活的逻辑可操作性设计实现多通道数据的同步采集,同时设计FIR数字滤波器以提高采集数据的可用性,利用STM32丰富的外设功能和数据处理能力,加入SD卡、USB接口以及以太网接口,用于数据的存储与导出。对主要模块进行仿真与测试,验证了该方案的可行性。

数据采集;FPGA;FIR滤波;FSMC;以太网

随着数字电子技术的飞速发展,高精度多通道的数据采集系统已经在测量测控领域占据了主要地位,被广泛的应用于工业、民生和军事等的各个领域,测量项目主要为观测电压和电流、温湿度与功率功耗等,后期用于数据的分析、系统的改善等[1]。现阶段单独基于FPGA和ARM的采集板很多,但将两者作为主协处理器配合完成采集、分析、计算和通讯的系统很少,在此提出一种基于FPGA和STM32的数据采集系统设计方案,其中FPGA负责多通道数据的同步采集与缓存,STM32负责数据处理、存储以及和上位机的通信传输。在系统总体方案的基础上,进一步讨论STM32与FPGA的通信接口、FIR滤波器的设计、数据缓存、以太网通讯等关键部分。该系统能够完成对多路信号的实时采集,具有高速信号处理与数据传输的能力。

1 系统总体设计

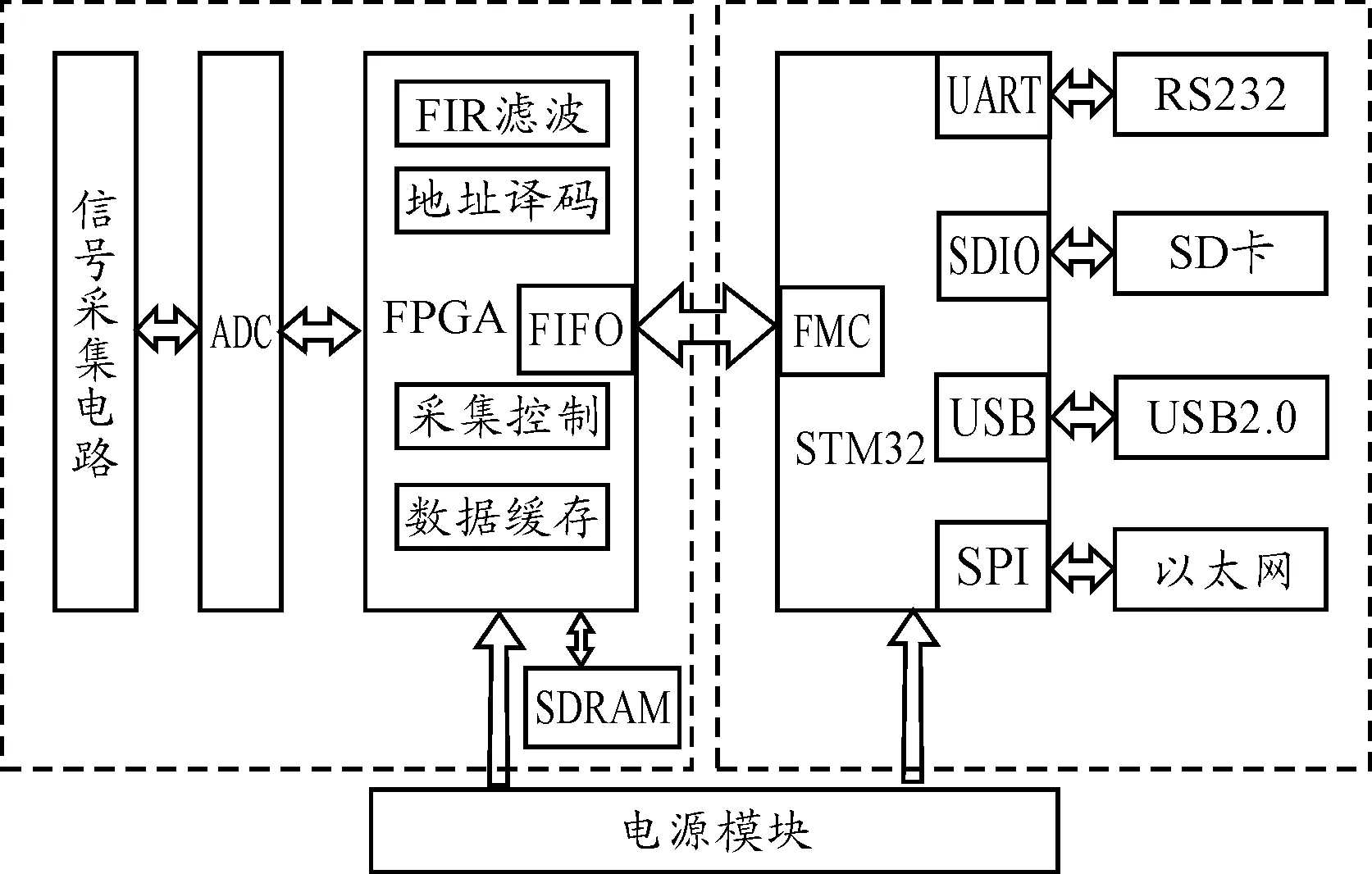

该设计中使用的FPGA采用Altera公司CycloneIV E系列的EP4CE10F17I7N,ARM芯片采用ST公司的STM32F407系列,STM32与FPGA通过FSMC(Flexible Static Memory Controller,可变静态存储控制器)接口连接,并加入256Mb的SDRAM作为数据缓冲器。选择AD7606作为AD转换芯片,该芯片是一款完全集成的多通道数据采集解决方案[2],有8路同步采样输入,内置16位、双极性ADC,所有通道转换速度均达到200ksps,并提供过采样功能,且AD7606提供高速串行接口、并行接口和并行字节接口,方便与FPGA直接连接[3]。设计RS232串口方便与工控机进行数据交换,选用USB3300芯片设计USB2.0接口用于数据导出,选用W5500设计以太网接口,以便通过上位机进行系统设置与数据实时传输,系统的总体设计结构框图如图1所示。

图1 系统总体设计结构

该高速多通道同步数据采集系统具有如下的功能特点:

1) 通过以太网或RS232接口可直接与上位机控制终端通讯,及时完成测试现场的数据采集与传输,并实现对数据采集终端的控制;

2) FPGA系统设计了异步FIFO与SDRAM,支持信号的长时间连续采集;

3) 支持数据的移动与远程存储,采集数据可通过存储卡或者网络进行存取[4]。

2 系统硬件结构设计

该系统由模拟数据采集、数据缓存、数据通讯、电源及系统时钟同步等几大模块组成,对其中关键的FIR滤波器设计、FPGA与STM32通讯的FSMC接口设计做详细的阐述。

2.1 FSMC接口电路设计

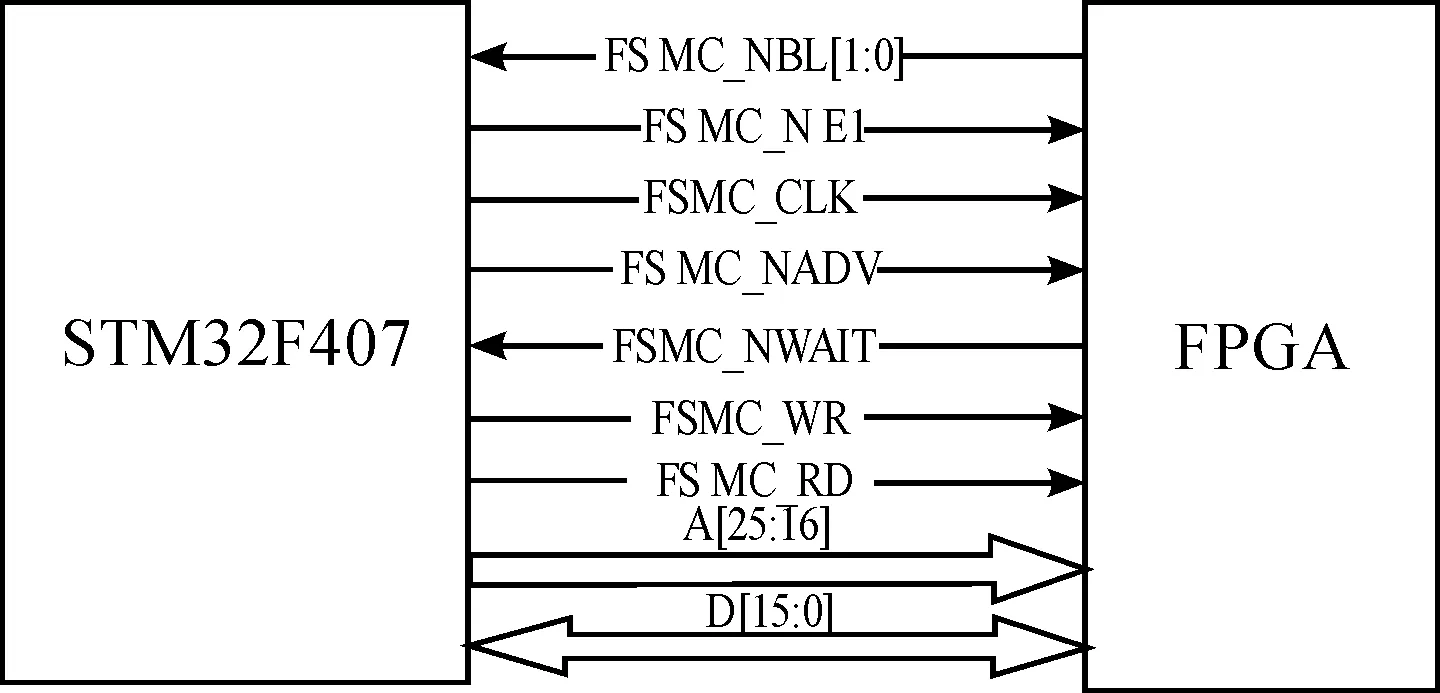

FSMC是STM32系列采用的一种新型的存储器扩展技术,支持不同的外部存储器类型,其中包括多种类型的静态存储器[5],因此,可将FPGA当作STM32F407的外部SRAM来配置,通过扩展出的数据/地址/控制三总线来实现操作,这样既能保证较快的操作速度,又具有很高的灵活性[6]。接口硬件连接原理图如图2。

图2 STM32与FPGA连接原理图

将FPGA直接挂载到STM32的FSMC总线上,FSMC提供了4个Bank用于连接不同的外部存储器,FSMC_NE1为Bank1第一区的片选信号,FSMC_WR和FAMC_RD分别为接口读写信号,根据设计的数据要求,设计数据位宽16位,地址位宽10位,将数据线D[15:0],地址线A[25:16]连接到FPGA的I/O端口,这样FPGA就作为STM32的外设接入,通过存储器读写指令访问FPGA。

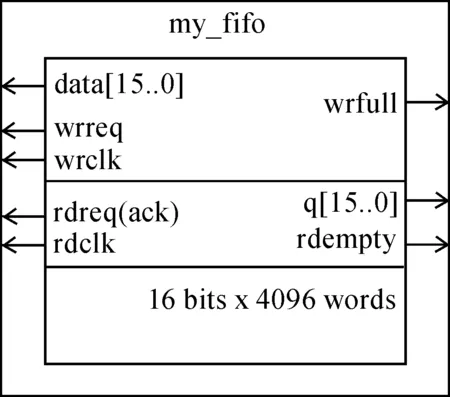

在FPGA的数据接口设计当中数据采集与FSMC总线的数据传输处于不同的时钟域,而数据在不同时钟域之间传递,容易产生亚稳态[7]。通过IP核设计异步FIFO用于数据的缓存与传输,采用两个时钟信号来控制其读写操作,分别为写时钟(wrclk)和读时钟(rdclk)。FIFO的模块简图如图3所示。其中异步FIFO模块包括8个端口,别为数据输入(data[15:0])、写请求(wrreq)、写时钟(wrclk)、读请求(rdreq)、读时钟(rdclk)、缓冲器满信号(wrfull)、缓冲器空信号(rdempty)、数据输出(q[15:0])。

图3 异步FIFO的模块简图

2.2 数字滤波器设计

在模拟信号采集电路当中,由于环境噪声与电源噪声的存在,其不可避免的会引入ADC芯片进行模数转换,这些噪声在数字系统的运算当中可能会被放大,从而影响测量精度,因此在FPGA内部创建数字滤波器,以进一步提高信噪比。

相比于完全依靠电阻、电容、晶体管等电子元件组成的模拟滤波器,数字滤波器具有更高精度、更高信噪比、无可比拟的可靠性等优点,虽然在其搭建过程当中工作量大、调试设计复杂,但其换来的灵活性与可扩展性可大大降低硬件电路板的设计及制作成本[8]。有限脉冲响应(Finite Impulse Response, FIR)滤波器由于其具有良好的线性相位和极高的稳定性,在数字信号处理领域得到了极为广泛的应用[8]。N阶FIR滤波器的输出y(n)可表示为输入序列x(n)与单位取样响应h(n)的线性卷积,如函数式(1)所示:

(1)

每一次的输出要完成N次的乘法和N-1次的加法,当阶数N较大时,系统延迟会很大。

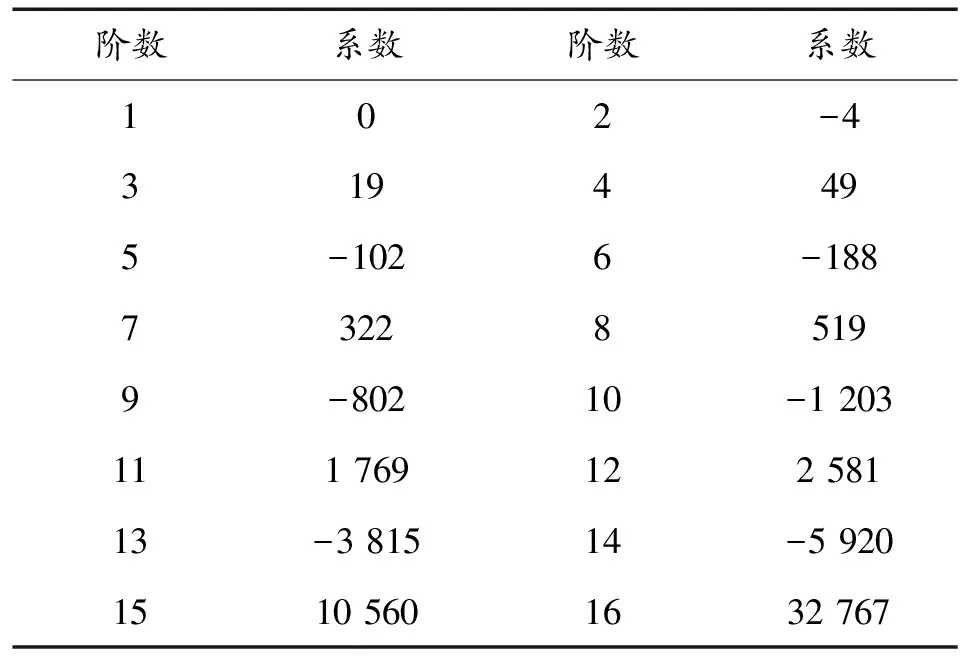

根据AD7606数据传输速度,设计低通线性相位FIR滤波器截止频率为250 kHz,阶数为31(滤波器长度32),采样频率1 MHz,量化系数为16比特。为提高设计效率和系统可靠性,首先通过Matlab设计出滤波器系数,而后将其导入到Quartus II的FIR IP核当中,直接生成FIR滤波器模块。为获得更高的运算速度,选择全并行分布式算法结构[9],FIR滤波器系数如表1所示,FIR滤波器系数量化前后频谱图如图4。

表1 FIR滤波器1~16阶系数

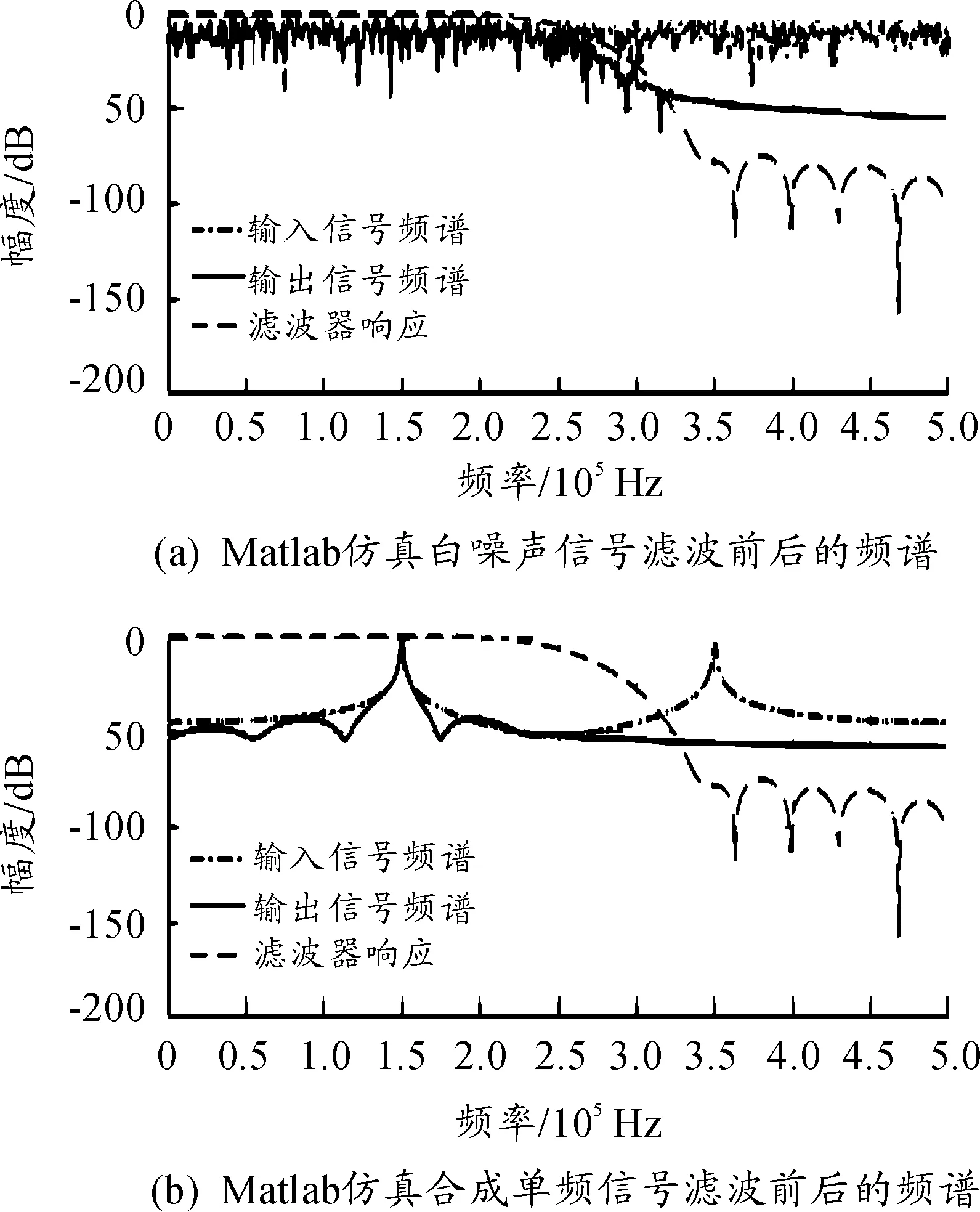

采用Matlab软件仿真出具有白噪声特性的输入信号,以及由150 kHz和350 kHz单频信号叠加的输入信号,进而仿真测试数据经滤波器滤波后的输出数据,以便和FPGA设计实现后的结果进行比较。Maltab仿真的信号滤波前后频谱如图5。

图5 Matlab仿真的信号滤波前后的频谱图

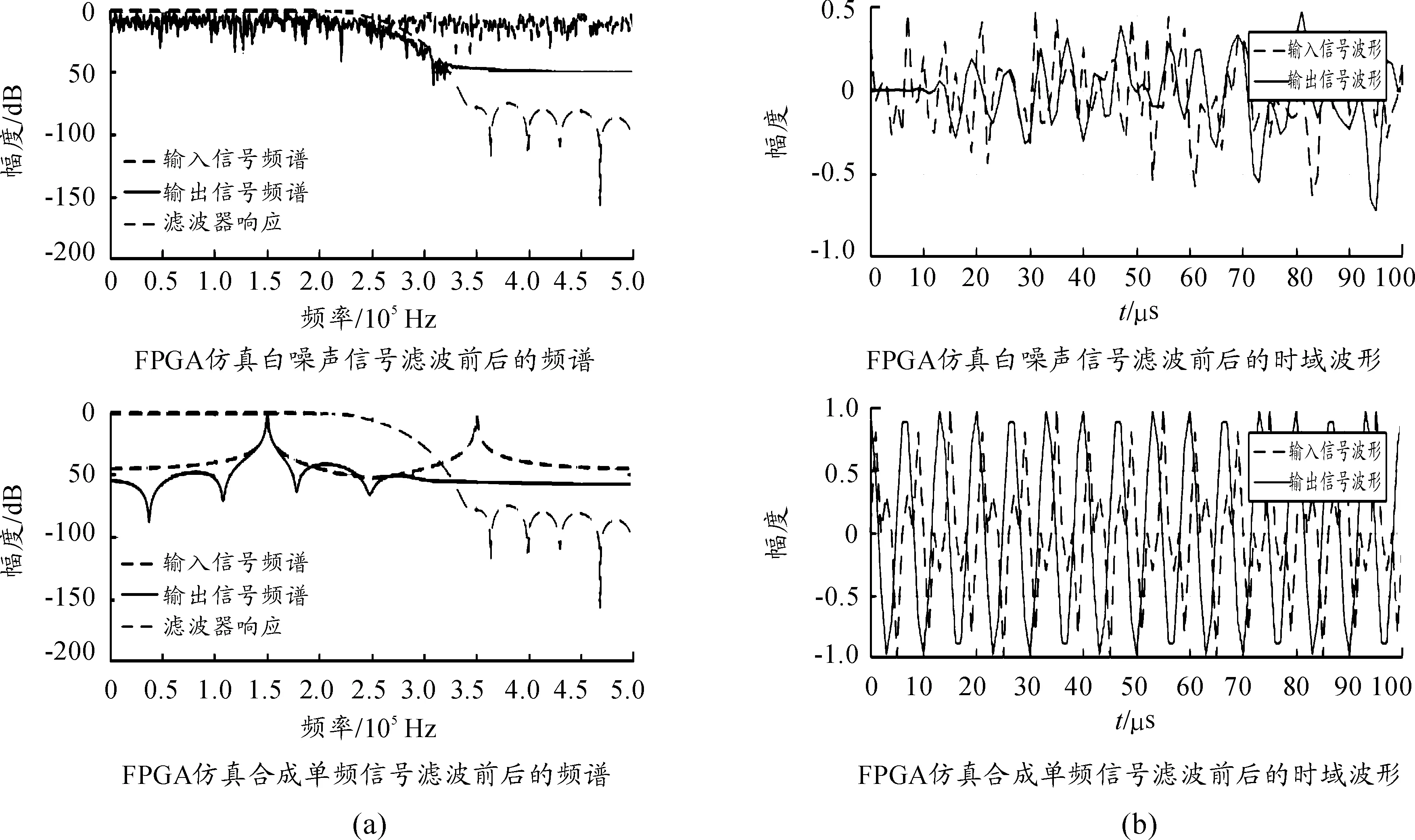

在FPGA设计完成后,将仿真的输入信号作为ModelSim的激励源,生成经FPGA滤波器的输出信号,对输出信号数据进行时域及频域分析,如图6(a)和图6(b)所示。

从图6(a)可以看出,FPGA实现的滤波器输入、输出频谱与Matlab直接仿真的结果相同。从图6(b)可以看出,滤波后的白噪声在时域上的变化趋势明显缓和,即滤除了高频分量,滤波后的合成单频信号已形成规则的频率为150 kHz的信号。因此,从仿真结果看,该滤波器的FPGA实现满足设计要求。

2.3 AD控制模块

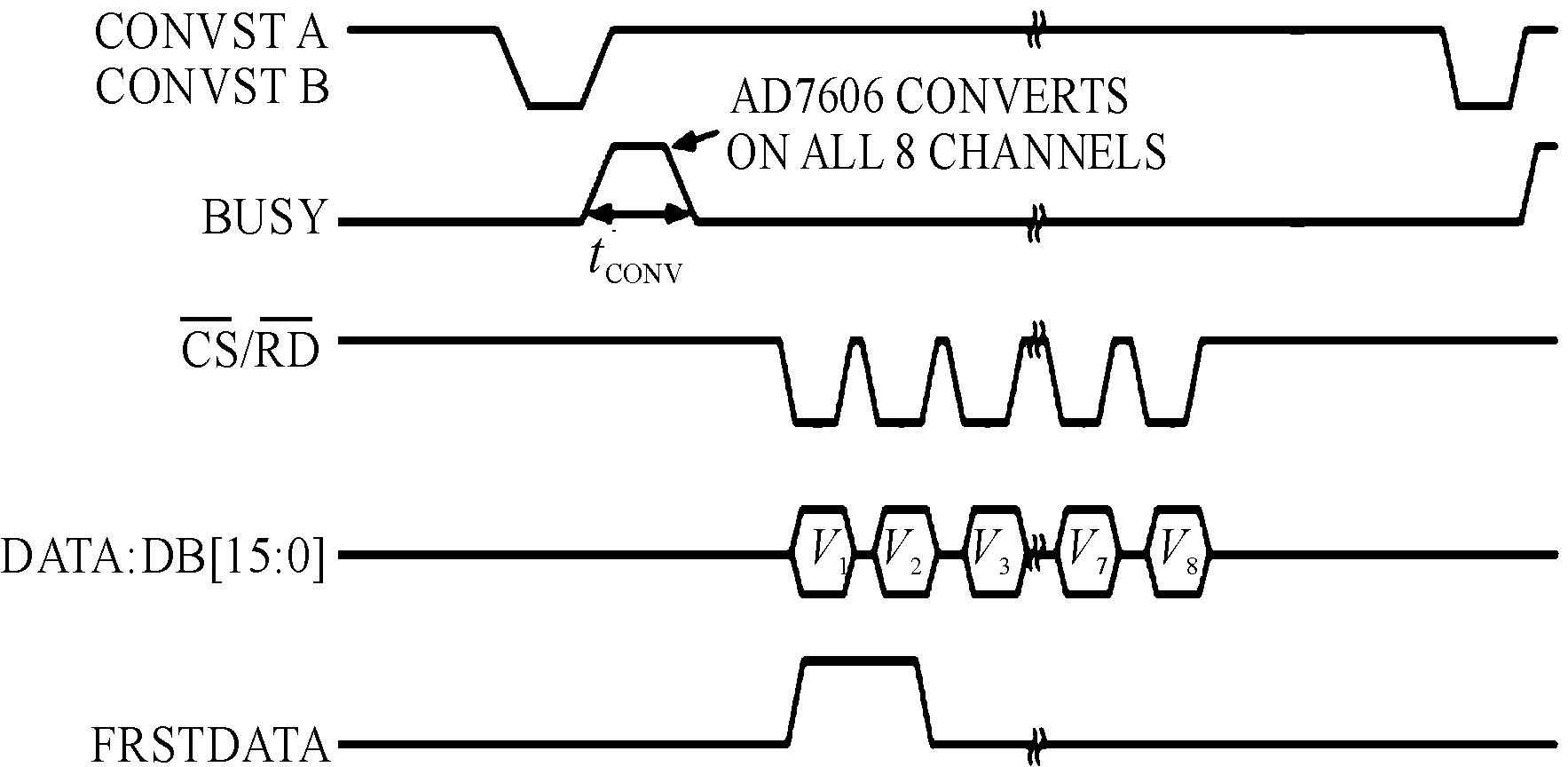

AD控制模块用来完成AD7606数据采集时序的控制,为确保时序的准确性和连续性,采用状态机的方式来实现。将两个CONVST引脚连在一起,以保证采集数据的实时性与同步性,设置AD7606为通道同步采样模式,此公用CONVST的上升沿启动对所有模拟通道的同步采样,AD7606的同步采样时序图(并行模式)如图7所示。

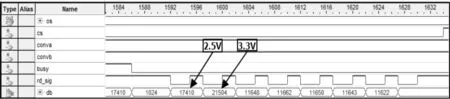

AD采样控制使用Verilog语言来描述,使用SignalTap II逻辑分析仪对控制时序进行验证,如图9所示,通道1和通道2分别为测量的2.5 V参考电压与3.3 V电源电压,可以看到AD控制器的时序与芯片参考手册提供的时序图相符,完成对模拟信号的采集。

图6 FPGA仿真的信号滤波前后的频谱图(a)和时域波形(b)

图7 AD7606通道同步采样时序图

图9 AD控制模块时序分析

3 系统软件流程设计

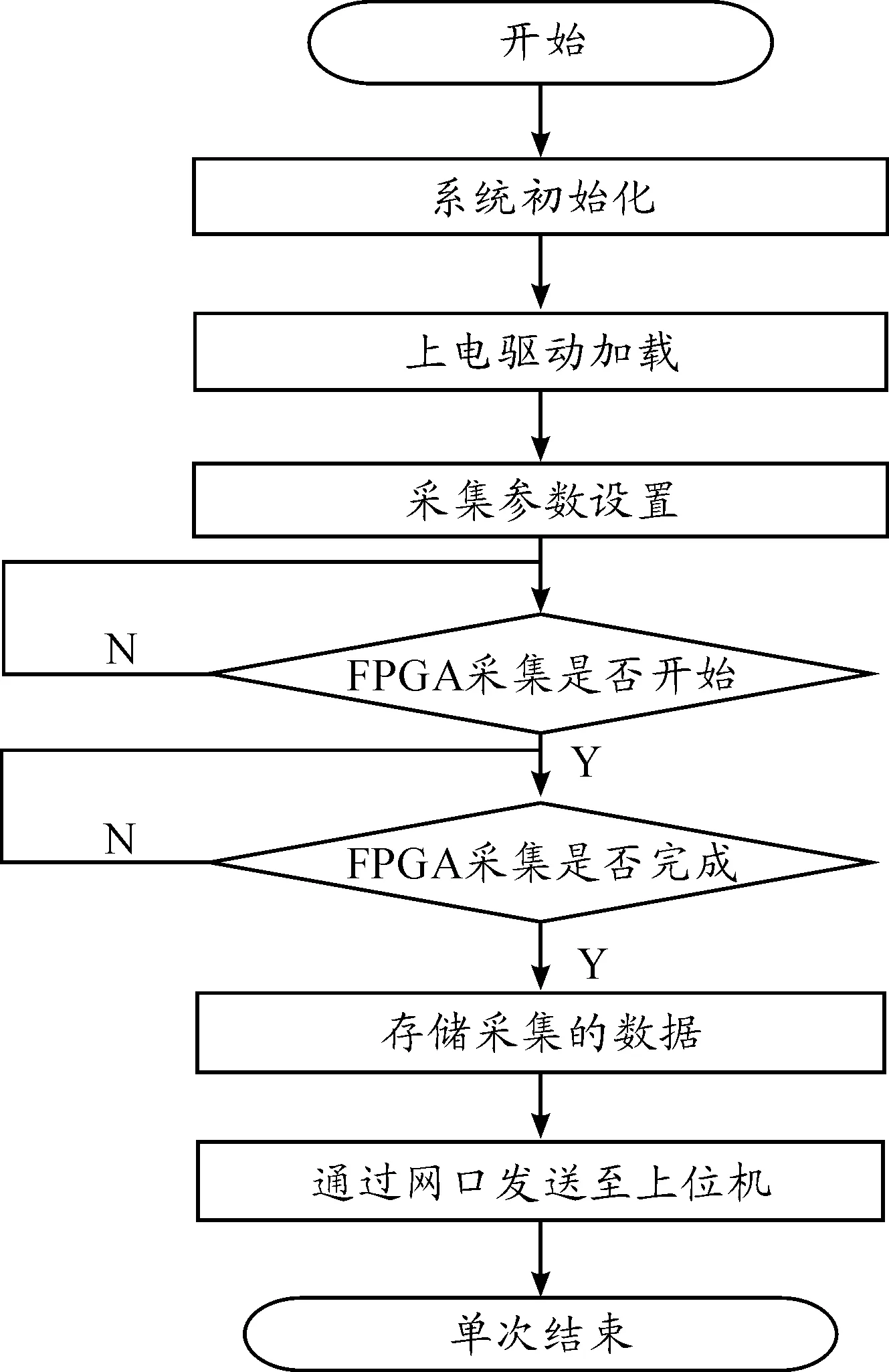

STM32作为系统的控制核心,主要负责FSMC接口驱动,采集数据的存储、实时显示,数据统计以及发送给FPGA的控制指令及参数设置等。STM32控制软件的流程如图10所示。

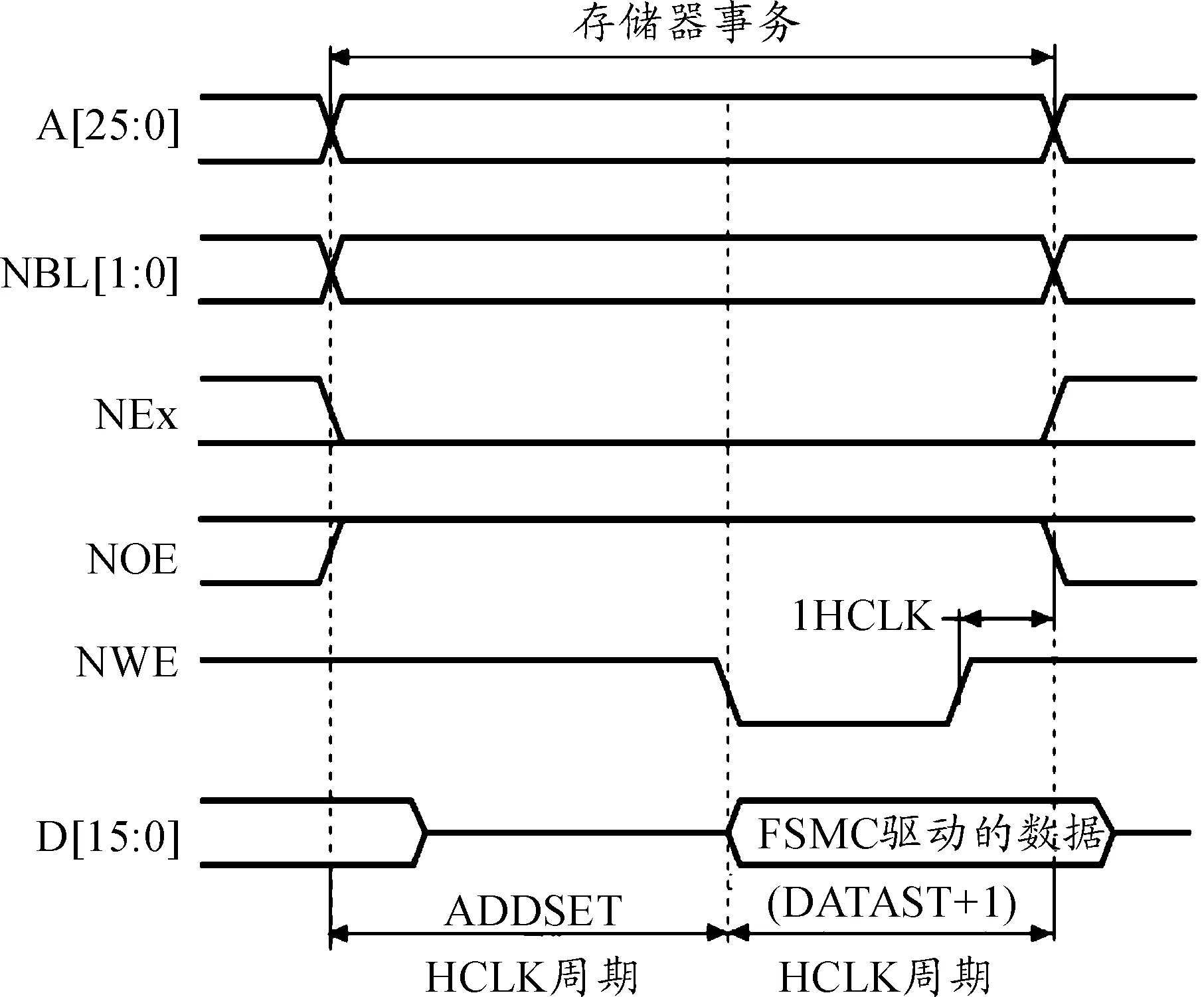

3.1 FSMC接口程序设计

在该设计中将FPGA通过FSMC接口映射为NOR控制器管理下的Bank1中的一段内存,起始地址为0x60000000。FPGA中的FIFO负责对采集数据的缓存,接收来自STM32的读写使能信号,复位信号,并且向STM32返回空、满信号。读写使能信号需要设置地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。该系统采用FSMC的模式1进行异步读写操作,允许读写使用不同的时序,模式1的写操作时序如图11所示。

图10 STM32软件设计流程

图11 FSMC模式1写操作时序

STM32的IO时钟设置为100 MHz,根据图11,设置写使能电平有效时间为FIFO时钟周期的两倍。FIFO满信号有效时,FSMC从FIFO读取数据,等待FIFO数据被读取,满信号无效后再次启动FIFO写命令。FIFO空信号有效时,FSMC停止从FIFO读取数据,直到空信号无效时启动FIFO读命令。

3.2 USB接口程序设计

在众多的USB设备类型中,HID类是Windows完全支持的第一批设备类型,它是为一些人工的输入输出设备而设计的,连接到计算机的USB设备几乎都包含HID类,用于信号控制[10]。

在该设计中利用ST公司的STM32系列USB固件库(STM32_USB-FS-Device_lib库)完成下位机HID类程序的开发。一个典型的USB包括外围硬件(hardware)、USB固件库和用户层(User application),USB固件库分为硬件驱动层和应用接口层,其中硬件驱动层管理USB的硬件设备和USB标准协议的直接交互,它又由Low Layer和Medium Layer两个层组成;而应用接口层又叫做High Layer层,它在固件库核和应用提供一个完整的接口。

STM32的USB程序主要包含三个部分:USB控制器初始化、主机请求响应和通讯数据收发。其中USB控制初始化包括端点的使能、中断方式、数据缓存设置等;至少需要响应获取描述符、设置地址、设置配置、设置闲置四种请求;通讯数据收发主要是以中断的方式向数据缓冲区读写数据。该设计根据ST公司提供的Custom_HID例程修改而来。

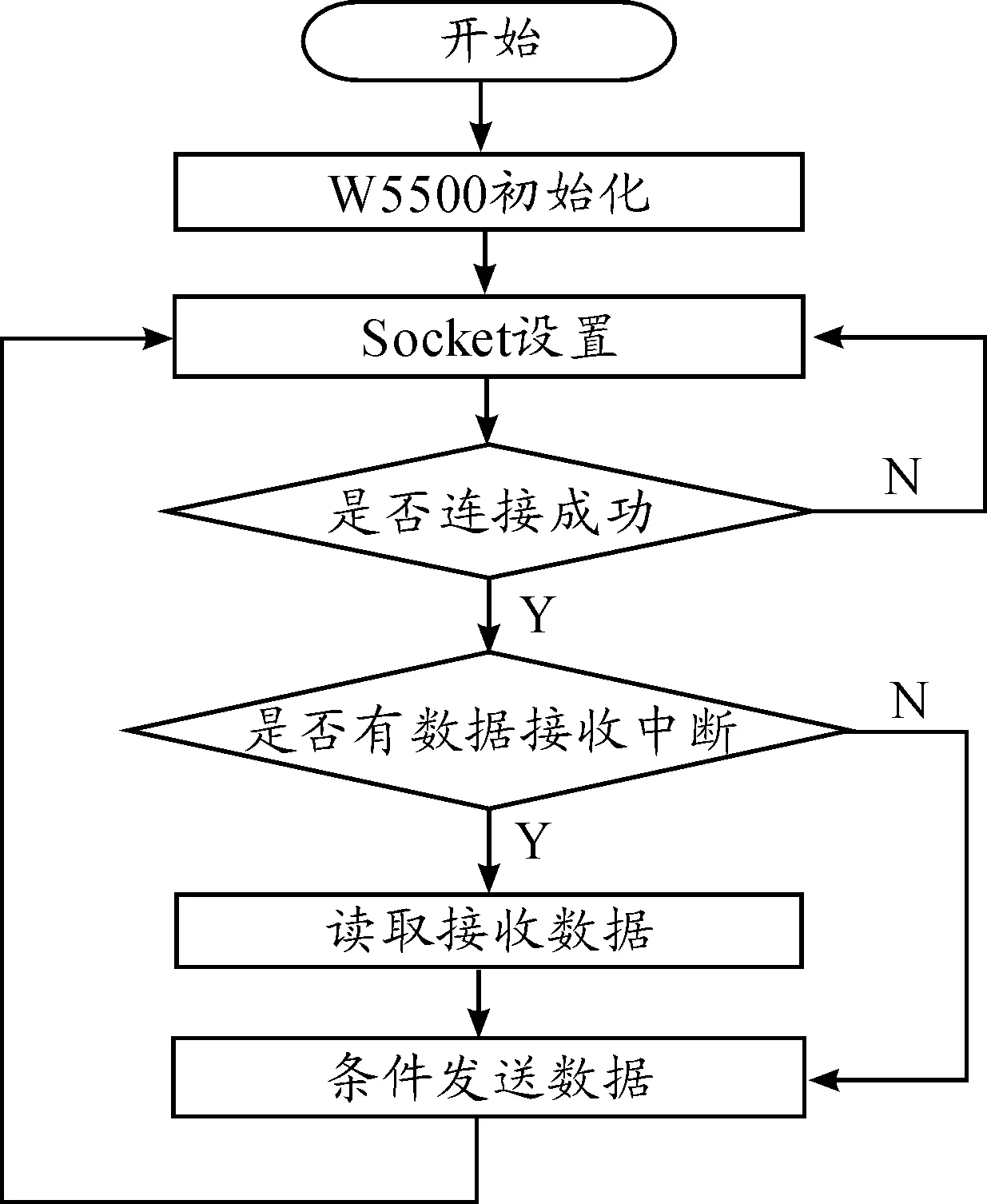

3.3 以太网接口设计

数据采集系统中加入W5500嵌入式以太网控制器,STM32通过SPI接口与之连接。W5500集成了TCP/IP协议栈,即芯片本身集成了网络层和传输层的相关协议,在软件的设计中只需要对芯片的相关协议参数进行初始化配置就可以实现以太网的数据收发[12]。使用W5500的软件设计流程图如图12。

图12 W5500软件设计流程

具体的初始化内容包括以下几个部分:

1) 配置本机MAC地址、网关地址、子网掩码和本机IP地址寄存器,配置目标主机IP地址寄存器;

2) 设置发送缓冲区和接收缓冲区的大小;

3) 设置重复发送超时寄存器和重复发送计数寄存器。

芯片初始化完成后检查网关服务器进行Socket设置,在数据的收发处理上采取条件发送中断接收的策略,在收发后重新检查网关服务器进行Socket设计,如此循环。

4 结论

本系统很好的结合了FPGA可编程逻辑器件和STM32控制器的优点,利用FPGA灵活的逻辑可操控性,有效地解决了数据采集的高速与实时性问题,同时利用STM32的FSMC接口和外设端口,极大的方便了数据的处理与高速传输,验证了该设计方案的可行性。简化了采用单一处理器的数据采集系统软件设计的复杂程度,缩短了开发周期。同时该系统保留了很大的可扩展性,有着广阔的应用前景和参考价值。

[1] 赵国.基于ARM和FPGA的多功能数据采集系统的研究[D].成都:电子科技大学,2014.

[2] 陶海军,张一鸣,曾志辉.基于AD7606的多通道数据采集系统设计[J].工矿自动化,2013,39(12):110-113.

[3] 于克泳,孙建军.新一代16位8通道同步采样ADC-AD7606在智能电网中的应用[J].电子产品世界,2010,17(10):63-65.

[4] 张素萍,高照阳,张建芬.基于FPGA和ARM的高速多通道数据采集系统设计[J].自动化与仪器仪表,2015(8):110-113.

[5] 潘辉.STM32-FSMC机制的NOR Flash存储器扩展技术[J].单片机与嵌入式系统应用,2009,9(10):31-34.

[6] 曹彬乾,程远增,杨青.基于STM32+FPGA的数据采集系统的设计[J].计算机工程与设计,2014,35(4):1231-1235.

[7] 杨会建,田成军,杨志娟,等.基于FPGA的SDRAM乒乓读写操作设计[J].长春理工大学学报(自然科学版),2015(2):67-71.

[8] 杜勇.数字滤波器的MATLAB与FPGA实现-Altera/Verilog版[M].北京:电子工业出版社,2015.

[9] 李伟,武鹏飞,陈宏霖.基于DSP Builder的分布式算法的FIR数字低通滤波器设计[J].计算机应用,2015(a02):335-338.

[10] 杨洪程,陈家新,张晓铀,等.基于USB HID类数据通信的直流电源监控设计[J].电子设计工程,2013, 21(13):97-100.

[11] 孙士诚,皮佑国, SUN Shicheng,等.基于STM32和FPGA的多路模拟量采集系统的设计[J].自动化与仪器仪表, 2015(4):23-26.

[12] 曾红,党盼盼.基于W5500的嵌入式系统以太网网关设计[J].网络安全技术与应用,2015(2):36-37.

DesignofMulti-ChannelDataAcquisitionSystemBasedonFPGAandSTM32

FAN Junjian, WU Guodong, WANG Zhijun, ZHU Yanxia, ZHANG Chong, JI Lu

(College of Mechatronic Engineering, North University of China, Taiyuan 030051, China)

Aiming athigh speed and real-time requirements for data acquisition in weapon testing systems, this paper presents a design scheme of data acquisition system based on FPGA+STM32. The data acquisition system uses FPGA+STM32 coprocessor and main controller program design multi-channel analog acquisition module. Realization of multi-channel data acquisition by FPGA flexible logic operability design, while the FIR digital filter is designed to improve the availability of data. Using STM32 rich peripheral functions and data processing capabilities, add the SD card USB interface and ethernet interface, for data storage and export. The simulation and testing of the main modules are carried out to verify the feasibility of the scheme.

DAQ; FPGA; FIR filter; FSMC; Ethernet

2017-09-20;

2017-10-15

国家自然科学基金资助项目(11572291);山西省研究生联合培养基地人才培养资助项目(20160033)

范君健(1993—),男,硕士研究生,主要从事弹药、武器系统相关测试研究。

10.11809/scbgxb2017.12.061

本文引用格式:范君健,吴国东,王志军,等.基于FPGA+STM32的多通道数据采集系统设计[J].兵器装备工程学报,2017(12):281-286.

formatFAN Junjian, WU Guodong, WANG Zhijun, et al.Design of Multi-Channel Data Acquisition System Based on FPGA and STM32[J].Journal of Ordnance Equipment Engineering,2017(12):281-286.

TP274.2

A

2096-2304(2017)12-0281-06

(责任编辑杨继森)