多物理场耦合研究电感线圈电镀铜

2017-10-12苏世栋冀林仙

苏世栋,冀林仙

多物理场耦合研究电感线圈电镀铜

苏世栋,冀林仙

(运城学院 物理与电子工程系,山西 运城 044000)

采用多物理场耦合方法构建了电感线圈电镀铜模型,通过有限元分析获得了电感线圈电镀铜过程中铜离子浓度分布、线圈表面电流密度与镀层分布状况,探讨了象形阳极与阴阳极距离对镀层厚度分布的影响。数值模拟结果表明,采用象形阳极与绝缘挡板有助于提高线圈表面镀层的均匀性。当阴阳极距离较小时,采用象形阳极电镀铜,镀层极差降低为0.21 μm,COV减小为0.5%。随着阴阳极距离的增加,镀层极差增大到9.5%,需要增加绝缘挡板来提高镀层均匀性。此时,镀层极差为0.14 μm,标准偏差COV值为0.4%。

印制电路;电感线圈;电镀铜;多物理场耦合;象形阳极;有限元分析

信息、通讯、消费性电子产品制造业的快速发展,使电子产品日新月异,并朝着体积小、质量小、多功能的方向不断发展[1-2]。电镀作为印制电路板(PCB)与电子元件表面重要的表面处理技术,在材料防护、精饰和获得功能性镀层等方面都具有举足轻重的地位,其制造品质直接影响电子终端产品的质量与可靠性。印制电路板精细导线化和微小孔径化的要求,给PCB图形设计与图形电镀均匀性提出了新的挑战。

图形电镀是指在PCB制作过程中,将合格的、已完成图形转移工序的电路板,用电镀方法将线路铜和孔壁铜加厚,并以镀锡层作为下一个工序蚀刻的保护层。电镀铜是图形电镀流程中最为关键的一步,镀液的稳定性与镀层均匀性一直是电镀铜互连研究的热点,其镀层性能直接影响产品的可靠性。电感线圈作为电子线路不可或缺的重要部件,采用光刻技术与电镀铜工艺相结合制造的埋嵌电感线圈电路板,有效提高了印制电路板的封装面积,减小板面焊接点,并提高封装的可靠性,从而引起了国内外学者极大的兴趣。电镀铜工艺作为电路板制造的关键技术,其过程作用机理复杂,镀槽形状、镀液传质方式、添加剂组分性质、电场线分布、温度场、应力场、基板材质与工艺流程等都会影响镀层性能[3-5]。图形电镀铜时,主要通过两种方法提高镀层均匀性:一是升级电镀槽构型;二是开发高效的电镀添加剂。目前,一些措施已经被采取以提高铜沉积的均匀性,如使用喷流作为镀液交换方式,增加辅助阳极和象形阳极,采用脉冲电镀方式电镀铜等[6-8]。然而,电镀铜过程受诸多因素影响,采用实验方法研究这诸多因素对电镀铜过程的影响需要设计实验。虽然正交实验方法提供了方便简洁的实验设计方案,但进行哈林槽实验仍然是费时费力的,且周期长、成本高。因此,对于实验过程复杂、成本高的电化学体系,可以采用数值模拟软件完成不同镀槽铜沉积过程的仿真,理解电镀过程的真实机制。目前,一些电化学软件,如Elsyca Plating Manager software, Ansys and Comsol Multiphysics被开发用于研究电镀行为,模拟电镀实验环境,引导电镀铜设备的升级与工艺参数的优化,这已经引起了工业界和学术界极大的关注[9-10]。

PCB图形电镀的主要目标是获得均匀的电镀铜层。为此,一些数值算法如有限元法(FEM)、边界元法(BEM)、有限差分法(FDM)、水平集法(LSM)被用于研究电镀铜过程,尤其是PCB盲孔填铜与通孔电镀铜,分析镀槽内流场与物质浓度分布、沉积层厚度分布等。而采用数值方法分析图形电镀过程机制的研究较少,且局限于一次电流条件下电镀铜的研究。而电感线圈电镀铜时,线圈的形状、镀液对流、电镀工艺参数等共同决定槽内空间电场分布与铜离子浓度分布,镀槽内电场与物质浓度场分布的不均匀(电流丛聚效应)引起线圈各处铜沉积速率不同而形成不均匀的镀层,进一步引起铜线间电阻的差异,引发电感线圈使用故障[3]。因此,镀层均匀性对PCB产品性能有极大的影响,非常有必要采用多物理场耦合方法进行电感线圈电镀铜过程的仿真,理解电镀铜过程作用机制。

为了提高PCB电感线圈电镀铜镀层均匀性,真实反映电镀槽的电镀效果,本文采用多物理场耦合的有限元方法,借助高性能计算机探讨镀件表面电流密度分布与电镀铜层的均匀性,力求反映真实电镀槽的电镀情形,提供线圈电镀铜过程清晰的图形化结果,反映电镀铜过程的真实机制,为PCB图形电镀铜工艺的优化提供理论指导。

1 电镀铜的多场耦合方法

PCB图形电镀工艺流程如图1。

图1 PCB图形电镀工艺流程

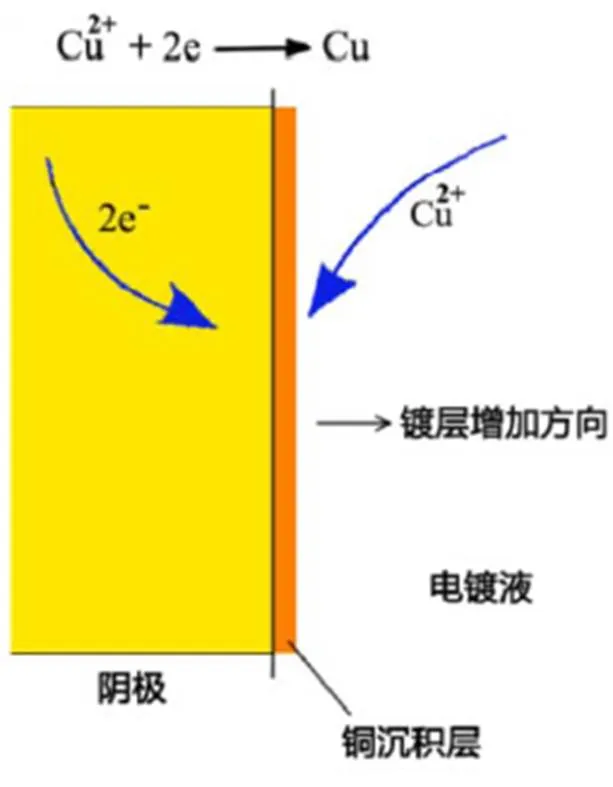

电镀铜是以硫酸铜、硫酸和氯离子作为溶液电解质,PCB作为阴极,与电源负极相连,阳极磷铜板连接电源正极,构成回路。在直流电作用下,阳极金属铜失去电子,被氧化成铜离子并溶于电镀液。在电场作用下,溶液中的铜离子不断向阴极迁移,并得到电子而还原为金属铜,形成不断变化的铜镀层,作用机理如图2。电镀铜是一个复杂的电化学过程,涉及电场、流体力学、化学反应、物质传递等多个物理场,这些物理场通过交互作用而相互影响,制约铜镀层的沉积[12]。数学上,这些物理场都可以用微分方程或偏微分方程来描述,因此,电镀铜层厚度可以借助计算机软件进行数值模拟。多物理场耦合以有限元法为基础,通过求解偏微分方程组来实现电镀铜过程的仿真,用数学方法求解电镀铜过程。

图2 电镀铜原理图

电感线圈电镀铜数值模拟模型如图3。图形电镀电镀铜镀液体系由200 g/L CuSO4·5H2O、50 g/L H2SO4、60 mg/L Cl−、1 mg/L SPS、200 mg/L EO/PO与6 mg/L PEOPI组成。数值模拟假设:电镀液传输特性(如离子扩散系数、密度、黏度)在电镀体系中稳定;镀液温度稳定在25℃,不考虑传热。

图3 电感线圈电镀铜几何模型

电镀铜镀层厚度的变化基于电化学中很重要的法拉第定律来描述,阴极沉积铜的物质的量与电流密度成正比,镀层厚度可表示为:

式中:为镀铜层厚度;为电镀时间;为电流密度;Cu为铜的摩尔质量;Cu为铜密度;为法拉第常数。

法拉第定律表明,金属铜在PCB表面各个部位的沉积量取决于电流在PCB表面上的分布状况。因此,一切能影响电流在阴极表面分布的因素,都能影响铜层在PCB表面的分布。

电镀液中各种离子的流量满足Nernst-Planck方程:

因此,阴极电流密度可表示为:

(3)

式中:c为离子的浓度;D为离子的扩散系数;z为离子电荷数;m, i为离子的迁移率;l为电势;为迁移率均值。

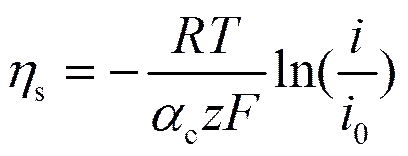

电极反应动力学用浓度依赖动力学Butler-Volmer(BV)方程来描述。当过电势s≤25 mV时采用线性近似简化方程;当s≥120 mV时采用Tafel近似描述BV方程,见式(4)。

式中:c、与0分别为阴极转移系数、转移电子数与交换电流密度。

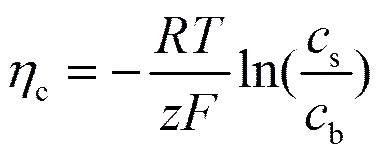

浓度过电位由铜离子的表面浓度与体浓度决定,表示为式(5)。

式中:b与s分别是铜离子的体浓度与表面浓度。

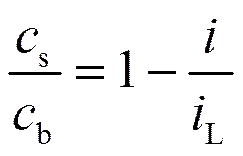

电极表面铜离子的消耗与极限电流密度L有关,见式(6)。

极限电流与扩散层厚度有关,表示为:

(7)

式中:为铜离子扩散系数;为扩散层厚度。

电镀铜数值模拟为了提高解的收敛性,设置阳极电势为0,并采用移动网格追踪铜沉积边界。边界条件为式(8)~(10)。

(阴极边界) (9)

(阳极边界) (10)

PCB电感线圈电镀铜用(error,误差)与COV(Coefficient of variance,标准偏差)评价镀件表面电流密度与镀层分布均匀性,定义为式(11)与(12)。与COV值越小表明镀层越均匀。

(12)

(13)

式中:max与min分别为最大电流密度与最小电流密度;为平均电流密度。

数值模拟参数列举于表1。为了准确计算电流密度与镀层厚度分布,在阴极附近构建边界层网格,第一层网格的尺寸设定为0.5 μm,以评价从几个到几十个微米的扩散层,边界层外部构建自由四面体网格,图形电镀模型划分的网格结构如图4所示。为了提高数值收敛性,采用迭代求解并设置几何自适应条件,以调整铜沉积过程中计算域的网格尺寸。

表1 电感线圈电镀铜数值模拟参数

Tab.1 Parameters of numerical simulation of inductor coil electroplating copper

图4 电感线圈电镀铜数值模拟有限元网格

2 结果与讨论

2.1 镀槽内铜离子浓度分布

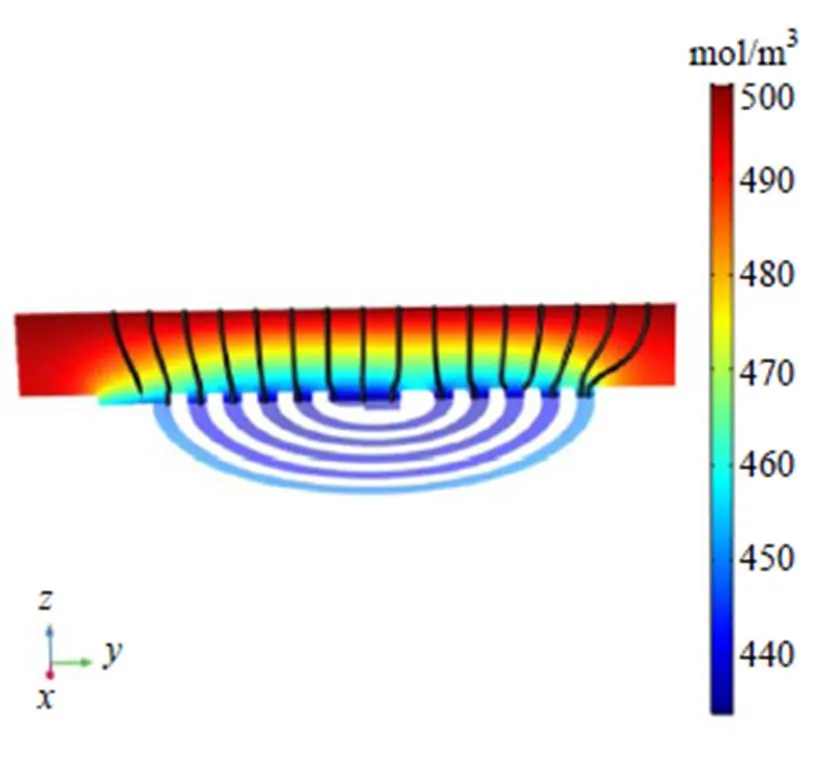

电镀铜时体系需要提供电能,使阳极能解离出铜离子,同时镀液中的铜离子还原在阴极,电镀铜层受电镀槽几何因素与电化学因素的影响[13]。电极表面附近的液层主要靠扩散作用来实现传质过程,形成稳定的铜离子浓度分布来决定铜的沉积速率,影响镀层厚度分布。电镀600 s槽内线圈表面与中部截面扩散层内铜离子浓度分布如图5所示。从图中可以看出,电感线圈表面扩散层内产生了铜离子浓度梯度,越靠近电极表面,铜离子在电极表面沉积使浓度减小。电感线圈从内到外,电场线分布的不均匀影响铜离子在镀液中的迁移,形成了中间扩散层厚度大,边缘扩散层厚度较小的现状,引起电极表面铜离子不同的扩散浓度,越靠近线圈中部,扩散层厚度越大,电极表面铜离子浓度越小,形成不同厚度的镀层。

图5 600 s镀槽内铜离子浓度分布

2.2 线圈表面电流密度分布

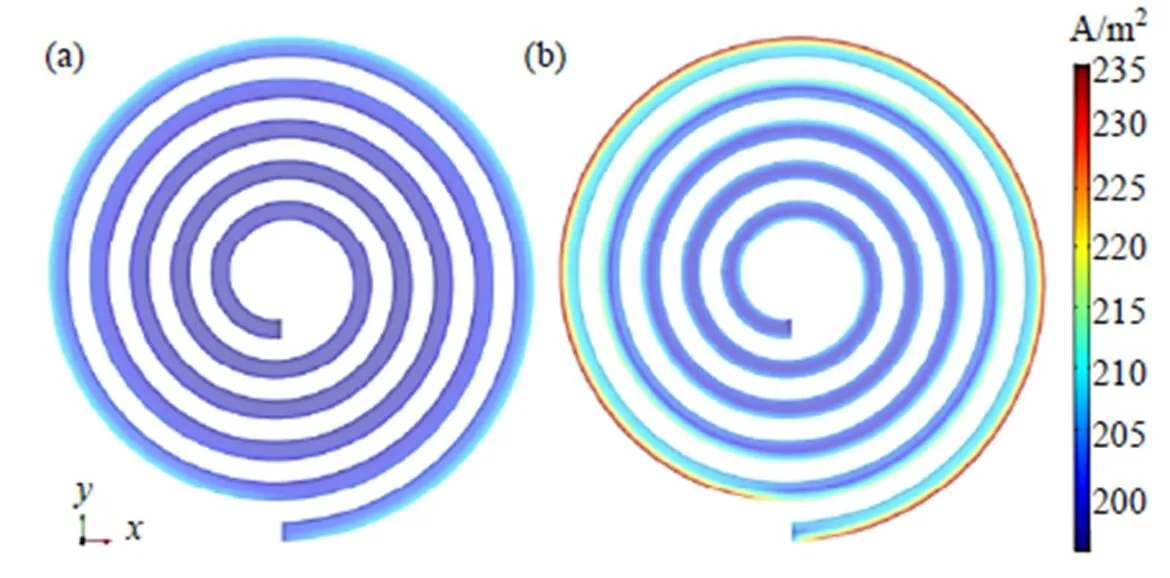

影响电流在阴极表面分布的因素很多,可以归纳为两个方面:一是几何因素;二是电化学因素、离子的扩散速度等因素[14]。电感线圈电镀铜时,电极附近发生电化学反应,增加了电镀液的电阻,即引起极化,形成电极表面二次电流分布。电感线圈在电镀600 s和1200 s电极表面电流密度分布如图6所示。镀槽内电场线分布的不均匀形成了线圈表面不均匀的电流密度分布。越靠近线圈外层边缘,电流密度越大,源于更为集中的电场线。线圈边缘上的离子流来自于边线方向和线圈的垂直方向,形成更为密集的电场线分布,边缘处电流密度值大于线圈中心处电流密度[15]。随着电镀的进行,阴极表面镀层的不均匀分布使电镀槽内形成了更为不均匀的电场,电极表面电流密度分布不均匀程度变得明显,线圈外层边缘处电流密度大于中心处电流密度。1200 s线圈表面镀层厚度分布如图7所示。

电镀时间(a)为600 s;(b)为1200 s

2.3 线圈表面镀层厚度分布

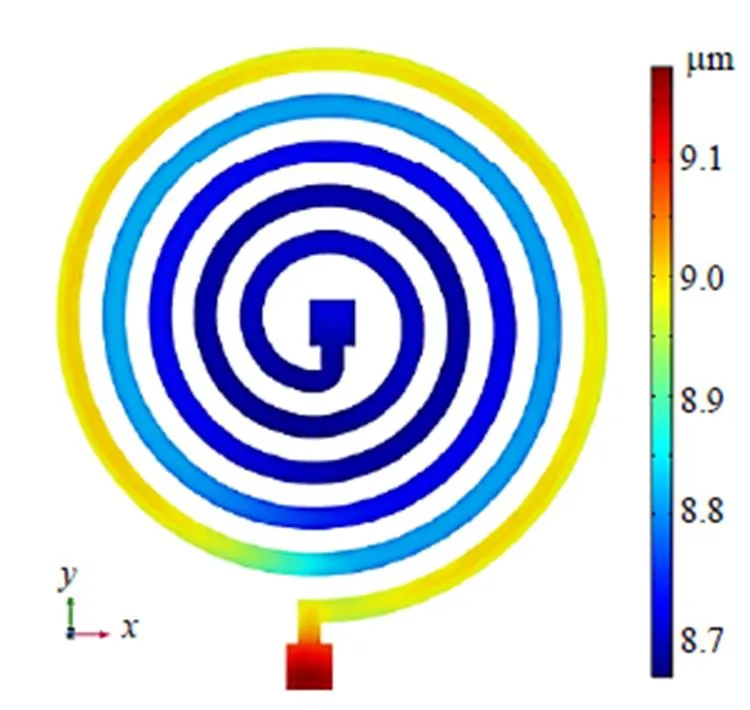

图7中可以看出,电镀进行到1200 s,线圈表面由于不均匀的电流密度分布而形成从内到外不均匀的镀层,外端子镀层最厚,达到9.21 μm。造成镀层厚度不均匀的主要原因是阴极表面图形分布状况及其工件在电镀槽中状况引起的电流分布不均匀。电镀铜时,需要提供电能,使得镀液中的铜离子(Cu2+)能还原在阴极,阳极能解离出铜离子,电镀能量高的地方具有较高的电镀速率,即形成高电流密度区;电镀能量低的区域其电镀速率较低,形成低电流密度区,线圈表面电流密度分布的不均匀形成了表面从内到外不均匀的镀层。若要改变镀层分布不均匀状况,可以改变电镀设备和设计理念,如增加阴阳极距离、使用绝缘屏蔽物改变等电位平面、使用象形阳极、辅助阳极等措施改变低电流密度区域的电流分布状况[16-18]。当使用象形阳极时,电镀1200 s线圈表面镀层分布如图8所示。

图7 电感线圈1200 s镀层厚度分布

2.4 图形电镀镀层均匀性的改善

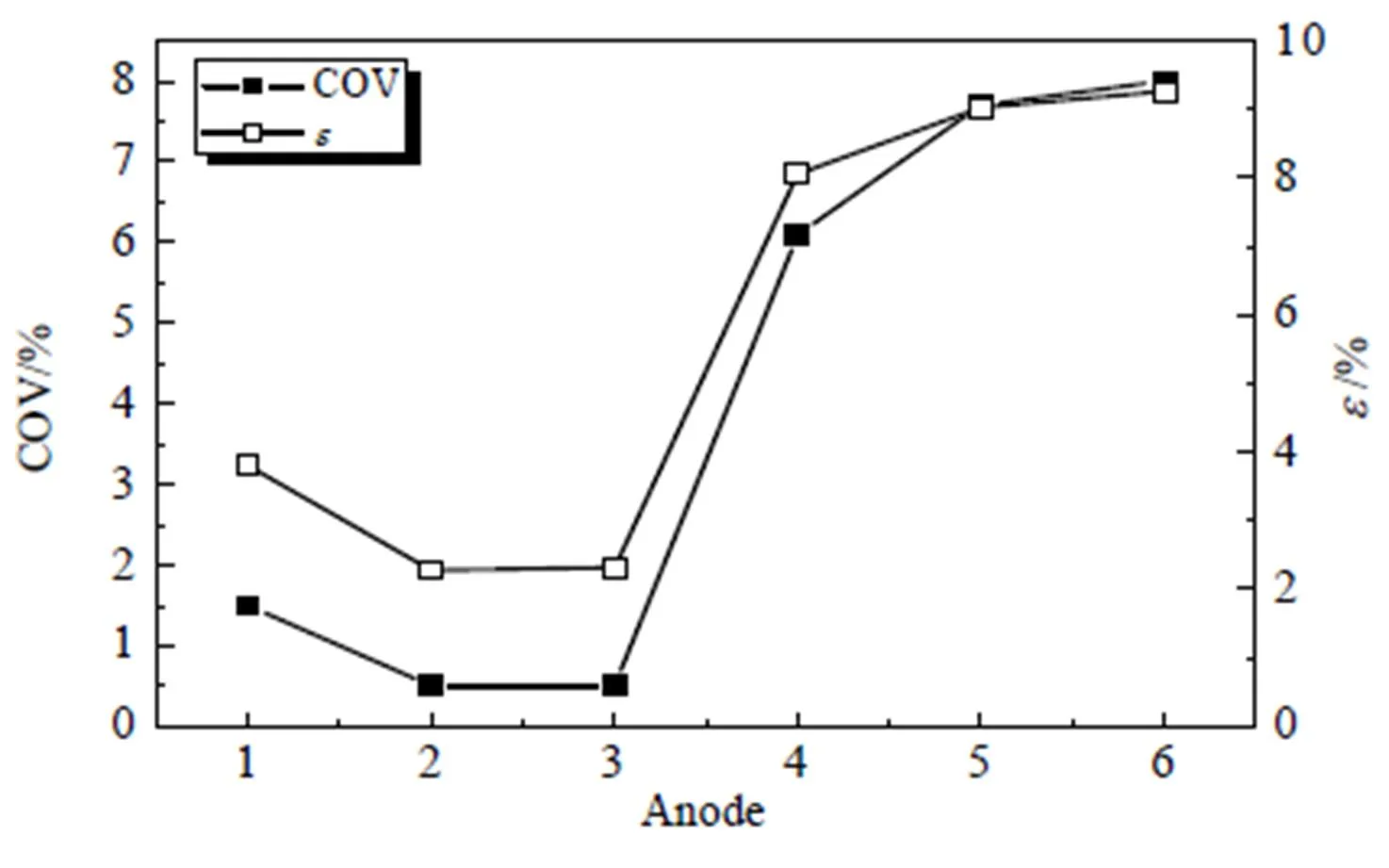

线圈在电镀铜过程中,由于线圈上下的镀液空间存在电力线的传导而产生了边缘效应,形成了线圈边缘电流密度高于中部区域,使得镀层不均匀分布。因此,电镀铜过程需要采取一些措施控制自由空间的电场线分布,如调整阴阳极距离、隔离自由空间、增加辅助挡板、象形阴极等。图8模拟结果表明,阳极采用象形阳极后,镀层均匀性有明显的提高,外层线圈与内层线圈镀层分布更加均匀。对镀件表面铜层厚度进行分析,阳极为铜板时,铜层厚度最大值为9.18 μm,最小值8.65 μm,极差为0.53 μm。阳极为象形阳极时,铜层厚度最大值为8.93 μm,最小值8.72 μm,极差为0.21 μm。镀层厚度结果显示,象形阳极进行线圈电镀铜,铜层极差降低,采用象形阳极进行电镀铜能提高镀层均匀性。为了分析镀槽几何因素对铜层的影响,线圈镀层厚度统计、镀层均匀性与COV随阴阳极距离分布如图9和图10所示。

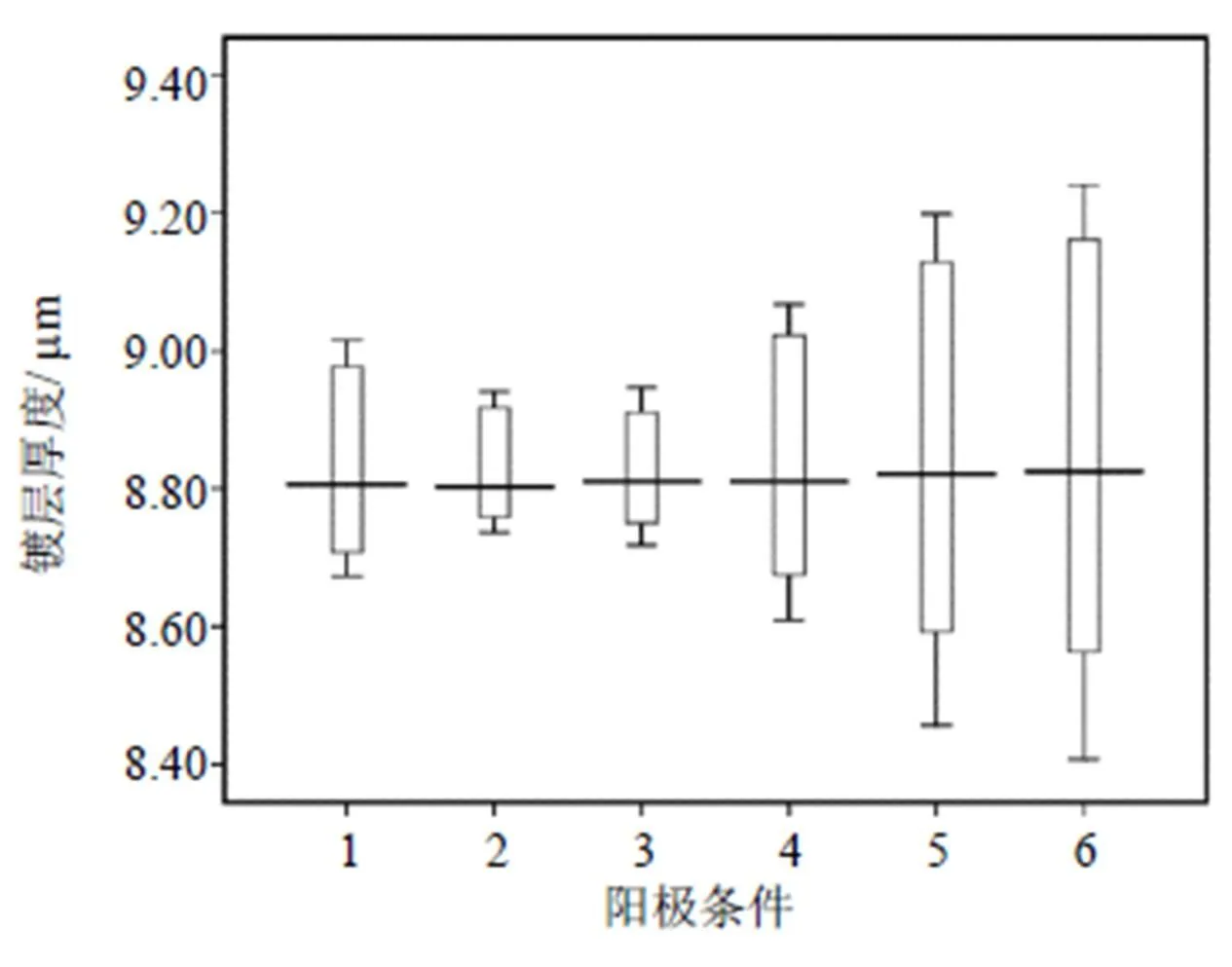

(a) 阳极为铜板;(b) 阳极为象形铜环

镀层厚度统计分布为图9,图10为与COV随阳极条件的变化,图9表明,线圈表面镀层厚度随阳极形状与阴阳极相对位置的变化而有所改变。当阴阳极距离较小时,即20~30 cm,线圈表面镀层厚度分布均匀,极值较小,约为0.21 μm。采用象形阳极有助于提高线圈表面镀层的均匀分布,表现为图10中与COV值减小,COV值为0.5%。然而采用象形阳极电镀铜时,随着阴阳极距离的增加,线圈表面镀层最大值增加,最小值更小。这源于镀液中自由空间的增加,加大了空间电场线的自由导电空间,形成了空间更复杂的电场分布,引起外层更大的电流密度形成较厚的镀层[8]。阴阳极距离越大,镀层极值越大,与COV值增大,镀层分布不均匀。当阴阳极距离为60 cm时,镀层最大值为9.25 μm,最小值为8.4 μm,极值为0.85 μm,COV达到9.5%。COV虽然满足PCB行业<10%的要求,但镀层不均匀性引起产品可靠性问题。生产线电镀铜时,镀槽中阴阳极距离是确定的,此时采用图形电镀时铜层均匀性尚需要采取其他措施,如增加绝缘挡板。绝缘挡板可以调整电镀槽中电场线的分布状况。当镀槽中阴阳极尺寸较小时,可以通过增加绝缘挡板将导电自由空间隔开,约束边缘电场线来调整电场线的空间分布,提高电场线分布的均匀性,从而提高镀层的均匀性。

1:阳极为平板;2~6阳极为象形阳极;阴阳极距离:1和2为20 cm;3为30 cm;4为50 cm;6为60 cm

图10 ε与COV随阳极条件的变化

电感线圈电镀铜镀槽中阴阳极距离为50 cm,将带圆孔的绝缘挡板放置于阴阳极之间,1200 s线圈表面镀层厚度统计分布如图11所示。镀层分布表明,线圈表面镀层均匀分布,最外层镀层较厚,大约为8.89 μm,线圈最内层镀层厚度为8.75 μm,极差为0.14 μm。镀层分布为1.6%,COV值为0.4%。与无绝缘挡板时的镀层分布相比,电沉积铜层的均匀性有很大提高。绝缘挡板分开了导电自由空间并改变了槽内空间电场分布,通过限制边缘处的电场调整镀槽空间电场使电极表面电流与镀层分布均匀,达到电镀铜均匀电镀层之目标。

图11 加入绝缘挡板后,1200 s线圈表面镀层厚度统计分布

电镀铜是一个复杂的电化学体系,实际电镀生产过程中,几何因素和电化学因素应看作一个不可分割的统一整体来考虑和研究。首先要设计合适的电镀槽,通过调整阴阳极位置,设计象形阳极,增加绝缘屏蔽物,增加辅助阳极或辅助阴极等,使一次电流分布尽量均匀;第二,提高电镀液的分散能力,如使用脉冲电镀、通过搅拌加快镀液交换等,改善二次电流分布的均匀性[19]。搅拌会加速电镀液的对流,使阴极附近消耗了的铜离子得到及时补充,并降低阴极的浓差极化,提高允许的阴极电流密度上限值,使在较高的电流密度和较高的电流效率下得到细致紧密的镀层,进一步提高镀层均匀性。

3 结论

线圈图形电镀铜作为印制电路板生产中一道重要的工序,电镀质量的好坏直接影响着印制电路板的外观与性能。本文采用多物理场耦合方法讨论了PCB线圈电镀铜过程,分析了不同阳极条件下线圈表面的电流密度与镀层分布状况。结果表明,阳极形状、阴阳极之间的距离会影响电流密度与镀层厚度分布。象形阳极的使用有利于提高镀层均匀性,随着阴阳极距离的增加,镀液中更大的自由导电空间引起电流密度与镀层的不均匀,需要采用绝缘挡板改善电场线分布状况来提高镀层均匀性,COV减小为0.4%。这一结论和实际电镀是一致的。PCB线圈电镀铜数值模拟结果表明,多物理场耦合方法能够较准确地对电镀体系进行预测和推理。此方法用于分析龙门电镀线、水平电镀线与垂直连续电镀线的电镀铜过程,有助于优化电镀铜工艺,帮助PCB生产商提高生产效率,减少不良率。多物理场耦合方法对于指导电镀铜工艺与镀件镀层分布的均匀性具有一定的借鉴意义。

[1] CHEN Y, HE W, CHEN X, et al. Plating uniformity of bottom-up copper pillars and patterns for IC substrates with additive-assisted electrodeposition [J]. Electrochim Acta, 2014, 120: 293-301.

[2] GAMBINO J P, ADDERLY S A, KNICKERBOCKER J U. An overview of through-silicon-via technology and manufacturing challenges [J]. Microelectron Eng, 2015, 135: 73-106.

[3] TAO Z, HE W, WANG S, et al. Synergistic effect of different additives on microvia filling in an acidic copper plating solution [J]. J Electrochem Soc, 2016, 163(8): D379-D384.

[4] KONDO K, KOUTA H, YOKOI M, et al. Behavior of cuprous intermediate in copper damascene electrodeposition [J]. ECS Electrochem Lett, 2014, 3(4): D3-D5.

[5] KIM H C, CHOE S, CHO J Y, et al. Bottom-up filling of through silicon vias using galvanostatic Cu electrodeposition with the modified organic additives [J]. J Electrochem Soc, 2015, 162(3): D109-D114.

[6] PARK C W, PARK K Y. An effect of dummy cathode on thickness uniformity in electroforming process [J]. Res Phys, 2014, 4: 107-112.

[7] HUANG D, SHEN L, CHEN J, et al. The influence of cathode surface velocity on friction aided jet electrodeposition [J]. Trans Indian Inst Met, 2014, 3(67): 351-357.

[8] RAFFELSTETTER P, MOLLAY B, VAN DEN B B, et al. Modeling strategy for predicting current density distributions on PCBs and other complex patterned substrates [J]. J Electrochem Soc, 2009, 156(2): D51-D57.

[9] COLLI A N, BISANG J M. Validation of theory with experiments for local mass transfer at parallel plate electrodes under laminar flow conditions [J]. J Electrochem Soc, 2013, 160(1): E5-E11.

[10] POHIORATA A, TENNO R. Implementing surfactant mass balance in 2D FEM-ALE models [J]. Eng Comput, 2011, 27(2): 165-175.

[11] JIA Z, ZHANG S T, LIU D, et al. The improvement of PCB’s electroplating uniformity [J]. Appl Mech Mater, 2012, 236: 158-162.

[12] JI L, WANG S X, WANG C, et al. Improved uniformity of conformal through-hole copper electrodeposition by revision of plating cell configuration [J]. J Electrochem Soc, 2015, 162(12): D575-D583.

[13] ZHANG Y, DING G, CHENG P, et al. Numerical simulation and experimental verification of additive distribution in through-silicon via during copper filling process [J]. J Electrochem Soc, 2015, 162(1): D62-D67.

[14] ZHU Y, MA S, SUN X, et al. Numerical modeling and experimental verification of through silicon via (TSV) filling in presence of additives [J]. Microelectron Eng, 2014, 117: 8-12.

[15] JI L, WANG C. Multi-physics coupling aid uniformity improvement in pattern plating [J]. Circuit World, 2016, 42(2): 69-76.

[16] PARK C W, PARK K Y. An effect of dummy cathode on thickness uniformity in electroforming process [J]. Res Phys, 2014, 4: 107-112.

[17] HERNANDEZ P, SOCAS A, BENITEZ A, et al. Computer aided electroforming. Elecform 3D™ [J]. Proc Eng, 2013, 63: 532-539.

[18] WU Q B, GREEN T A, ROY S. Electrodeposition of microstructures using a patterned anode [J]. Electrochem Commun, 2011, 13(11): 1229-1232.

[19] ZHU Q S, TODA A, ZHANG Y, et al. Void-free copper filling of through silicon via by periodic pulse reverse electrodeposition [J]. J Electrochem Soc, 2014, 161(5): D263-D268.

(编辑:陈渝生)

Copper electroplating for inductance coil with multi-physics coupling

SU Shidong, JI Linxian

(Department of Physics and Electronic Engineering, Yuncheng University, Yuncheng 044000, Shanxi Province, China)

A model for copper electroplating on inductance coil was established based on multi-physics coupling technology. The characteristics of Cu2+concentration distribution, current density of coil surface and thickness of copper electrodeposition were obtained by finite element analysis. The effects of pictographic anode and distance between anode and cathode on coating thickness distribution were discussed. The numerical simulation results show that it is helpful to improve the uniformity of copper electrodeposition on coil surface by adding pictographic anode and insulating baffle. When the distance between cathode and anode is small, the range of plating thickness is 0.21 μm, the value of COV (Coefficient of Variance) is 0.5% under the condition of electroplating copper with pictographic anode. With the increase of the distance between the anode and cathode, coating thickness increased to 9.5%, and an insulating baffle was needed to improve the uniformity of coating. Then, the range of plating thickness is 0.14 μm, the value of COV is 0.4%.

printed circuit; inductance coil; copper electroplating; multi-physics coupling; pictographic anode; FEM

10.14106/j.cnki.1001-2028.2017.10.008

O441.4

A

1001-2028(2017)10-0046-07

2017-06-30

苏世栋

运城学院院级项目资助(No. CY-2016005)

苏世栋(1962-),男,山西运城人,副教授,从事电子元器件制作等研究,E-mail: shidongsu123@126.com 。

2017-09-27 10:57

网络出版地址:http://kns.cnki.net/kcms/detail/51.1241.TN.20170927.1057.008.html