采样保持电路中全差分增益提高放大器设计

2017-09-21钱黎明魏敬和

钱黎明,魏敬和

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

采样保持电路中全差分增益提高放大器设计

钱黎明,魏敬和

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

介绍了一种全差分增益增强CMOS运算放大器的设计和实现。该放大器用于12位20 MHz采样频率的流水线模/数转换器(A/D)的采样保持电路。为了实现大的输入共模范围,采用折叠式共源共栅放大器。主放大器采用开关电容共模反馈电路,辅助放大器则采用简单的连续时间共模反馈电路。该放大器采用CMOS 0.5 μm工艺,电源电压为3.3 V。Cadence Spectre仿真结果显示,在负载为6 pF的情况下,其增益为99 dB,单位增益带宽为318 MHz,相位裕度为53°。

增益提高;共模反馈;采样保持电路

1 引言

高清图像、视频处理芯片的快速发展对A/D的速度和精度要求越来越高,这直接转化为对运算放大器的要求。A/D的采样速度取决于运算放大器的建立时间(Settling Time),建立时间取决于摆率(Slew Rate,SR)和运放的增益带宽积(Gain Bandwidth,GBW)。A/D的采样精度要求运算放大器具有高直流增益。而随着工艺尺寸和电源电压的不断降低,普通运算放大器大概能实现50~60 dB的直流增益。而一些高精度A/D要求放大器的直流增益为90 dB以上,两级放大器虽然能实现较高的增益,但其功耗太大,并且速度也很难满足要求。增益提高运算放大器是将共源共栅电流源中通过增加反馈放大器而提高输出阻抗的思想应用到运放中。这使得即使亚微米工艺制备的运放其增益也可以达到90 dB以上。

2 增益提高运算放大器结构

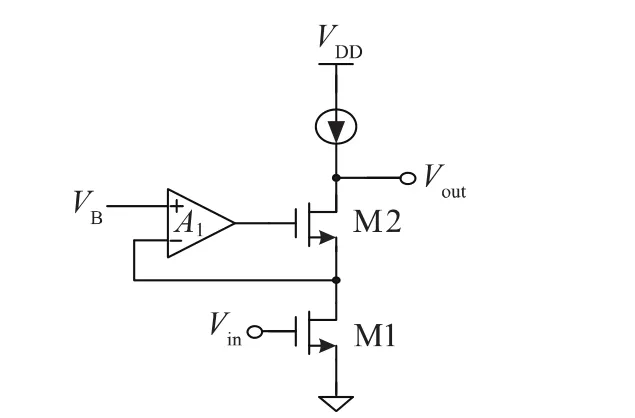

增益提高运算放大器如图1所示,该结构的运放提高增益的思想是在共源共栅电流源中增加反馈放大器而提高输出阻抗,从而大大增加了增益,在深亚微米工艺制程中其增益可以达到90 dB以上。加入增益提高辅助运放A1后,主运放的单位增益带宽和输出电压摆幅都没有减小,这是增益提高运放的另一个突出优点。由于增益提高型结构的辅助运放会引入零极偶对子(pole-zero doublet),使运放建立时间有所增加,但速度仍然很高[1~2]。

图1 增益提高共源共栅放大器

提高增益的基本思想是采用负反馈控制稳定输入管M1的漏源电压,减小输出电压变化对M1管漏端电压的影响,使流过M1管的电流更加恒定,从而产生更高的输出阻抗。若忽略衬底偏置效应的影响,辅助运放使共源共栅放大器的输出电阻增加为:

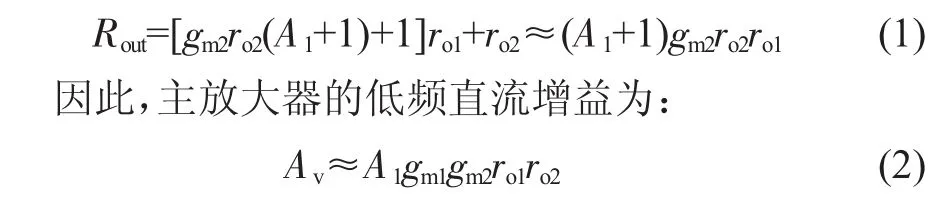

可以看出输出阻抗增加了A1倍,这使得增益提高了A1倍,将这个增益提高型的共源共栅电流源应用到运放中,图2和图3分别为折叠式增益提高型运放和套筒式增益提高型运放,它们的增益可以达到90 dB左右。增益提高型结构可以提高运放的增益,而不改变运放的单位增益带宽和输出电压摆幅。增益提高型结构的辅助运放Aap和Aan会引入零极点对和重极点,使得运放的速度有所下降,但速度仍然较高。

图2 折叠式增益提高型运放

图3 套筒式增益提高型运放

3 增益提高运算放大器设计

运算放大器最高的应用要求是满足12位20 MHz信号的采样保持电路。因此对运放的基本要求是高速高增益,并且其功耗和噪声应尽可能小,考虑到电容翻转式的采样保持电路输入电压为相对固定的1.65V,所以采用折叠式增益提高型运放结构,如图2所示。辅助运放因其输入输出共模电压变化范围的需要,因而只能采用折叠式共源共栅结构。系统运放的增益达到(gmro)4量级,采用0.5 μm工艺比较容易实现90 dB以上增益。因此,运放设计时从频率与速度特性考虑,并通过仿真检验增益与输出电压摆幅是否同时满足设计要求。

3.1 主运算放大器设计

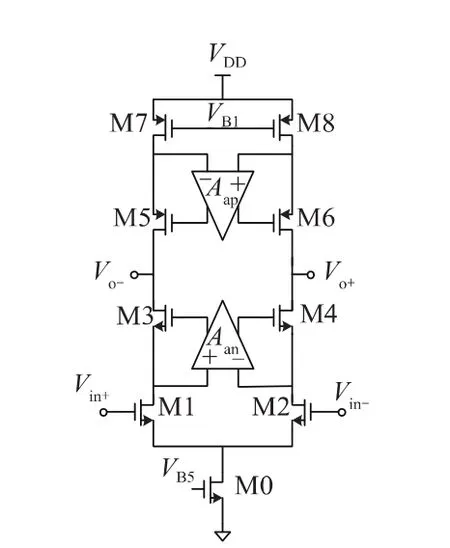

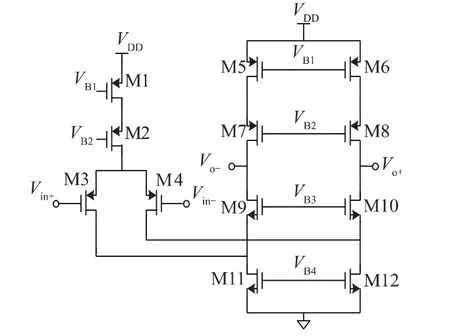

主运放为折叠式运算放大器,如图4所示。

图4 主运放电路图

该主运放单端小信号电压增益为|AV|=GmRout,其中:

假设Cout为输出端节点的总电容,CL1为M7源级的总电容,CL2为M9源级的总电容,则主极点频率p1为:

主运放为折叠式结构,晶体管M1的漏电流必须小于或等于M11的漏电流,否则会使尾电流源M1进入线性区[3],影响建立速度,本设计中取M1的漏电流等于M11的漏电流。为了使运放工作速度最快,所有MOS管的L取允许的最小值(L=0.55 μm)。

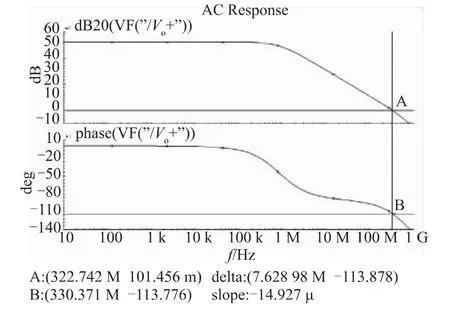

因此,结合上述原理,基于系统对主运放的性能要求,通过理论计算并结合仿真调整,在主运放输出端加6 pF负载电容(CL=CS+CS-MDAC=1.5+4.5=6 pF),利用Cadence平台下的Spectre环境对其进行小信号ac分析,得到运放的开环增益为52 dB,单位增益带宽为330 MHz,相位裕度为76°。

图5 主运放开环幅频与相频仿真波形

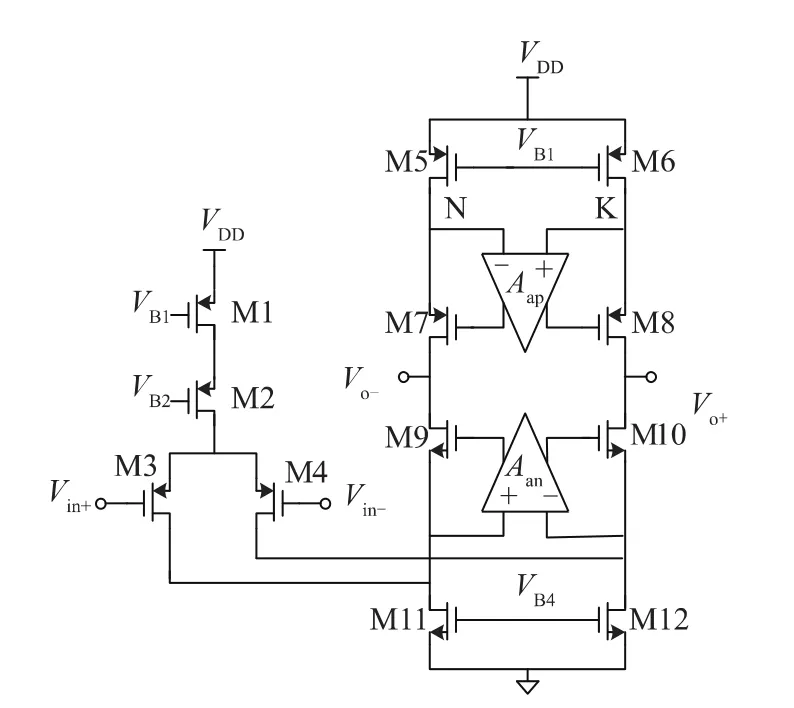

3.2 辅助运算放大器设计

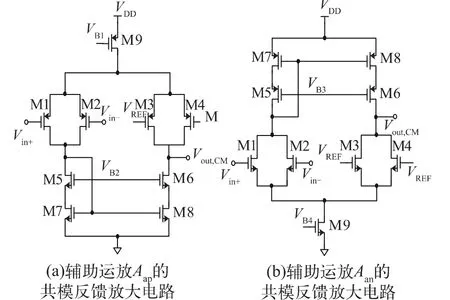

由上文分析可知,运放的直流增益必须大于90dB,考虑到给予一定的余量,直流增益必须大于96 dB,因为整个运放的增益等于主运放与辅助运放直流增益的乘积,而主运放增益为52 dB,所以辅助运放的直流增益必须大于44 dB,这里辅助运放也选用共源共栅结构,辅助运放Aap和Aan如图6所示。

辅助运放在信号路径上,为了不损失主运放的单位增益带宽,对此运放的单位增益带宽必须满足下面的表达式[4]:

f为反馈系数,fu-main为主运放单位增益带宽,fu-a为辅助运放的单位增益带宽,p2为主运放的第二个极点。

图6 辅助运放

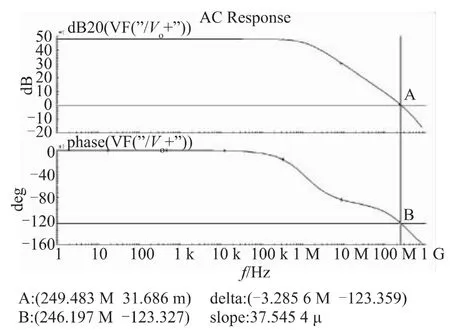

因此,结合上述原理,通过理论计算并结合仿真调整,在辅助运放输出端加1 pF负载电容,利用Cadence平台下的Spectre环境对其进行小信号ac分析,得到辅助运放Aap的开环增益为48 dB,单位增益带宽为246 MHz,相位裕度为57°;辅助运放Aan的开环增益为49 dB,单位增益带宽为254 MHz,相位裕度为64°,因此满足系统的要求。

图7 辅助运放Aap开环幅频与相频仿真波形

3.3 共模反馈电路设计

全差分结构可以消除二次谐波并降低很多非线性效应,而差分运放输出阻抗非常高,这使得输出共模电压难以稳定。因此,为了确保运放的正常工作,需要加入负反馈电路来稳定输出共模电压。本设计中的主运放采用开关电容共模反馈电路结构,如图9所示;辅助运放采用连续时间共模反馈电路结构,如图10所示。

4 增益提高运算放大器仿真

运放的总体结构为折叠式增益增强型,如图2所示。将已设计的主运放和辅助运放Aap和Aan组合起来,即得到总体运算放大器。

图8 辅助运放Aan开环幅频与相频仿真波形

图9 主运放开关电容共模反馈电路

图10 辅助运放连续时间共模反馈电路

在总体运算放大器输出端加6 pF负载电容,利用Cadence平台下的Spectre环境对其进行小信号ac分析,得到总体运放的开环幅频与相频仿真波形,如图11所示。仿真得到运放的开环增益为99 dB,单位增益带宽为318 MHz,相位裕度为53°。因此,整个运算放大器符合设计要求。

图11 增益提高运放开环幅频与相频仿真波形

5 结论

本文分析和设计了一个采用增益提高技术的折叠式共源共栅全差分放大器。它具有高直流增益、较大输入范围、输出摆幅和较高的增益带宽。主放大器和辅助放大器采用不同的共模反馈电路来优化设计和降低功耗。Cadence Spectre仿真结果显示,在负载为6pF的情况下,其增益为99dB,单位增益带宽为318MHz,相位裕度为53°,该运算放大器完全满足12位20 MHz A/D采样保持电路的设计要求。

[1]Denis Flandre,Alberto Viviani,Jean-Paul Eggermont,et al. Improved Synthesis of Gain-Boosted Regulated-Cascode CMOSStagesUsingSymbolicAnalysisandgm/ID Methodology[J].IEEE J Solid-State Circuits,1997,32(7): 1006-1011.

[2]Mrinal Das.Improved Design Criteria of Gain-Boosted CMOS OTA With High-Speed Optimizations[J].IEEE Trans on Circuits and Systems II,2002,49(3):204-207.

[3]Ahmed I,Johns D A.A 50-MS/s(35 mW)to 1-kS/s(15 μW) power scaleable 10-bit pipelined ADC using rapid power-on opamps and minimal bias current variation[J].IEEE JSSC, 2005,40(12):2446-2455.

[4]Andersen T N,Briskemyr A,Telsto F,et al.A 97 mW 110 MS/s 12b pipeline ADC implemented in 0.18/spl mu/m digital CMOS[J].Design,Automation and Test in Europe, 2005,3:219-222.

[5]KUNIHIKO I,HIROFUMI M,MASAYA U,et al.A 14-bit Digitally Self-Calibrated Pipelined ADC With Adaptive Bias Optimization for Arbitrary Speeds Up to 40 MS/s[J].IEEE Journal of Solid-State Circuits,2006,4(41):883-890.

Design of Fully Differential Gain Boosted OPAMP Dedicated to Sample and Hold Circuit

QIAN Liming,WEI Jinhe

(China Electronic Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

A kind of gain boosted fully differential CMOS operational amplifier is introduced in this paper.It is used for the Sample and Hold(S&H)circuits of a 12 bit 20 MHz pipeline A/D convertor.The main amplifier is folded cascode to obtain a large range of input common mode voltage.The switched capacitor Common Mode Feedbackcircuit(CMFB)isadoptedinmainamplifier,whilesimplecontinuoustimeCMFBisimplementedinthe auxiliaryamplifier to reduce power consumption and simplifythe circuit.The amplifier is designed with CMOS 0.5μmprocessunder3.3Vpowersupply.CadenceSpectresimulationresultshowsthattheamplifierhasachived theDCgainof 99dB,thegainbandwidthof 318MHzandthephasemarginof53degreeattheloadof6pF.

gainboosted;PLL;CMFB

TN752

:A

:1681-1070(2017)09-0019-04

2017-6-21

钱黎明(1981—),男,安徽芜湖人,硕士,现在中国电子科技集团公司第五十八研究所从事系统芯片SoC设计与研发工作;

魏敬和(1971—),男,安徽安庆人,博士,现在中国电子科技集团公司第五十八研究所从事系统芯片SoC设计与研发工作。