万兆以太网与RapidIO网络的互连与传输

2017-09-12柴小丽顾燕飞

左 颜,柴小丽,顾燕飞

(华东计算技术研究所, 上海 201801)

万兆以太网与RapidIO网络的互连与传输

左 颜,柴小丽,顾燕飞

(华东计算技术研究所, 上海 201801)

伴随着各种高性能计算系统的不断发展,所采用的数据传输方式对系统整体性能的影响越来越重要。RapidIO是基于数据包交换的互连架构体系,是能满足各种高性能嵌入式系统需求的一种开放式互连技术标准。介绍了RapidIO的一些基本概念知识以及万兆以太网的发展现状,分析了RapidIO网络和万兆以太网的数据传输过程。介于有些实时数据需要在万兆以太网和RapidIO网络之间进行传输,提出了一种基于万兆以太网和RapidIO网络间数据转换的网关设计。在硬件平台中,充分使用资源设计并实现了10GE-RapidIO协议转换的网关嵌入式软件系统。采用IP-over-RapidIO技术,可以将以太网数据包封装进RapidIO数据包中实现以太网数据包在RapidIO网络中传输,即实现万兆以太网和RapidIO网络的互连互通。这种方法能使用户专注于上层应用开发,不必过多关注于系统底层复杂的强实时RapidIO技术细节。最终通过搭建实验平台对该网关设计的实用性进行了验证。

RapidIO;万兆以太网;IP-over-RapidIO;网关

RapidIO是基于数据包交换的互连体系结构,同时也是一种互连方式,具有卓越的性能以及简易的结构,能满足各种高性能的嵌入式系统的要求。它具有很多优越性,比如延时低、可靠性强、带宽高和效率高等,可以为高性能嵌入式系统内部互连提供优秀的解决方案。RapidIO协议分为3个层:逻辑层、物理层和传输层[1]。逻辑层是最高层,所有的协议等都由逻辑层决定;地址空间和路由信息则由传输层决定;物理层位于最底层,事物传输方式以及接口信息等由其决定[2]。

以太网传输基于TCP/IP协议,在很多领域都有普遍的应用,而万兆以太网传输方式更是引领于各种应用,成为一种主流趋势。万兆以太网络采用全双工与光纤的技术,其带宽和处理能力更胜一筹,不受传输距离影响,保持了以太网的兼容性,使用方便且升级容易,普及率非常高。万兆以太网技术相比普通以太网技术功能更新、更强大,这样使得QoS得到了很大的提高[3]。

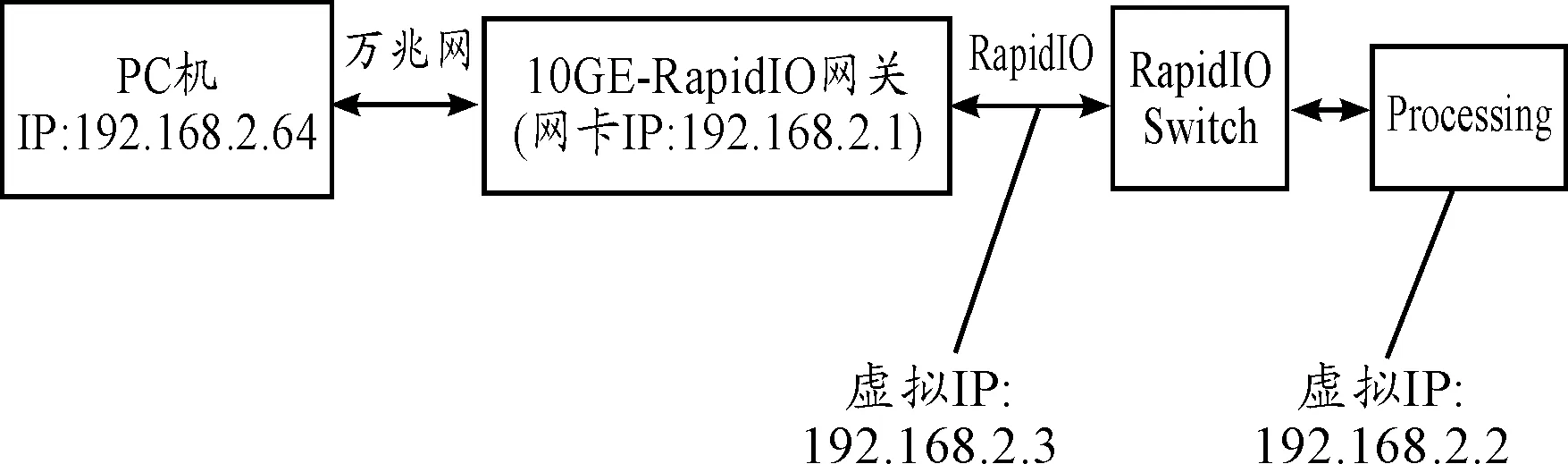

本文主要研究万兆以太网和RapidIO网络间实时数据转换的网关设计。实时数据可以在万兆以太网和RapidIO网络间高效方便地传输通信。设计的重点就是可以构造出将RapidIO数据包和TCP/IP数据包互为转换的网关。该网关即为将万兆以太网和RapidIO网络连接起来。如图1网关架构所示,分布式计算系统内部的处理节点间由RapidIO网络互连,其中的每一个处理节点看做是RapidIO网络中的的一个终端节点,RapidIO交换模块用于完成交换功能[4]。分布式计算系统与10GE-RapidIO网关之间由RapidIO网络互连,网关的另一端同时与万兆以太网组建的IP网络互连。IP网络和RapidIO网络的数据通信经由10GE-RapidIO网关完成。

图1 网关架构

1 硬件体系结构

整个网关设计环节最重要的部分就是处理器的选择,在查阅相关文献资料后,权衡比较了恩智浦公司的QorIQ P4080和P2020处理器,最终决定选择QorIQ P4080高性能处理器为数据处理及交换的核心。P4080具有卓越的性能,能支持万兆以太网和RapidIO网络,符合该网关的要求。每个模块之间通过超高速串行信号进行互连。单SRIO通道中数据传输率可以达到2.5 Gbps,数据吞吐率非常强。网关硬件平台中板载2路万兆以太网光纤接口及1路千兆以太网接口、1路RS232串行接口,通过后出线板即可扩展出更丰富的接口,具备超强的数据交换能力[5]。硬件结构由CPU中央处理单元、万兆以太网接口单元、高速串行交换单元、以太网接口单元、系统控制单元、电源管理单元和时钟管理单元组成。硬件结构框图如图2所示。

图2 硬件结构框图

CPU中央处理单元:CPU中央处理单元是模块的核心单元,采用QorIQ P4080作为处理器,它是由恩智浦公司生产的新一代高性能通信处理器。P4080处理器的内核相比其他处理器而言更胜一筹。QorIQ P4080凭借结构上的灵活性,使用者可以灵活地对控制数据路径和应用处理进行区分[6-7]。

以太网接口单元:通过千兆以太网交换机得以将CPU与外设连接起来,同时也将单模块单元与系统连接起来。通过底板上的千兆以太网接口与系统中其他模块进行通信,主要用于发送、接收控制及命令信号。P4080片内仅仅集成2路千兆以太网接口,与千兆以太网交换机连接后即可扩展为5路,模块的适应性得到了很大的增强[8]。千兆交换机的PORT0~4作为MDI接口,PORT5作为MII接口,通过RGMII接口与CPU连接,采用全双工工作方式,拥有1 000 Mbit/s的速率。千兆以太网交换机的SMI单元(串行管理接口)接入CPU,此时的CPU做为MAC,而交换机做为PHY。

万兆以太网接口单元:由XAUI接口的万兆以太网PHY芯片BCM8727以及SFP+光纤收发模块组成,用于模块与外部设备之间的接口,实现高速数据传输。BCM8727为双通道10-GbE SFI-to-XAUI收发器,通过XAUI到SFI之间的接口转换,从而实现了CPU与SFP+光模块之间的通信。P4080Z作为万兆以太网MAC,BCM8727作为万兆以太网PHY,MAC通过SMI接口对PHY进行配置和管理,MAC与PHY之间通过XAUI进行数据交换[9]。

高速串行交换单元:高速串行交换单元包括SRIO信号交换以及PCIE信号交换,功能分别由SRIO交换机及PCIE交换机去实现,用于将CPU原生的SRIO及PCIE信号转发到底板上,并扩展相应的通道路数,从而构建出多接口的高速数据传输通道,即可实现模块与系统之间的数据交换。

2 软件系统结构

该万兆以太网与RapidIO网络间数据转换的网关设计采用IP-over-RapidIO技术将以太网数据包封装进RapidIO数据包中实现以太网数据包在RapidIO网络中传输,从而实现万兆以太网和RapidIO网络的互连。IP-over-RapidIO技术由网关相应的软件系统实现。软件系统结构如图3所示。

图3 软件系统结构

IP-over-RapidIO技术是通过将以太网数据帧封装在RapidIO数据帧中,得以实现以太网数据包在RapidIO网络中传输的目的。简而言之,即将由TCP/IP协议栈层层封装的数据帧封装进RapidIO数据包中。这需要RapidIO以太网模拟器和RapidIO底层驱动互相协作来实现。

该技术的重点则是RapidIO地址是如何与IP地址映射的,以及在进行通信的时候,P4080处理器是如何处理来自两个不同网络的数据,即具体的实现过程。

要想使以太网数据包与RapidIO数据包能一一映射可以采用如下方法:可以令以太网数据包中的MAC地址中的最后两位对应RapidIO数据包的ID号,比如以太网数据包的MAC地址为xy:xx:xx:xx:xx:ab,则相映射的RapidIO数据包ID号则为ab。在数据通信时,10GE-RapidIO网关接收到来自RapidIO设备发出的数据包,判断RapidIO数据包ID号是否与以太网数据MAC地址最后两位相一致。若不一致,则向RapidIO其他节点设备转发数据包;若一致,则10GE-RapidIO网关向以太网设备转发数据,以太网设备接收到来自网关转发的数据。数据转发流程如图4所示。

图4 数据转发流程

RapidIO底层驱动为上层的以太网模拟器提供了数据传输接口,以太网模拟器则调用驱动利用RapidIO进行传输,也为上层MUX提供函数接口[10]。同时,以太网模拟器也可与MUX及上层TCP/IP协议栈进行数据交换、处理以太网数据包。

模拟器是调用RapidIO底层驱动,使用户可以像使用以太网一样,通过socket接口、TCP/IP协议使用RapidIO物理网络。它使用RapidIO提供的直接IO/DMA或消息传递等数据传递方式来传输网络数据,并可以使用门铃中断加以控制[11]。通俗地说,就是采用IP over RapidIO方法,在RapidIO网络中将以太网数据帧封装进RapidIO数据包中进行传输。以太网模拟器工作原理如图5所示。

图5 以太网模拟器工作原理

以太网模拟器工作原理:以太网-RapidIO转换网关有两个网络接口,一个是以太网网络接口,另外一个是RapidIO网络接口,MUX接口层收到以太网数据包,并提交到上层,即转换协议层。应用程序通过调用Socket接口可以将数据封装入以太网数据帧,然后通过以太网物理层传至以太网-RapidIO转换网关,数据经RapidIO以太网模拟器转发至RapidIO网络,经解析后,即可上交至Socket接口,输出RapidIO数据包[12]。

RapidIO的驱动包括控制器初始化、硬件抽象层初始化、网络配置及通信控制若干部分。

控制器初始化即初始化硬件的接口、配置端口与寄存器、事务窗口维护、事务呼入呼出窗口读写、呼出门铃窗口的配置,定义dmainit()、riodoorbellinit()、rioportwriteinit()等函数用来初始化DMA控制器、门铃控制器和端口写控制器等[13]。

硬件抽象层(HAL)利用统一的软件接口来配置各种处理部件的寄存器。其函数通过配置读写操作,从而能够访问RapidIO器件的寄存器。

网络配置划分为动态网络配置与静态网络配置,在此使用动态枚举网络配置资源[14]。

RapidIO支持的逻辑层业务包括直接IO/DMA和消息传递。在主设备知道被访问端的存储器映射的情况下可以使用直接IO/DMA,从设备的存储器在这种情形下可以直接被主设备读写[15]。

3 实验与结果

实验环境搭建:1台具有万兆网卡的PC机,1台RapidIO设备,以及10GE-RapidIO网关;PC机与RapidIO之间通过10GE-RapidIO网关连接。测试环境逻辑如图6所示。

图6 测试环境逻辑

实验包括两部分:连通性实验与性能实验。连通性实验的目的是验证网关外部以太网网络与内部RapidIO网络能否正常通信。测试方法主要通过ping命令。具有万兆网卡的PC机IP地址为:192.168.2.64,由RapidIO网络互连的分布式计算系统内部节点绑定虚拟IP地址为:192.168.2.2,用前者去ping后者,实验结果如图7所示。

图7 以太网模块ping RapidIO模块实验结果

性能测试是测试基于IP over RapidIO的数据传输速率。通过在不同的负载下,观察数据传输速率的变化。本研究规定传输数据大小为512 M,将每次传输数据量大小分别定为64 K、256 K、1M、4M,分别来测试在不同负载情况下的数据传输速率。为了使得到的数据结果更直观,将通过IP over RapidIO网关传输和直接通过万兆以太网传输进行一个对比,得到如图8所示的结果,其中:系列1为万兆以太网方式传输;系列2为IP over RapidIO方式传输。

图8 性能试验结果

由图8可知:采用万兆以太网传输时,在不同负载情况下,数据传输速率的变化不大,保持在一个相对较稳定的水平;而采用IP over RapidIO网关传输时,发现在负载为256 K时,数据传输速率较之前有近2倍的提高,而后随着负载的逐渐增大,传输速率也稳中有升。对于大数据量的传输,IP over RapidIO网关传输可以采用内存映射即DMA数据传输,其带宽可以达到相对较高水平。

通过上述连通性实验与性能实验,可以认定该10GE-RapidIO网关能够达到初步的设计要求,可以在实际中使用。

4 结束语

本文分析了RapidIO与万兆以太网TCP/IP协议的特点,通过采用IP over RapidIO的方法,在RapidIO网络中将以太网的数据帧封装进RapidIO数据包进行传输;将RapidIO协议和万兆以太网协议互相转换,从而实现万兆以太网与RapidIO技术的相互连接与转换。该网关解决了分布式计算系统中外部万兆以太网与内部RapidIO网络互联的数据交换,缓解了通信瓶颈压力,增强了分布式计算系统的外部接口性能。

在以太网模拟器的设计中,因为以太网与RapidIO网络之间的互联与通信需要经过MUX接口层、TCP/IP协议栈等,所以每层的处理都会对实时数据的传输速率带来影响,故最终以太网数据包经过解析后得到的RapidIO数据包数据传输速率会出现一部分的降低。针对该问题,可以采用以下方案解决:在以太网与RapidIO网络中,不需要经过MUX接口层及TCP/IP协议栈;在RapidIO数据包的帧头写入源ID与目的ID,将其与以太网数据包中的IP地址一一对应起来,IP发送ARP地址解析包,得到MAC地址,然后将IP地址与MAC地址存入以太网数据帧中,从而可以实现以太网数据与RapidIO网络数据的直接转换与传输,所以传输速率会高于以太网模拟器的传输速率。该过程的具体实现将在下一阶段的工作中完成。

[1] RapidIO Trade Association.RapidIO interconnect specification review1.3[S].Texas,USA:RapidIO Trade Association ,2005.

[2] 林玲,蒋俊,倪明.RapidIO在多处理器系统互连中的应用[J].计算机工程,2006,32(4):244-246.

[3] 李明,康静秋.嵌入式TCP/IP协议栈的研究与开发[J].计算机工程与应用,2002,38(16):118-121.

[4] 高毅,刘永强,赵小冬.基于串行RapidIO协议的包交换模块的设计与实现[J].航空计算技术,2010,40(1):123-125.

[5] 吴海燕.基于RapidIO总线的信号处理平台设计[D].成都:电子科技大学,2009.

[6] P4080 QorIQ Integrated Multicore Communication Processor Family Reference Manual Supports P4080[EB/OL].[2010-08-20].Freescale Semiconductor,Inc.2010.

[7] Freescale.MPC8641D Integrated Host Processor Family Reference Manual[Z].2008.

[8] 张娟娟,陈迪平,柴小丽.VxWorks下RapidIO互连系统的实现[J].计算机工程,2011,15(3):176-178.

[9] 尹亚明,李琼,郭御风,等.新型高性能RapidIO互连技术研究[J].计算机工程与科学,2004,26(12):85-87.

[10]杨卿.RapidIO高速互联接口的设计研究与应用[D].成都:电子科技大学,2009.

[11]王金刚,宫霄霖,熊辉.Wind River.VxWorks网络程序员指南[M].北京:清华大学出版社,2003:186-193.

[12]吕佳彦,杨志义,於志文,等.VxWorks增强型网络驱动程序(END)的分析与实现[J].计算机应用研究,2005,22(4):200-202.

[13]SAM F.RapidIO:The Embedded System Interconnect[M].London:John Wiley & Sons,Inc,2005.

[14]瞿俊杰.软硬件协同设计技术研究[D].上海:同济大学,2003.

[15]潘灵.桑楠.一种RapidIO网络路径分配策略[J].计算机应用,2008,28(Z2):294-295.

(责任编辑 刘 舸)

Interconnection and Transmission of 10 Gigabit Ethernet with RapidIO Network

ZUO Yan, CHAI Xiaoli, GU Yanfei

(East China Institute of Computer Technology, Shanghai 201801, China)

With the continuous development of various high-performance computing systems, the impact of the data transmission on the overall performance of the system is more and more important. RapidIO is a packet-based interconnect architecture:an open interconnect technology standard that meets the needs of a variety of high-performance embedded systems. This thesis briefly introduces some basic concepts of RapidIO and the status of 10 Gigabit Ethernet, and then illustrates RapidIO network and 10 Gigabit Ethernet data transmission process. In that some real-time data needs to be transmitted between 10 Gigabit Ethernet and RapidIO networks, and an idea of gateway design based on data conversion between 10 Gigabit Ethernet and RapidIO networks is proposed. On the hardware platform, making full use of all resources to design and implement the 10GE-RapidIO protocol conversion gateway software system, and using IP-over-RapidIO technology to encapsulate Ethernet packets into the RapidIO packet Ethernet packets in the RapidIO network transmission can help achieve 10 Gigabit Ethernet and RapidIO network interconnection. This approach allows users to further focus on the application development and not to focus too much on complex system technical details. Finally, the design of gateway can be verified practically via establishing experimental platform and completing the experiment.

RapidIO;10 gigabit ethernet;IP-over-RapidIO;gateway

2017-04-09 作者简介:左颜(1992—),男,安徽合肥人,硕士研究生,主要从事嵌入式计算机系统结构研究,E-mail:zuoyan135@163.com。

左颜,柴小丽,顾燕飞.万兆以太网与RapidIO网络的互连与传输[J].重庆理工大学学报(自然科学),2017(8):134-139.

format:ZUO Yan, CHAI Xiaoli, GU Yanfei.Interconnection and Transmission of 10 Gigabit Ethernet with RapidIO Network[J].Journal of Chongqing University of Technology(Natural Science),2017(8):134-139.

10.3969/j.issn.1674-8425(z).2017.08.022

TP302.1

A

1674-8425(2017)08-0134-06