基于SOPC的弹光调制干涉信号高速数据采集*

2017-09-06王丽安永泉王志斌张敏娟王耀利李克武谭绪祥

王丽,安永泉,2*,王志斌,2*,张敏娟,2,王耀利,李克武,谭绪祥

(1.山西省光电信息与仪器工程技术研究中心,太原030051;2.仪器科学与动态测试教育部重点实验室,太原030051)

基于SOPC的弹光调制干涉信号高速数据采集*

王丽1,安永泉1,2*,王志斌1,2*,张敏娟1,2,王耀利1,李克武1,谭绪祥1

(1.山西省光电信息与仪器工程技术研究中心,太原030051;2.仪器科学与动态测试教育部重点实验室,太原030051)

针对弹光调制干涉信号频率高的特点及实时处理的要求,设计一种基于SOPC(System-on-a-Programmable-Chip)技术的可脱离PC环境的弹光调制干涉信号高速数据采集平台。通过在FPGA片上系统调用嵌入式软核处理器(Micro-Blaze),调整系统各部分IP核参数的方法,实现干涉信号的实时采集和处理。对卤钨灯光源经调制后的干涉信号进行采集和处理验证实验,实验结果表明,该系统可以对最大光程差为69.608μm的干涉信号进行实时采集与存储,采集的信号波形与实际弹光特性相一致。

FPGA;弹光调制;SOPC;IP核;Micro Blaze

红外光谱测量技术已在科研、环境、军事等方面有广泛的应用[1-2],基于人工双折射效应的弹光调制傅里叶变换光谱仪PEM-FTS(Photo-Elastic Modulation Fourier Transform Spectrometer)为红外光谱测量提供一种高速、宽光谱范围、高灵敏度的测量方案[3]。美国Los Alamos国家实验室最先对弹光调制傅里叶变换光谱仪进行研究,并将其运用到超光谱荧光显微镜和血细胞计数仪上[4]。在国内,天津大学胡淼[5]等人对基于弹光调制的红外光谱吸收进行了研究,中北大学张敏娟[6]等人对大光程差PEM-FTS的快速反演算法进行了研究。然而,实际上由于弹光调制干涉信号具有频率高、信息量大、对信息处理实时性要求高等特点,需要对其进行高速、实时采集。最近,我们采用基于PCIE总线的高速数据采集方案[7],实现了对弹光调制干涉信号的实时采集。但该数据采集系统,需具有PCIE插槽的PC来支持数据存储和处理,降低了整体系统的灵活性和集成度。

基于上述现状,本文提出了一种可脱离PC环境的弹光调制干涉信号高速数据采集方案,该方案采用SOPC(System On a Programmable Chip)嵌入式技术,将FPGA芯片上嵌入大量可随时升级的IP (Intelligent Property)核,从而可以快速实现集成度高、升级维护灵活的高速数据实时采集系统。采用Xilinx公司的Spartan6芯片配置Micro Blaze微处理器软核,利用软件和硬件的联合设计,加载相应的外设IP核实现高速数据采集系统,即在FPGA控制下将采集到的弹光调制干涉信号以DMA传输方式存储到DDR3 SDRAM。

1 弹光调制干涉信号的工作原理

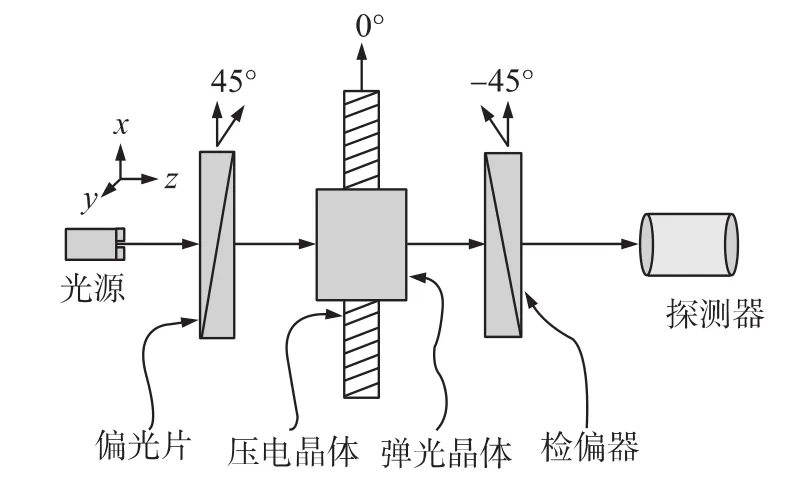

弹光调制傅里叶变换光谱仪的核心器件——弹光调制器(PEM)由提供驱动的压电晶体和产生双折射效应的弹光晶体通过胶粘合而成。利用压电晶体在光学各向同性的弹光晶体加以周期性变化的机械应力,形成应力驻波,该应力驻波会驱动弹光晶体以正弦函数形式振动,进而改变其折射率。其工作原理如图1所示。

图1 弹光调制干涉具调制原理图

当被测光经过与x、y轴成45°起偏器后,进入发生共振的弹光晶体时,就会发生双折射,被分解为相互垂直的o光和e光,折射率分别为no和ne。通过晶体后的光程差为L=D(no-ne)=D·Δn其中,Δn= B sin(w0t)为折射率差,而B为双折射率差的最大幅值,w0为调制器的谐振角频率(w0=2πf0,f0为谐振频率),D为晶体的厚度。最后利用点探测器接收干涉光信号,再通过外部采集系统即可获得调制后的干涉信号。

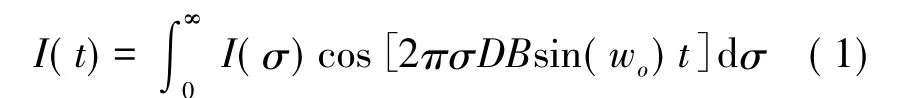

滤除直流成分后的干涉信号I(t):

式中,σ为被测光的波数。

经傅里叶变换得到被测光谱为I(σ):

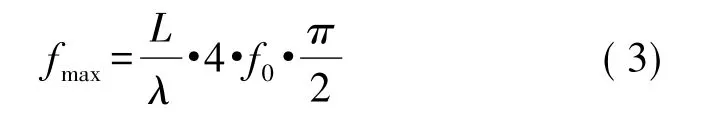

根据式(1)、式(2)可得信号最高频率为fmax[3]:

弹光调制器的谐振频率f0一般为50 kHz左右,光谱仪的工作波段λ为2μm~10μm,由式(3)可得在最大光程差L一定时,信号的最高频率为fmax=在满足数据无失真复原的条件下,系统的采样率至少为2fmax。

2 系统硬件平台设计

在系统硬件结构中,Xilinx公司Spartan6系列的XC6SLC150T-3FGG676C芯片具有功耗低、资源利用率高的特性,从而选用其来实现系统控制。该芯片内部集成了1片32 bit的处理器软核(Micro Blaze),Micro Blaze采用数据总线及指令总线相互独立的哈佛结构的RISC(Reduced Instruction Set Computer)架构,支持数据缓存及指令缓存,能够以较高的速度访问片上及片外程序存储器;8个串行收发器(General Data Transfer Platform,GTP)(最高速率达3.2 Gbit/s);4个存储器控制模块(Memory Control Block,MCB);23 038个Slice;268个18 kbyte的双口Block RAM;6个时钟管理模块CMT(每个CMT由两个DCM和一个PLL构成)等资源。该芯片具有很高的逻辑资源,因此适合实时高速数据采集系统的设计选择。

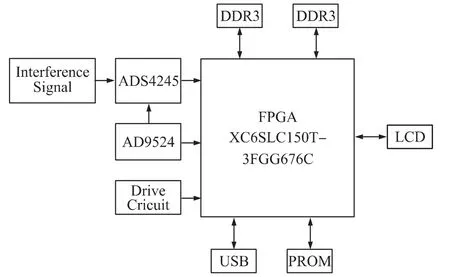

系统整体设计如图2所示,模/数转换器ADS4245具有100 Msample/s的转换速率、14 bit的分辨率、可以实现对弹光调制干涉信号的无失真采集;将采集到的数据以DMA传输方式存储到两片DDR3 SDRAM;外部时钟分配器AD9524提供ADC的采样时钟和FPGA内部参考时钟,该时钟芯片具有低抖动低噪声等特性,可以提高系统的动态性能;FPGA芯片采用Xilinx Spartan6系列,其资源丰富、价格低廉、设计灵活方便,是高密度集成数据处理应用的理想选择;FPGA的控制下将DDR3 SDRAM中的数据传输到TFT070-A型LCD上进行显示,其分辨率为800像素×480像素,显示区域大小为600像素×450像素。

图2 系统结构原理图

3 SOPC系统设计

SOPC[8-10]是一种片上系统SOC(System on Chip)与FPGA结合的嵌入式系统;嵌入式FPGA的主要是使用纯逻辑的方式来实现控制功能,其硬件的反应时间在纳米级,适合于实时性要求较高的场合。

施加一定应力后,ND钢钝化膜被机械破坏,导致基体遭遇更严重的腐蚀,而Corten钢在相同情况下能依靠内侧掺混残存的少量合金元素形成的氧化物减缓腐蚀速率,因此Corten钢腐蚀速率更低。对耐腐蚀材料采取掺混合金及表面强化相结合的方式可能更有利于抵御应力对耐腐蚀性的削弱。

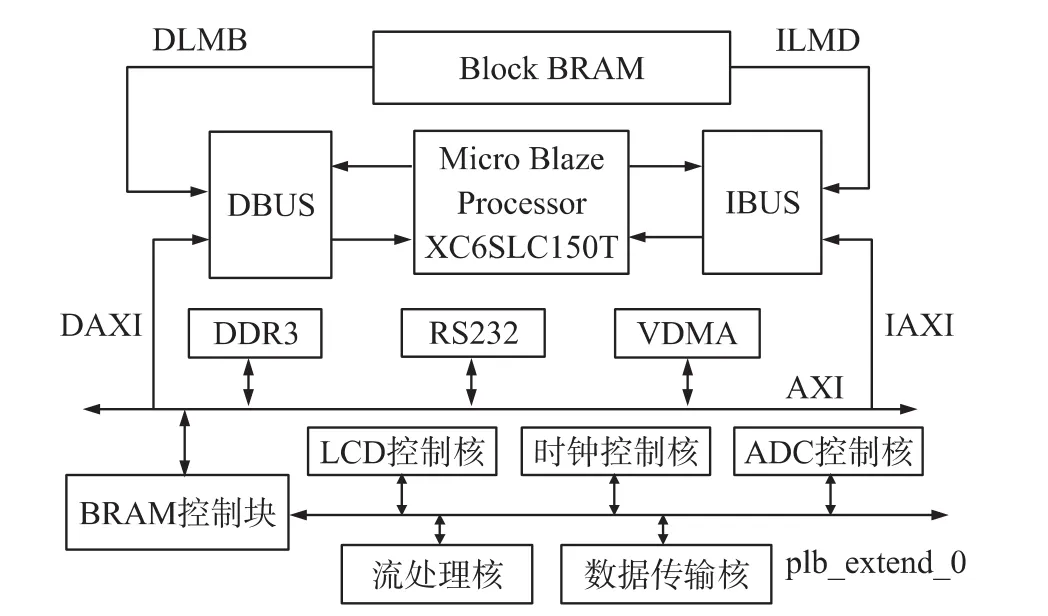

本文提出的基于SOPC技术的弹光调制干涉信号高速数据采集系统,即在一片高性能、低功耗的Spartan6 FPGA芯片上实现AD配置、时钟配置、流处理控制、数据传输控制、LCD控制等模块。SOPC技术分为硬件设计和软件设计两部分,硬件设计利用Verilog硬件描述语言实现内部控制系统;软件设计利用硬件配置自动生成的软件包、SDK板级支持包和C语言,实现了系统的驱动程序和应用程序设计。SDRAM中。数据传输控制核可以实现驱动电路与FPGA之间进行数据传输,传输的数据为参考信号的调制频率及一个驱动周期内干涉信号的峰数,可以实现最大光程差的确定[11-12]。

图3 SOPC硬件原理图

3.1 SOPC硬件设计及各个模块的搭建

整个系统硬件设计如图3所示,本地存储总线(LMB)将简单的程序指令和数据存到FPGA的片上内存Block RAM。AXI(Advanced Extensible Interface)总线能够使SOC(System on Chip)以更小的面积、更低的功耗,获得更加优异的性能。设计中在64 bit的AXI总线上外挂了一个串口RS232控制器、两块256 Mbyte大小的MCB_DDR3_BANK控制器、双通道VDMA控制器、BRAM控制器等IP核。BRAM控制器扩展总线plb _extend_0,该总线是由BRAM控制器的读写操作封装而成,CPU通过控制BRAM控制器,完成对挂在该总线上外设IP核包括时钟控制、ADC控制、LCD显示控制、流处理控制、数据传输等的操作。流处理单元是将经FPGA还原后的AD采集的数据进行处理以满足DMA的格式,最后DMA控制器将数据缓存至内存DDR3

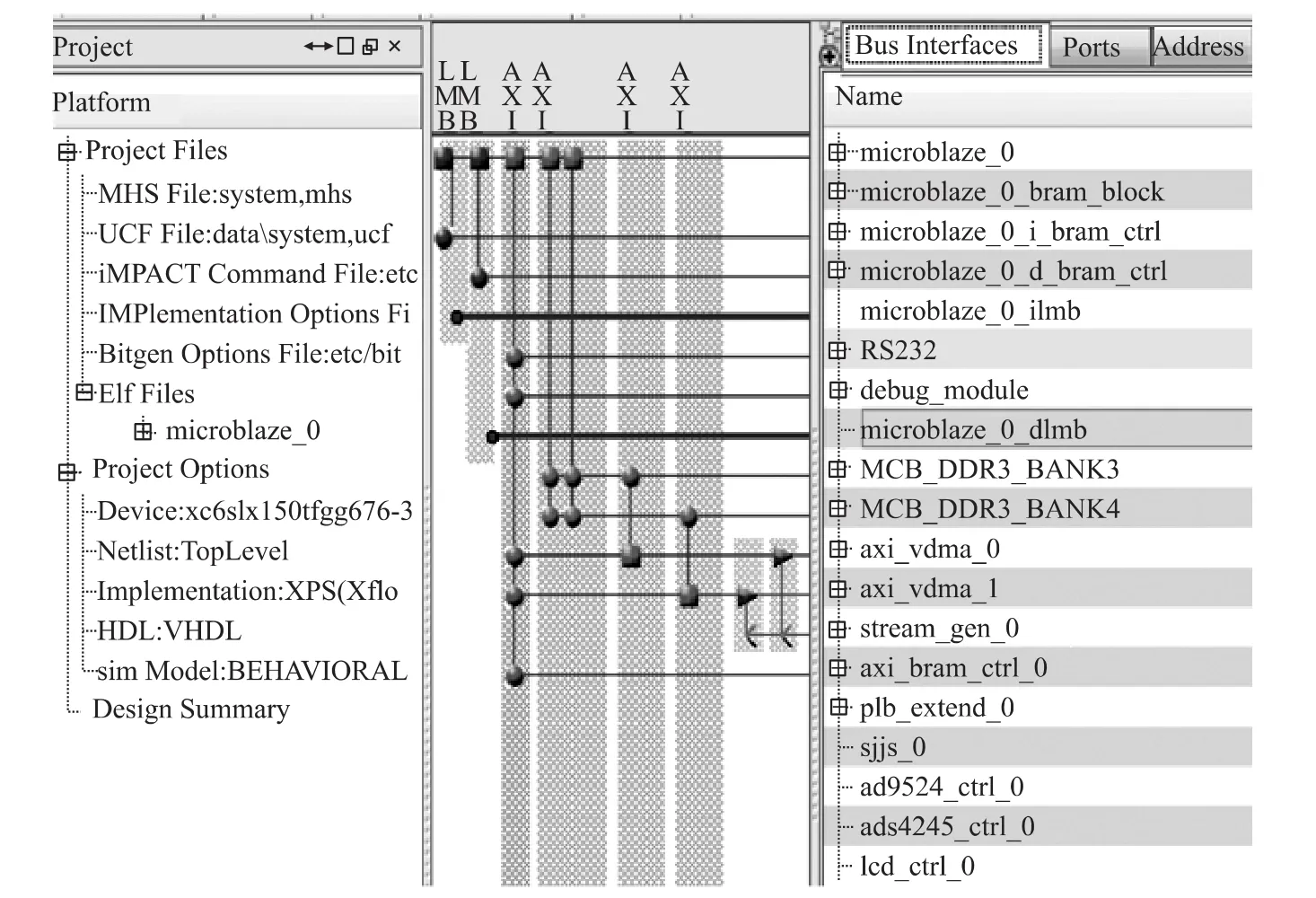

在XPS(Xilinx Platform Studio)13.2硬件原理实现如图4所示,总线接口(Bus Interfaces)模块中嵌入的各外设IP核分别挂在相应的总线下;端口(Ports)模块中包括顶层端口和各模块端口,不同模块的端口之间相互连接从而实现数据流的传输、以及将其中的FPGA物理端口设置为外部端口,直接连接到所需控制的外设;地址生成(Addresses)模块为Micro Blaze处理器及相应的外设IP核分配相应地址,采用存储器映像方式实现处理器与各存储器的通信。此外,通过编写处理器硬件规范文件MHS(Micro Processor Hardware Specification)亦可实现硬件各个模块的设计和搭建。MHS文件定义了外部端口、嵌入式处理器及外围设备各模块的地址分配和连接关系。这是两种用来搭建系统平台的表现方式。它们之间是相互关联的。

图4 SOPC硬件实现图

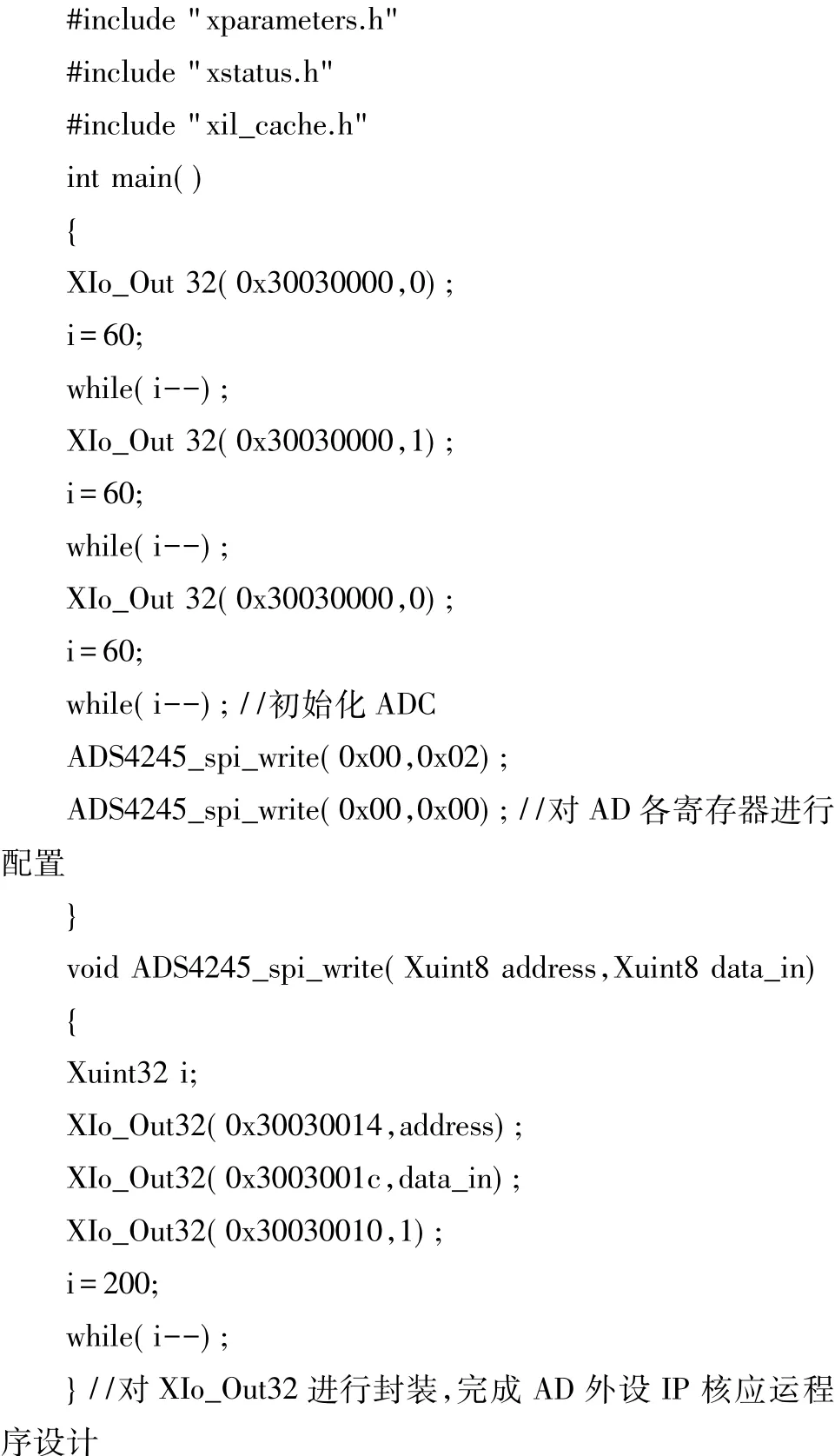

3.2 SOPC软件设计

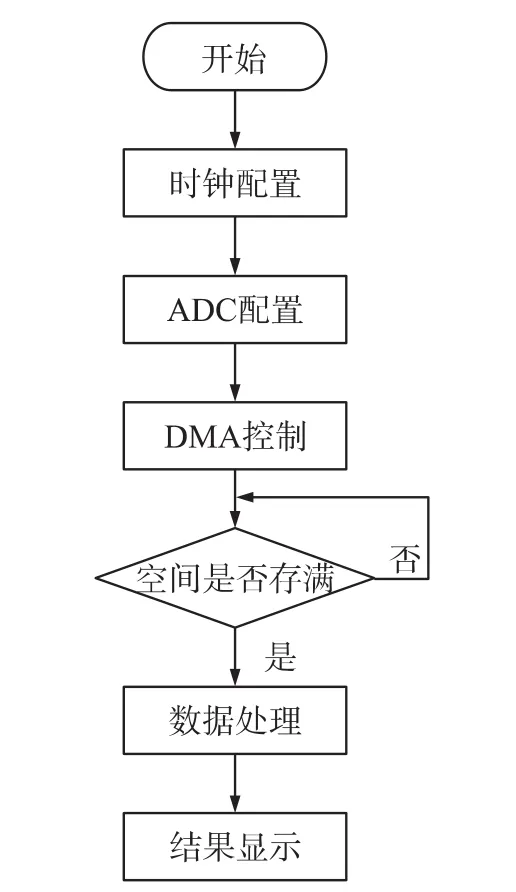

硬件设计完成后,将设计生成的比特文件及存储器映射文件导入到软件,开始软件设计。软件设计包括外设驱动程序设计和应用程序设计。驱动程序设计可利用SDK(Software Development Kit)中的BSP(Board Support Package)实现,可建立Standalone及Xilkernel型的驱动程序,设计中选用Standalone型。展开支持包文件中的Include项发现一个xparameters.h文件,其为参数定义文件,主要包含一些能够对硬件各个模块属性、相关参数以及地址进行申明的宏定义。该头文件是软件工程主程序中必须包含的,因其包括了系统中各个硬件模块的基本属性和地址信息。这样才能实现软硬件联合操作,软件实现中还要包含其他源程序中要用到相关库的头文件,如stdio.h、platform.h、xil_ cache.h等头文件。头文件宏定义之后就是编写主程序main.c文件,其源程序的简单流程图如图5所示。

图5 软件程序编写流程图

4 实验结果分析

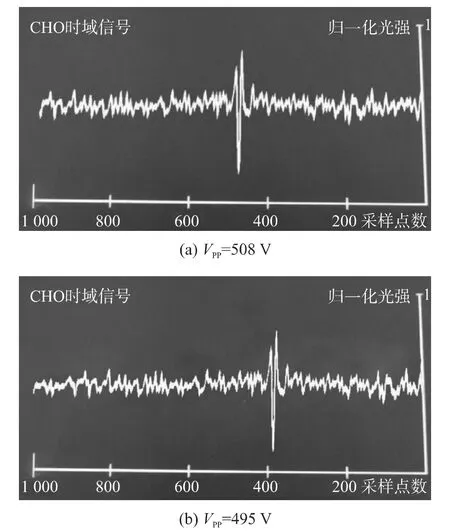

弹光调制干涉信号输入到硬件电路后,加载设计中所述的高速数据采集系统。硬件平台生成网表,最后生成硬件比特文件和存储器映射文件。软件通过建立脚本文件并进行编译生成可执行文件。将硬件文件和软件文件合成一个可下载的download.bit文件,下载到FPGA中运行并观察显示结果,如图6所示。

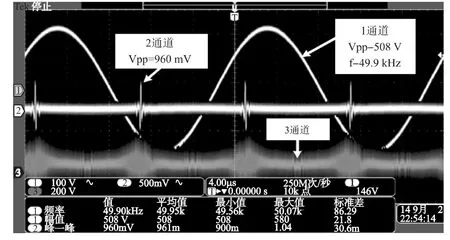

图6(a)、图6(b)为驱动频率f0=49.90 kHz,驱动电压VPP=508 V、495 V下LCD显示的弹光调制干涉信号波形。由于弹光调制干涉信号的驱动电压越大其最大光程差越大,由式(3)知其对应的信号最高频率及最大采样率就越大。图7是驱动电压VPP=508 V对应的示波器采集信号。

图6 LCD显示干涉信号图

图7 示波器采集信号图

图7中1通道为驱动信号,其频率为49.90 kHz、电压为508 V;2通道为输入光波长2μm~10 μm的弹光调制干涉信号;3通道是参考信号,为波长λ=632.8 nm的弹光调制干涉信号。由图7可见,在一个调制周期T=1/49.90 ms内,参考信号产生了N=440个峰,可得最大光程差L=Nλ/4= 69.608μm。由式(3)知此时2通道弹光信号的最高频率fmax为10.906 MHz,在满足信号无失真复原的条件下,系统的采样率至少为21.813 MHz,为了更好的实现弹光信号的复原,本基于SOPC技术的高速数据采集系统的采集频率已达到100 MHz,可实现对弹光调制干涉信号的无失真采集。

5 结语

本文设计了一套基于SOPC的弹光调制干涉信号采集系统,采样率为100 MHz的高速模/数转换器可以对最大光程差为69.608μm的干涉信号进行准确地采集。采用Spartan6 FPGA作为核心控制模块,将采集到的数据以DMA传输方式存储到两片DDR3 SDRAM。DMA方式传输数据的过程中不需要处理器的干预,提高了系统数据的传输速度,优化了数据采集存储方式,使得整个数据采集系统具备较高的实时性,根据实际采样速度的需求,对AD控制逻辑进行调整。该系统为弹光调制干涉信号提供了一种实时高速、可脱离PC环境的解决方案。

[1]马恒,王志斌,张记龙,等.改进多项式迭代拟合红外光谱基线校正方法[J].激光技术,2013,37(2):223-226.

[2]姚涛,吕群波,相里斌,等.非均匀采样干涉数据光谱反演技术研究[J].光谱学与光谱分析,2010,30(5):1430-1433.

[3]张敏娟.弹光调制傅里叶变换光谱复原高速数据处理技术研究[D].山西太原:中北大学,2013.

[4]Buican T N.High Retardation-Amplitude Photo-Elastic Modulator.US 7,764,415B2[P].2010.07.27.

[5]胡淼,王太勇,乔志峰,等.基于弹光调制的红外光谱吸收法在室内VOC检测中的研究[J].光谱学与光谱分析,2012,31 (12):3232-3235.

[6]张敏娟,王召巴,王志斌,等.大光程差PEM-FTS的快速光谱重建[J].光谱学与光谱分析,2014,34(7):2010-2014.

[7]杜鹏飞,王志斌,王艳超,等.弹光调制干涉信号的高速数据采集系统设计与实现[J].计算机工程与设计,2014,35(8):2728-2731.

[8]黄云,杨尊先.基于SOPC的数据采集与处理系统设计[J].电子器件,2010,33(1):67-70.

[9]尚媛园,杨新华,徐达维,等.基于SOPC技术的高速图像采集控制系统的设计与研究[J].传感技术学报,2011,24(6):864-869.

[10]邹晨,高云.FPGA内嵌处理器的SOPC系统设计与分析[J].航空计算技术,2013,43(5):123-127.

[11]张敏娟,王志斌,李晓,等.弹光调制干涉图最大光程差的稳定性及检测技术研究[J].光谱学与光谱分析,2015,35(5):1436-1439.

[12]张敏娟,王召巴,王志斌,等.大光程差PEM-FTS的快速光谱重建[J].光谱学与光谱分析,2014,34(7):2010-2014.王丽(1990-),女,汉族,山西朔州人,硕士研究生,主要研究方向为高速数据采集、信息与信号处理,389263397@ qq.com;安永泉(1976-),女,汉族,黑龙江哈尔滨人,副教授,研究生导师,研究方向为气动光学、光电仪器与光学成像技术研究,anyongquan107@hotmail.com。

High-Speed Data Acquisition of Photo-Elastic M odulator Interference Signal Based on SOPC*

WANG Li1,AN Yongquan1,2*,WANG Zhibin1,2,ZHANGMinjuan1,2,WANG Yaoli1,LIKewu1,TAN Xuxiang1

(1.Engineering Technology Research Center of Shanxi Province for Opto-Electronic Information and Instrument,Taiyuan 030051,China; 2.Key Laboratory of Instrumentation Science and Dynamic Testing of the Ministry of Education,Taiyuan 030051,China)

A high-speed data acquisition platform,which can be separated from the PC environment based on a Programmable Chip(SOPC)technology,a system was designed against high frequency characteristic and real-time processing requirements of the photo-elasticmodulator interference signal.Using themethod of calling the embedded soft-core processor(Micro-Blaze)and adjusting each partof the system IP core parameter on chip of FPGA real-time data acquisition and processing of the interference signal can be realized.The results of acquisition and processing validation test ofmodulated signals of the tungsten-halogen light source shows that this system can acquire and store the interference signal in real-timewhile the optical path difference is 69.608μm and thewaveform of photo-elastic is consistentwith the actual characteristics.

FPGA;photo-elastic modulator;SOPC;IP core;Micro Blaze

C:7210G

10.3969/j.issn.1005-9490.2017.01.019

TP274+.2

:A

:1005-9490(2017)01-0098-05

项目来源:国家自然科学基金青年科学基金项目(61505180);山西省青年科技研究基金项目(2015021084);山西省青年科技研究基金项目(2014021012)

2016-01-22修改日期:2016-03-18