一种固定工作时钟的可变码速率同步器

2017-07-14康超谢作全陈丽婷

康超+谢作全+陈丽婷

摘要:在目前的遥测通信系统中,从PCM码流中直接提取时码钟是最常见的码同步方法。传统码同步器的工作时钟都是码速率的16倍,无法适应码速率可变的通信系统。该文提出了一种基于FPGA的固定工作时钟码速率可变码同步器,结构简单易于在FPGA上实现,同步时间快,性能优越。

关键词:码同步;PCM码;鉴相器;DDS;FPGA

1背景

在当前的数字通信系统中,通常采用锁相法来实现码同步器。其工作原理为利用16倍码速率的时钟对PCM码和接收端自身产生的时码钟进行相位比较,产生相位误差信号(系统相位超前或滞后信息),徘徊滤波器对相位误差信号滤波以消除干扰,在确认系统处于相位超前或滞后状态后对时码钟进行调整,最终达到与PCM码同频同相的目的。本文基于锁相法的设计思路,提出了一种固定工作时钟码速率范围409.6Kb-ps~10Mbps的码同步器,结构简单、资源利用率小,易于在FP-GA上实现。

2工作原理

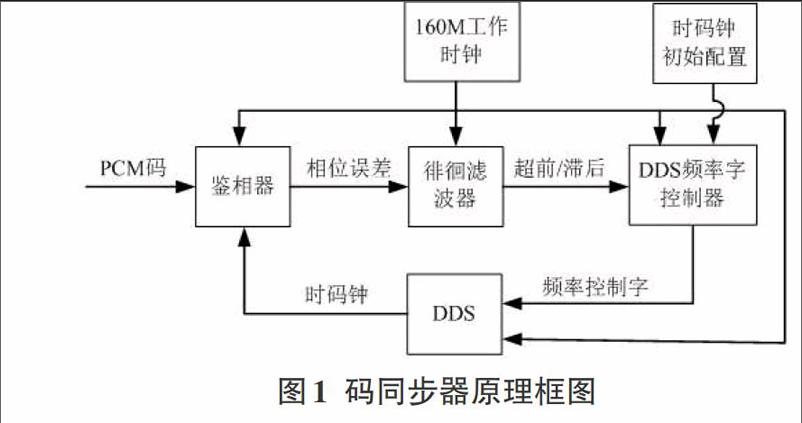

码同步器主要由DDS、鉴相器、徘徊滤波器、DDS频率字控制字四个模块组成,都以160MHz时钟工作。DDS根据上位机传下来的时码钟初始配置信息产生一个与PCM码同频的时码钟,鉴相器对PCM码和时码钟采样并比对沿口得到相位误差信息。误差信息送至徘徊滤波器进行判决,只有在连续3个码元周期内都存在相位超前/滞后情况下DDS频率字控制器才会调整DDS步进使时码钟沿口提前/延后。调整后的沿口再次与PCM码进行相位比对,直至PCM碼与时码钟沿口对齐。码同步器原理框图如图1所示:

3算法实现

1)鉴相器

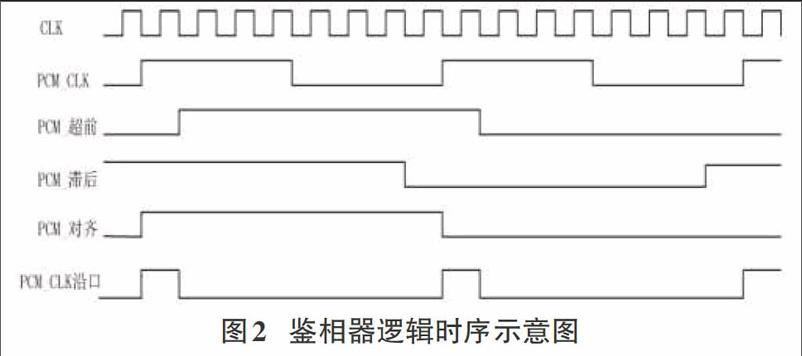

鉴相器的功能是完成PCM码和时码钟的沿口比对,输出相位超前/滞后的误差信息,其逻辑时序示意图如图2所示。首先用CLK对PCM码流进行采样,可以保证图中所有信号都与CLK的沿口对齐。

按最高码速率的16倍计算,工作时钟CLK为160MHz。首先对两个PCM_CLK沿口间的PCM码进行0/1计数,若cnt0/cnt1=0说明此时沿口是对齐的。若cnt0/cnt1=0,以图2中为例cnt0=1说明存在1个CLK的相位误差,此时结合PCM码极性变化信息便可得到超前/滞后信息。

2)徘徊滤波器

徘徊滤波器的功能是对鉴相器输出的相位误差信息进行判决,滤除干扰信号。因采用固定工作时钟,所以鉴相器对不同码速率的鉴相精度也是不同的:10Mbps下是1/16,5Mbps下是1/32,2Mbps下是1/80……,传统码同步器的鉴相精度为1/16,所以本文针对不同码速率设置相应的门限判决是否存在相位误差。

当相位误差超过判决门限时,徘徊滤波器判定误差有效,只有连续3个码元都判定误差有效的情况下才输出超前/滞后信息给DDS频率字控制器调整。

3)DDS频率字控制器

DDS频率字控制器的功能是根据超前/滞后信息调整DDS的频率控制字,使DDS输出的沿口提前或延后。上位机根据不同码速率计算出初始频率控制字,正常情况DDS以此控制字工作。当时码钟超前时,根据计数器中相位误差个数将频率控制字置0,达到相位误差个数后控制字恢复为初始值;当时码钟滞后时,根据计数器中相位误差个数将频率控制字置为默认控制字的2倍,达到相位误差个数后控制字恢复为初始值。

4)DDS

DDS(Direct Digital synthesizers)是FPGA自带的IP CORE被广泛应用于数字通信处理系统,作为载波跟踪环的NCO使用,可根据控制字输出频率实时可变的两路正交正余弦信号。本文利用DDS输出频率可控的特性,将其内部累加器的最高位输出作为时码钟。DDS的原理就是在每个工作时钟对频率控制字进行累加,将累加器的结果查表得到相应的正余弦信号。所以频率控制字就是累加器的步进,增加频率控制字累加器最高位就会提前翻转,控制字置0累加器最高位就会延后翻转。

本文的DDS位宽设计为16位,工作时钟160MHz,控制字计算公式如下:

初始频率控制字=160M*2/码速率 (1)

例码速率为10Mbps时,初始控制字为4096;码速率为2Mbps时,初始控制字为819。

4性能分析

1)同步精度

本文中鉴相器的工作时钟是160MHz,码速率范围409.6Kbps~10Mbps,所以理论上同步精度在409.6Kbps时为1/390码元长度,10Mbps时为1/16码元长度。徘徊滤波器对码速率范围设置了不同的门限,本文码同步器的同步精度最高为1/40码元长度,最低为1/16码元长度。可以通过修改判决门限来调整码同步器的同步精度。

2)同步时间

在确认存在超前,滞后情况后,DDS频率字控制器会根据鉴相器输出的相位误差长度来调整DDS频率字,所以在一个码元周期内即可完成同步工作。

3)不同码速率适应情况

本文码同步器使用DDS输出时码钟,DDS工作时钟160MHz,位宽16位,所以时码钟分辨率为2.44KHz。

按上文公式(1)计算DDS初始频率字会存在不是整数的情况,如2Mbps码速率下结果为819.2,实际使用中四舍五入取819。此时DDS的输出时码钟频率为1.99512M,存在0.0244%的误差。理论上DDS输出最大频率偏差为1.22(0.5*2.44)KHz,按最低码速率409.6Kbps简单计算,本文码同步器的理论最大误差为0.3%,实际上409.6Kbps码速率的频率偏差为0.56K,误差为0.13%。

因此在理想的PCM码流情况下,如果按公式(1)计算的初始频率字为整数则码同步器一旦同步好便无需再调整时码钟沿口,如果初始频率字为不是整数则码同步每隔一段时间调整一下时码钟沿口。

5结束语

本文基于锁相法的设计思路,利用鉴相器比较PCM码与时码钟的相位误差进一步调整DDS频率控制字最终达到PCM码与时码钟同频同相的目的仅需FPGA即可实现,占用资源小,同步时间快。与传统码同步器相比具有很大的灵活性,可适应409.6Kbps~10Mbps码速率,同步精度可调整,可广泛应用在通信系统基带信号处理中。