基于FPGA的视频以太网传输

2017-06-02李嘉琛杨光

李嘉琛 杨光

摘要:为解决视频传输实时性问题,提出采用现场可编程门阵列(FPGA)作为主控芯片来控制CMOS传感器进行图像采集,然后和上位机之间进行以太网数据通信。加入ChipScope软件进行在线逻辑分析。实验结果表明系统实现了高质量视频实时传输,且具有耗能低、稳定性高等优点。

关键词:FPGA;图像采集;以太网

中图分类号:TP393.11 文献标识码:A 文章编号:1007-9416(2017)04-0032-04

面对日益增长的数据流和多媒体服务,大容量、高速率、多功能模块高端网络产品的市场规模将不断扩大,以太网的出现能够很好地满足这一市场需求。TCP(Transmission Control Protocol)和UDP(User Datagram Protocol)属于传输层协议。TCP是基于连接的协议,在正式收发数据前,必须建立可靠的连接,因此可以提供IP环境下数据的可靠传输,但也使得通信效率变低。UDP协议不属于连接型协议,它不与对方建立连接,而是直接就把数据包发送过去。因而具有资源消耗小、在数据传输过程中延迟小和传输效率高等优点,可以有效地实现图像数据快速传输。FPGA在高速数据信号采集、处理具有最为显著优势,且集成度高,功耗低,编程配置灵活。为此本文就FPGA和UDP/IP协议相结合的方式设计了一个视频快速传输系统,并从时序仿真、功能仿真和硬件平台上验证了其可行性。

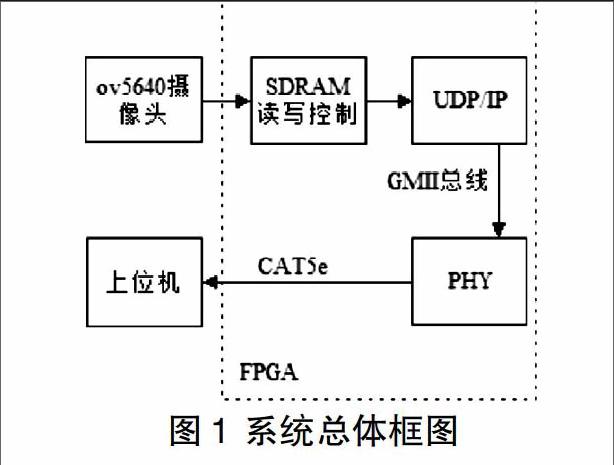

1 系统概述

为提高系统的集成度、可靠性和稳定性,首先对主控制器进行选择。FPGA打破了顺序执行模式,在每个时钟周期内可完成更多的处理任务,远远超越了数字信号处理器(DSP)的运算能力。本设计中选用Xilinx公司低成本的Spartan6 XC6SLX9作为主控芯片,采用Realtek公司的PHY芯片RTL8211E来实现以太网数据通信。

图1为视频以太网传输的整体原理框图,包含数据采集系统、数据处理系统和数据接收系统三个部分。数据采集系统采用OV5640高清摄像头模组来实现图像的采集,FPGA通过I2C总线对OV5640摄像头内部寄存器进行配置,使其工作状态满足要求。FPGA把采集到的图像数据流写入内部SDRAM进行数据缓存。对于SDRAM的读写采用乒乓结构来实现图像数据快速读写。通过不断地读取SDRAM内部储存的数据,将数据流按照UDP协议打包成IP数据包,之后把IP数据包按照标准以太网帧格式封装后通过GMII总线发送到PHY芯片,之后PHY芯片通过CAT5e网线将数据包发送至上位机。上位机通过接收网口的UDP数据包,提取图像数据。

2 数据采集及缓存

2.1 数据采集

FPGA通过总线来完成OV5640内部寄存器的配置,使它的输出格式为JPEG,像素大小为1280*720。由于JPEG格式下输出的图像每一帧的数据大小是不相等的,这里设置JPEG 输出的数据模式为2,此模式下可以设置内部寄存器4600来确保每一帧都有一个固定的行数,默认为1024。如果最后一行的数据没有达到固定宽度时,寄存器会自动添加虚拟数据以匹配固定宽度。

配置完寄存器后,OV5640输出的像素时钟PCLK作为像素数据采样的基准。在寄存器配置完成后需要等待至少10帧,即OV5640工作稳定后,才开始采集图像数据。当行场有效时(即CMOS_VSYNC为低电平,COMS_HREF为高电平)图像数据有效,此时FPGA可以在PCLK上升沿读取8位图像数据。由于数据流在SDRAM存储数据宽度为16bit,所以这里第一个PCLK上升沿时进行8位图像数据的暂存,第二个PCLK上升沿再进行8位数据转16位数据转换操作。此时定义一个数据同步输出信号CMOS_oCLK,其上升沿表示16位数据开始有效,下降沿时16位数据稳定,外部模块可以读取数据。

利用xilinx的ChipScope软件抓取摄像头采集到的图像数据如图2所示,在信号CMOS_HREF为高电平时,开始输出8bit图像数据CMOS_iDATA并暂存,然后再进行8位数据到16位数据转换操作,输出有效数据CMOS_oDATA。图中CMOS_oCLK上升沿表示图像数据开始有效,CMOS_oCLK的下降沿表示數据稳定。

2.2 数据缓存

图像数据采集完成后,需要对图像数据流进行缓存。首先,正常情况下摄像头的输出为25Mhz的8bit的数据流,经过2次8bit的数据拼接后,将转变为12.5Mhz下的16bit数据流。而以太网通信中发送数据的时钟为125Mhz,这涉及到跨时钟域数据交互。其次,标准以太网帧长度范围为64~1518字节,当以太网帧长度小于64字节时,会造成双方通信的数据发生冲突,导致数据传输失败。因此需要大容量的存储器来缓存图像数据流。

鉴于图像数据量大,而且图像数据从采集到以太网传输的过程中存在低频域到高频域的跨时钟域数据转换,为了提高系统的稳定性,防止数据的错位与丢失,采用大容量SDRAM(即同步动态随机存储器)作为缓存单元,来实现跨时钟域数据的交互。这里选用的SDRAM型号为HY57V2562,容量为256Mbit,存储架构为4M×4Banks×16bit。数据缓存原理框图如图3所示。

FPGA片内的RAM、FIFO都可以设置成双端口读取模式,即独立的读时钟与写时钟。其固有的特性决定了可以在两个时钟域下进行数据的读写操作。FIFO采用的是先入先出机制,同时根据存储的容量判断所存储的跨时钟域数据的量,很容易就能实现跨时钟域数据的交互。系统采用一个写FIFO(即WRFIFO)和一个读FIFO(即RDFIFO)来完成图像数据在SDRAM中的写入和读取。具体的操作时序流程如图4和图5所示。

SDRAM读和写采用乒乓结构来实现图像数据快速读写。SDRAM中共有4个Bank,将4个Bank划分为两个部分,即Bank0+1和Bank2+3。SDRAM初始化完成后,首先将图像数据流写入Bank0+1中,此时从Bank2+3中读取图像数据。当一帧数据写入且读取完毕后,切换到Bank2+3进行下一帧数据的写入;同时读取Bank0+1中的图像数据,依次循环,保证数据流的连续性。使用ISE的片内逻辑分析工具Chipscope来观察图像数据在SDRAM控制模块中的写入和读取如图6所示。

3 Ethernet UDP通信

3.1 UDP/IP协议

UDP是一種无连接的传输层协议,主要作用是将网络数据流量压缩成数据包的形式。具有资源消耗小,处理速度快的优点,它们即使偶尔丢失一两个数据包,也不会对接收结果产生太大影响。每一个UDP数据包的前8个字节用来包含报头信息,剩余字节则用来包含具体的传输数据。如图7所示,UDP首部由4个域组成,包括源端口号、目的端口号、UDP数据包长度和校验和,每个域各占用2个字节。

UDP协议包只是IP包中的一种, UDP在IP报文的协议号是17。以太网数据需要封装为标准帧之后再进行传输,如图8所示为本次设计中的以太网帧格式。以太网首部包括帧头标记、目的MAC地址、源MAC地址和IP包类型。数据域包括20字节长度的IP首部、8字节长度的UDP首部和图像数据。帧校验的长度为4字节。

3.2 UDP/IP通信

UDP/IP通信模块中读取SDRAM内部存储的数据流,按照以太网数据包格式对数据进行包,FPGA通过GMII总线和PHY芯片通信,PHY芯片把图像数据包通过网线发给上位机。

一帧以太网数据发送过程为:先发送8个字节的以太网帧头标记(7个字节前导码和1个字节的帧起始定界符),再发送6个字节的目标MAC地址和6个字节的源MAC地址,接着发送两个字节的IP包类型。以太网首部表示一个IP数据包传输的开始;目标MAC地址为数据要发送对象的MAC地址,即目标MAC地址的值为上位机的MAC地址。源MAC Address是指FPGA本地的MAC地址。IP包类型值为0x0800。

发送完IP包类型之后开始发送IP数据包首部,IP数据包首部为20字节。本设计源地址IP:192.168.1.105,目标地址IP:192.168.1.109。然后发送八个字节的UDP首部,接着发送SDRAM缓存的图像数据,最后发送4个字节的CRC32校验值。如图9所示,为ChipScope软件抓取的数据包,可以看到FPGA(IP:192.168.1.105)向上位机(IP:192.168.1.109)发送的数据包,显示了数据包的以太网帧头标记、目标MAC地址、源MAC地址、IP包类型、IP首部、UDP首部以及图像数据和校验值等信息。

4 程序设计

在一个系统中,软件和硬件相辅相成,两者缺一不可。FPGA程序设计按自顶向下的设计方法,采用Verilog语言在Xilinx开发的ISE14.7环境下进行硬件描述。整个Verilog设计由一个顶层设计模块和五个子模块构成。如图10所示,系统控制模块例化了一个PLL时钟模块,PLL时钟模块调用PLL核来产生不同频率的时钟,分别作为SDRAM的驱动时钟、SDRAM控制器的控制时钟、摄像头的驱动时钟等,同时系统控制模块产生一个全局复位信号。摄像头模块例化了三个子模块,分别为复位等待模块、寄存器配置模块和图像采集模块。其中复位等待模块用来满足OV5640上电时对时序的要求。另外程序中加入Chipscope模块来观察FPGA内部想要观察的任何信号。

5 系统测试

运行上位机NicWinPcap软件,设置好IP地址和端口号,选择视频的保存路径后即可开始视频的录制。同时运行网络抓包工具Wireshark软件,观测到系统以太网数据传输的速度如图11所示。视频录制完成后如图12所示。

6 结语

本文针对实时视频以太网传输系统的设计作了系统的阐述。系统采用编程方便灵活、集成度高、处理速度快的FPGA作为主控芯片。FPGA将OV5640高清摄像头模组采集到的图像数据通过以太网传输到上位机。利用ISE软件中附带的ChipScope工具将采集到的数据信号进行逻辑、时序分析,保证了图像数据采集、缓存和传输的准确性。研究结果表明该系统具有集成度高、处理速度快、功耗低、性价比高、可靠性高等优点。而且系统有很高的移植性,在企业局域网建设、视频监控等领域有着很好地应用前景。

参考文献

[1]熊远,赵海盟,杨福兴,等.基于I2C总线CMOS成像系统的设计与实现[J].影像技术,2013,(1):47-51.

[2]李修堂.基于FPGA的以太网UDP/IP处理器的设计与验证[D].成都:电子科技大学,2015.

[3]刘喜作,周晶,梁德清.基于UDP的大数据包可靠传输[J].电讯技术,2012,52(1):1-5.

[4]李航.基于FPGA和千兆以太网(Gige)的图像处理系统设计[D].南京:南京理工大学,2014.

[5]沈淦松.基于FPGA的千兆以太网相机的传输系统研究[D].成都:电子科技大学,2013.