一种应用于偏频锁定激光系统的多功能测频电路

2017-05-25白巍凯刘涛董瑞芳张首刚刘娅邓雪陈玖朋高静刘杰

白巍凯,刘涛,董瑞芳,张首刚,刘娅,邓雪,陈玖朋,高静,刘杰

一种应用于偏频锁定激光系统的多功能测频电路

白巍凯1,2,3,刘涛1,2,董瑞芳1,2,张首刚1,2,刘娅1,4,邓雪1,2,陈玖朋1,2,3,高静1,2,刘杰1,2

(1. 中国科学院 国家授时中心,西安 710600;2. 中国科学院 时间频率基准重点实验室,西安 710600;3.中国科学院大学,北京 100049;4. 中国科学院 精密导航定位与定时技术重点实验室,西安 710600)

针对偏频锁定激光系统需要精密频率测量以及频率电压转换等需求,设计了一种基于FPGA(field programmable gate array)的多功能测频电路,实现了抗噪数字转方波电路,在8~20MHz范围内的测频平均误差为0.00156%,具有频率转电压与整数分频功能。目前本测频电路已应用于偏频锁定激光系统之中,将两台激光器的频差从35MHz/h稳定在17kHz/h以内。

频率测量;FPGA;频率电压转换;偏频锁定

0 引言

频率计数是一种对信号频率进行测量的电子技术,在物理研究、通讯技术等领域都有着重要的应用。在开展偏频锁定激光实验[1-2]中,为了达到激光频率的精确计数、频率-电压的线性转换,以及频率信号分频输出等要求,需要实现具有频率-电压转换、50%占空比-任意整数分频的多功能测频电路。

当前已有许多商用频率计和频率电压转换芯片出售,它们可实现在较小的测频周期下达到较高的测频精度,但是由于大多频率计没有频率-电压转换功能,而大多频转压芯片的频率接收范围不够大,均不能达到偏频锁定激光系统的要求。因此,需要自行研制一种专用于偏频锁定系统的多功能测频电路。

关于频率测量的电子技术[3-4]有很多种,根据测频原理主要分为模拟法和计数法。其中模拟法主要有利用无源网络谐振特性的电桥法与谐振法,通过被测信号与已知频率信号相比较的拍频法与差频法等。这些方法[5-6]的测频需要参考信号,频率测量范围受参考信号和器件工作范围限制,范围一般较窄。计数法则主要有电容充放电式与电子计数式两种方法。前者是利用电子电路控制电容器充放电次数,再用磁电式仪表测量充、放电电流的大小,从而指示出被测信号的频率值;后者是根据频率的定义,用电子技术显示单位时间内通过被测信号的周期个数来实现频率的测量。由于数字电路的飞速发展和数字集成电路的普及,电子计数法的应用十分广泛,利用电子计数器测量频率具有精确度高、显示醒目直观、测量迅速以及便于实现测量过程自动化等一系列突出优点。因此,本文采用了电子计数的方法,设计了专门的数字测频电路,以应用于光学系统之中。

数字计数式频率计根据其具体实现算法的特点与用途,主要分为两类:第一类测频范围较窄,大多是定点测频,测量周期较长,但测频分辨率与测量精度极高,能达到10-15量级[7],多用于对时间标准频率的测量工作中;第二类测频范围较宽,测频周期较短,但测频分辨率与测量精度较低,其大多数量级在10-1~10-6范围内[8-12],用于对被测信号频率值的实时测量工作中,如本文设计的测频系统。目前这类频率计中以多周期同步测量法最为常用,此外还有基于DDS的测频法[13]以及全相位FFT测频法[14]等方法。其中基于DDS的测频法每次需先对被测信号进行粗略测量,再调整DDS频率输出之后精细测量,这样对于频率漂移较大的激光系统并不适合,并且其消耗时间较长,不利于反馈控制的应用情况。对于全相位FFT测频法,其测频误差在10-4量级,但其频率测量范围相对较小,同样不能满足激光实验的需要。而多周期同步测量法成熟稳定,在满足实验要求的同时开发难度较小。因此,本文设计的数字测频电路在多周期同步测量法的基础上,做了一些实验应用方面的优化。

目前设计数字测频电路的嵌入式平台主要有ARM[8]、DSP[9]、FPGA[10-12]以及一些低性能的单片机[15]等。本文设计的多功能测频电路采用了能够实现并行处理的FPGA芯片作为主控芯片,模块之间的关联结合了流水线式的设计原理[9]以减小测频系统的工作死区、满足实验的要求。本文首先对测频电路的整体系统进行介绍,包括系统总体设计、系统执行流程和FPGA模块划分;然后,对FPGA内部关键模块的实现原理进行阐述,最后对测试结果及实验应用进行分析。

1 测频电路总体设计

偏频锁定激光实验的系统如图1所示。主激光作为频率参考,将从激光以一定频率差锁定到主激光的频率之上。实验中,利用研制的测频电路测量两台激光器的拍频信号并产生控制信号,通过伺服系统对从激光进行反馈控制,从而实现偏频锁定。由于两台激光器有着较大的相对频率漂移,导致两台激光器的频差变化较大,因此偏频锁定系统分为两级锁定,具体光路如图1所示,虚线部分为光路,实线部分为电路。系统一级锁定通过将两个激光器的拍频信号送至多功能频率计进行频压转换,其输出电压信号经过比例积分微分控制器(proportion integration differentiation,PID)反馈至2号激光器的压电陶瓷换能器(piezoelectric ceramic transducer,PZT)上,以达到抑制相对频率漂移的目的;二级锁定在一级锁定的基础之上进行进一步的频率锁定,实现频率稳定。

注:图中的虚线表示光路部分,实线表示电路部分。

实现系统的一级锁定,即将两台激光器之间的频差稳定在20kHz/h以内,所需要的多功能测频电路需满足以下要求:①测频量程20MHz,以满足较大的激光拍频变化范围;② 电路的测频-转换工作的时间周期可调节,测量周期1 ms时对应测量精度不小于1 kHz,以达到后接模拟PID得到较好的反馈控制效果;③ 实时频率电压转换的线性度优于1%,频压转换的中心频率和范围可调节,并在转换范围为全量程(20 MHz)时分辨率优1 kHz,以达到更高的锁定效果;④ 不影响其他功能的情况下增加任意整数分频功能,用于激光系统的测试实验。

很多测频电路在接收模拟信号时采用模拟电路对正弦信号进行方波转换,进而对方波进行频率测量。这就需要设计一个带宽较大的高增益放大电路。而本文设计的测频电路采用了一种抗噪性较好的数字转方波电路,被测模拟信号直接由AD(analogue-to-digital conversion)芯片进行采集并转换为数字信号之后,采用数字转方波电路将正弦波转换为方波。本文设计采用FPGA(CyClone4-EP4CE15F17C8N)作为平台,该型号内部资源充足。关于测频系统的相关参数,如测频周期、频转压的范围与中心频率等通过矩阵键盘输入。FPGA数据处理之后,在数码管上显示被测信号频率值,并控制DA(digital-to-analogue conversion)芯片输出频转压后的电压信号,以及基于分频系数与被测信号的分频信号。

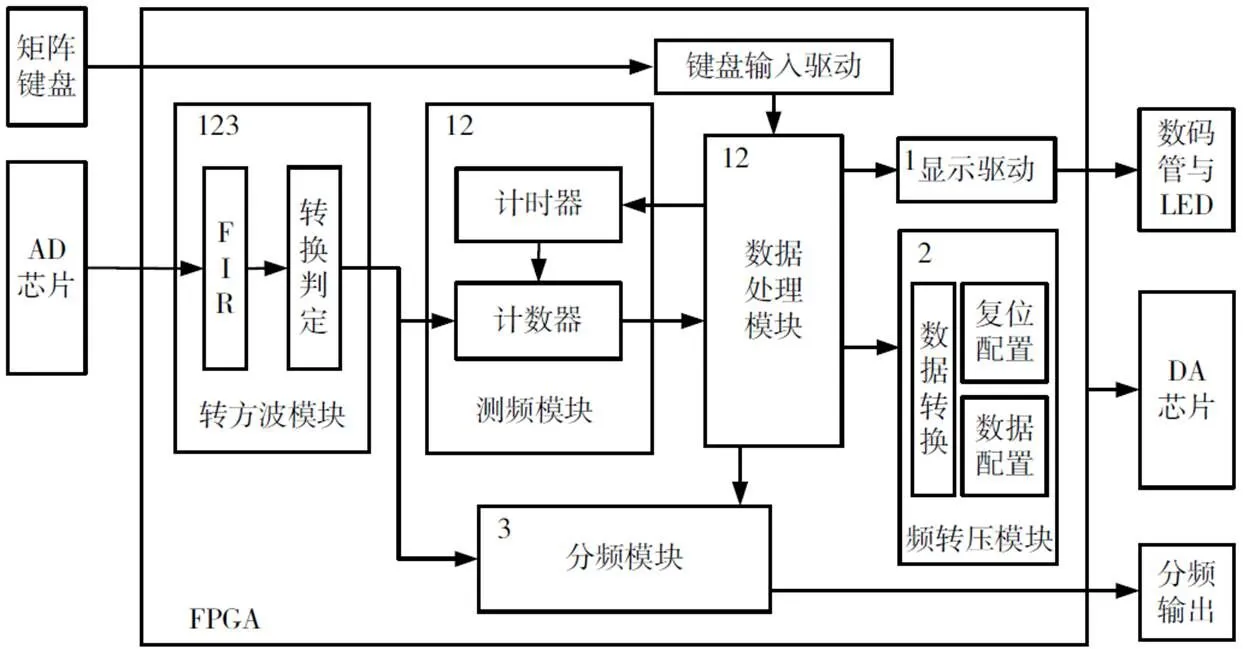

根据系统需要,测频电路的系统结构如图2所示。采用了50 MHz超稳晶振作为系统的参考频率。在FPGA内部,按功能主要由转方波模块、测频模块、数据处理模块、频转压模块和分频模块这5部分组成。均在QuartusII-11.0软件下,使用Verilog 语言进行编程,并通过Modelsim SE-6410.0c进行仿真验证。当信号经过数字转方波处理之后,分为3路(如图2中模块左上标注):① 测频-数据处理-显示-数码管;② 测频-数据处理-频转压运算-电压信号输出;③ 分频-分频输出。

其中第1路完成电路的基本测频功能,第2路完成频率转电压功能,第3路完成任意分频功能。由于FPGA属于硬件设计平台,所以可设计这3路并行执行,同时工作而又不会互相影响。每一路的各个模块之间均采用4次重叠执行的流水线式的结构设计[16],从而使测频模块2次数据测量之间的间隔减小到只有2个系统时钟周期,几乎消除了频率计数的测量死区。

图2 测频电路系统结构图

2 FPGA内部模块的方案实现

2.1 数字转方波模块

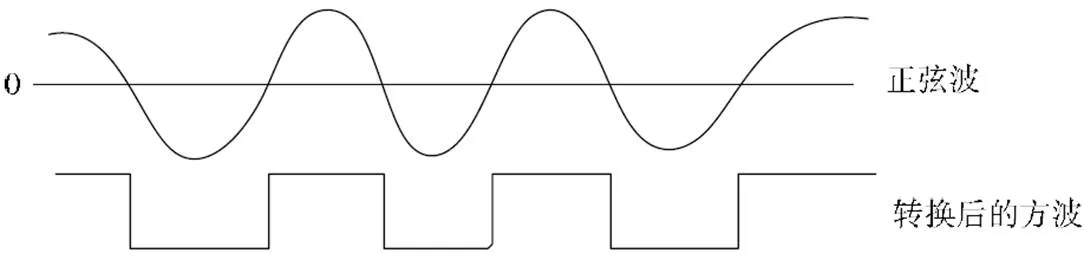

数字转方波模块的作用是将经过AD芯片采集而得的数字正弦信号转换成与其周期相同、计数器可以直接计数的内部方波信号。数字转方波电路的基本原理如图3所示。

图3 正弦转方波原理示意图

理想状态下设输入正弦波的波腹值为0。将0设定为判定阈值对接收到的数据进行判定,当数据≥0时,输出方波为高电平;当数据<0时,输出方波为低电平。但在实际中,电路系统中有噪声的存在:一部分来自于中路的白噪声;另一部分来自于AD芯片的转换噪声。本文设计所采用的AD9280芯片工作在32MHz时转换误码率0,本文设计所采用的系统时钟频率为50MHz,会增加AD芯片的转换误码率(CER)与功耗。这种情况下使用上述判定方法会使输出的方波产生较多毛刺,导致过大的测频误差,如图4所示。

针对噪声的影响,模块中会用两个措施对其进行抑制。

首先,在模块内加入有限长单位冲激响应(finite impulse response,FIR)滤波器。由于白噪声和转换误码带来的噪声都是随机的,所以它们在频谱分布上基本是在所有频域之上。因此,将AD采集到的数据先通过一个低通数字FIR滤波器就可以消除部分噪声。本滤波器40MHz、9阶低通滤波器,抽头系数由Matlab计算得到。

图4 正弦转方波噪声示意图

其次,在判定部分中采用状态机代替普通的逻辑判定,并提高判定阈值。如图5所示,设阈值为a,状态机起始状态输出信号为低电平,当数据>a时,进入下一个状态并将输出信号拉高,等数据<-a时,状态机返回初始状态并将输出信号拉低。这样基本上解决了出现毛刺的现象。该数字转方波电路不仅适用于正弦波,对三角波、锯齿波一样有效。我们采用Modelsim软件进行仿真,分别以叠加噪声的正弦波、锯齿波、三角波作为数字转方波模块的输入AD,B_Out为经过以上两种措施改进的数字转方波模块的输出,A_Out为未经改进的模块输出。仿真图如图5所示,经过改进后的数字转方波模块,已经成功消除了毛刺出现的现象。

(a) 正弦波

(b) 锯齿波

(c) 三角波

2.2 测频模块

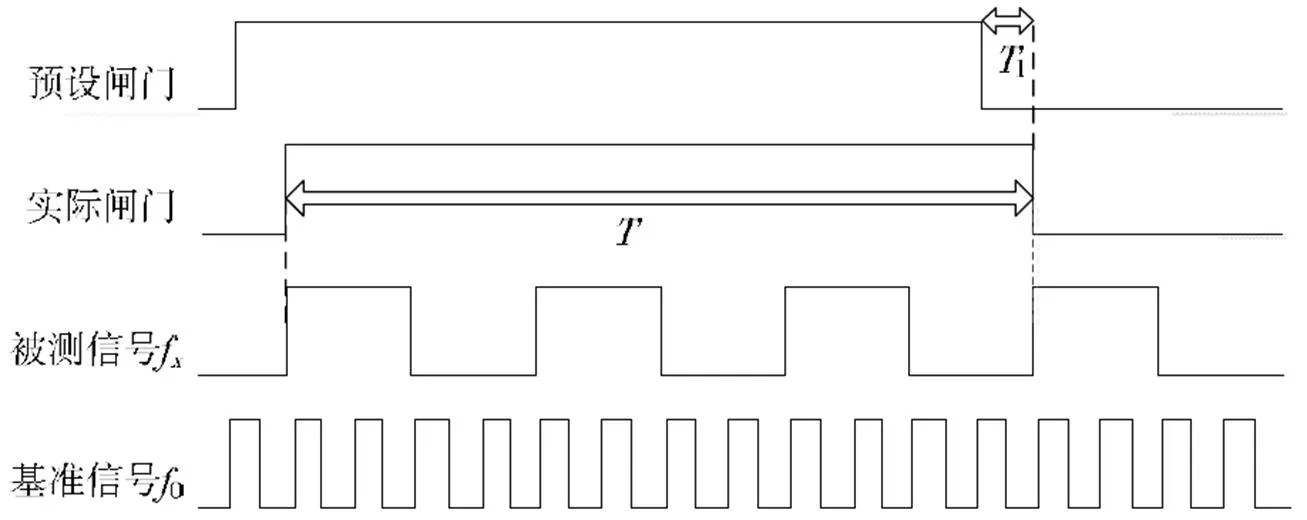

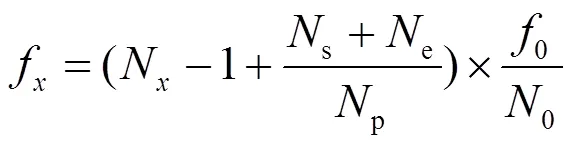

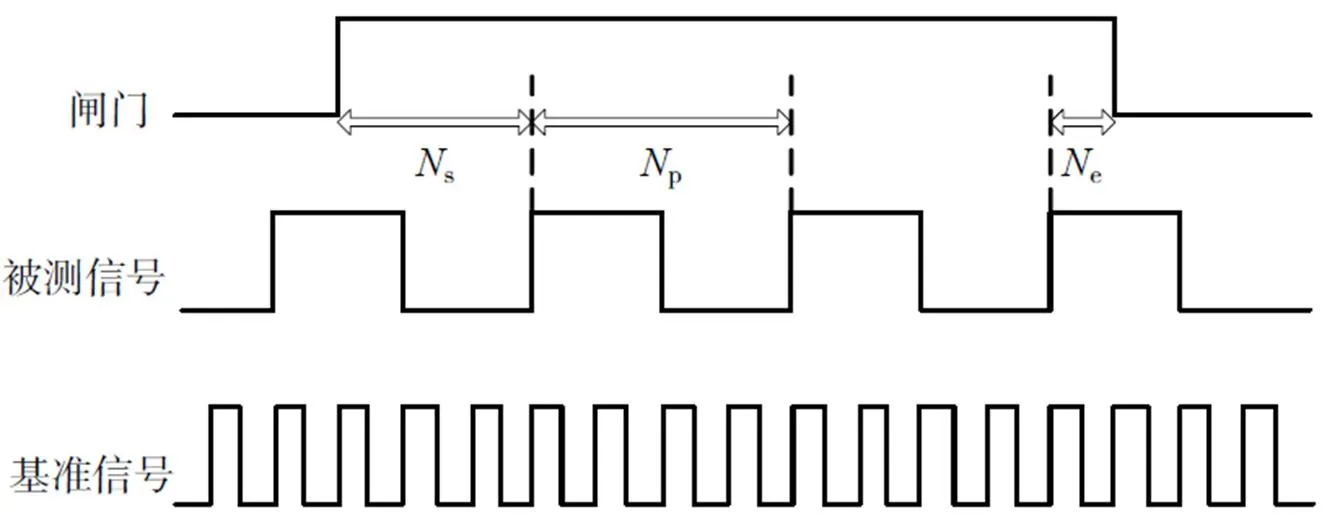

常见的测频算法以多周期同步测量法最为人知,又名等精度测量法,该方法目前非常成熟,并广泛应用于测频系统的设计当中。这类算法是基于直接测频算法而得,虽然具有“测频周期越短,频率分辨能力越小”的缺点,但其方法相对简单、易于程序实现,并且频率分辨率能够满足偏频锁定系统中抑制频率漂移的要求,所以本文设计采用该算法,并在该算法基础上加以优化,使其更适用于锁定系统当中。关于算法的具体内容在文献[10]和[17]中有详细的介绍,以下只做简单的介绍。由等精度测频法的示意图6可见,除了被测信号作为输入信号外,还有一个确定频率的基准信号,在实际闸门开放的时间内对它们进行计数。设对基准频率信号的计数结果是,其周期为;对被测信号的计数结果,其周期为,则有等式:

推导得到被测量的信号频率是

。(2)

图6 等精度测频原理示意图

因此,根据系统应用的需求,本次设计在等精度测频法之上做了以下优化:① 将预置闸门作为实际闸门;② 加入周期测量计数器、前置计数器、后置计数器。修改后的测频原理如图7所示。做第1步修改,使得闸门开启后到测频计数完成输出结果之间的时间为确定值,去掉了不确定值,但是会给频率计数带来一个±1的误差。为了对这个误差进行补偿,需要做第2步修改。以基准频率为标尺,加入周期测量计数器测量被测信号两个上升沿之间的间隔;加入前置计数器用于测量在闸门开启后第1个被测信号的上升沿与闸门信号上升沿之间的时间间隔;加入后置计数器用于测量闸门关闭前与最后一个被测信号的上升沿与闸门信号下降沿之间的时间间隔。由于最后关闭闸门时,被测信号并没有传送一个完整周期的波形,所以测得的结果需要减1,即。加入误差补偿后的被测信号频率如下:

。 (4)

所有的数据计算部分均在数据处理模块内进行,测频模块将测得的各个参数传送至数据处理模块便完整其功能。

图7 改进后的测频原理示意图

2.3 频压转换模块

频转压模块接收到中心频率、测频范围等参数后,通过数模转换芯片完成频率与电压的线性转换。因为项目要求转换范围等于测频量程(20MHz)时,频压转换分辨率必须优于1kHz,所以采用了16位DA转换芯片,芯片型号为DAC8562,输出范围0~2.5V。FPGA与DA通过SPI协议[18]进行通信,所以此模块包含两个部分:一部分用于对频压转换进行计算;另一部分完成SPI命令发送,将计算得到的结果采用原码并结合命令控制字发送至DA,使DA更新输出电压。

在第1部分中,关于频压转换的计算公式如式(5)~(8)所示:

。 (6)

。 (8)

第2部分是一个SPI协议发送模块,FPGA与DA芯片通信的数据一帧为24bits(MSB)。其中高8位是DA的控制命令,低16位为之前模块计算所得的16位数据,通过三线式SPI协议发送至DA芯片。

其他模块主要包括显示驱动模块、分频模块[19]、数据处理模块等。其中数据处理模块的功能主要是协调各个模块进行运算处理。分频模块主要在基于累加器原理的基础上做了优化,使整数分频输出信号具有50%占空比。目前这些模块的技术原理已经比较成熟。

3 测试结果及实验应用

3.1 测试结果

我们对多功能测频电路进行了频率测量功能、频率-电压转换功能及分频功能测试。

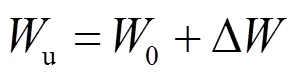

首先用多功能测频电路测量由信号发生器(SRS,SG382)输出的正弦信号,读取数据并进行误差计算。因为测频功能的频率分辨率与设定的测量周期有关,测量周期越长频率分辨率越高。为了排除频率分辨率的影响,更准确的得到测量误差,将测量周期设定为1s。每隔1s测量1次,每组数据测量50次,进行平均后计算其残差,如图8(a)所示。测量平均误差为0.0027%,置信区间为(0,0.00765%)。其中在8~20 MHz的测量平均误差为0.00156%,置信区间为(0,0.000216%)。

然后,对多功能测频电路的频率-电压转换功能进行测试。设置频率计的频压转换参数为:中心频率10MHz、范围8~12MHz,电压输出范围为0~2.5V。根据理论计算,我们得到频率与输出电压的关系为

式(9)中,为频率,取值范围8~12 MHz。

在实际测试中,使信号发生器(SRS,SG382)输出信号的调制参数测频电路频压转换的参数设置一致,调制频率为1Hz的正弦波。采用频率计数器测量信号发生器输出频率,并用示波器对测频电路的输出电压信号进行捕捉,经拟合后得到函数:

。 (11)

由此可得测频电路输出电压与输入信号的频率具有良好的线性关系,满足线性度优于1%的实验要求。

最后,对多功能测频电路的分频功能进行测试。对信号发生器发出10MHz正弦波信号进行分频,依次改变频率计的分频系数,通过另一台商用频率计(Agilent,53230A)测量其分频后的频率,计算其误差比。其误差比的平均值为1.77×10-11,置信区间为(0,3.638×10-11),如图8(c)所示。

(a) 测频残差图

(b) 频率-电压转换残差曲线

(c) 分频误差图

对各项测试结果进行误差分析:① 测频误差在算法上由测频周期与基准信号频率两因素决定[5];② 在FPGA内部数据处理中,由数字化带来的量化误差对低频测频误差影响较大;③ 在实际电路中,FPGA时钟源采用的是有普通源晶振,其稳定度也会对测频误差造成一定影响;④ 测频误差、DA电路部分模拟噪声也会对频率-电压转换的线性度有一定影响;⑤ 分频误差主要取决于测频误差。

3.2 实验应用

目前此多功能测频电路已应用于偏频锁定系统的一级锁定中,偏频锁定激光系统如图1所示。两台激光器的中心波长均为1550nm,频率在193.5THz左右。其中主激光锁定在超高精细度光学腔上的窄线宽激光器,其线宽小于3Hz,频率漂移每秒千赫兹量级;从激光是一台商用光纤激光器(NKT,Basic),输出激光线宽在千赫兹量级。由于光电探测器无法直接响应激光光频范围的信号,所以从激光与主激光的输出光先通过光纤输出,在光纤内进行拍频。拍频所得的光频信号中包含两激光器频差的信息,通过光电探测器将频率差值转换成频率相同的电压信号之后,传至多功能测频电路进行测频与频压转换。经过测频电路频压转换后的信号再传输至模拟PID进行控制运算,输出控制信号对从激光的PZT进行反馈调整,从而抑制两台激光器的相对频率漂移,达到偏频锁定系统一级锁定的目标。

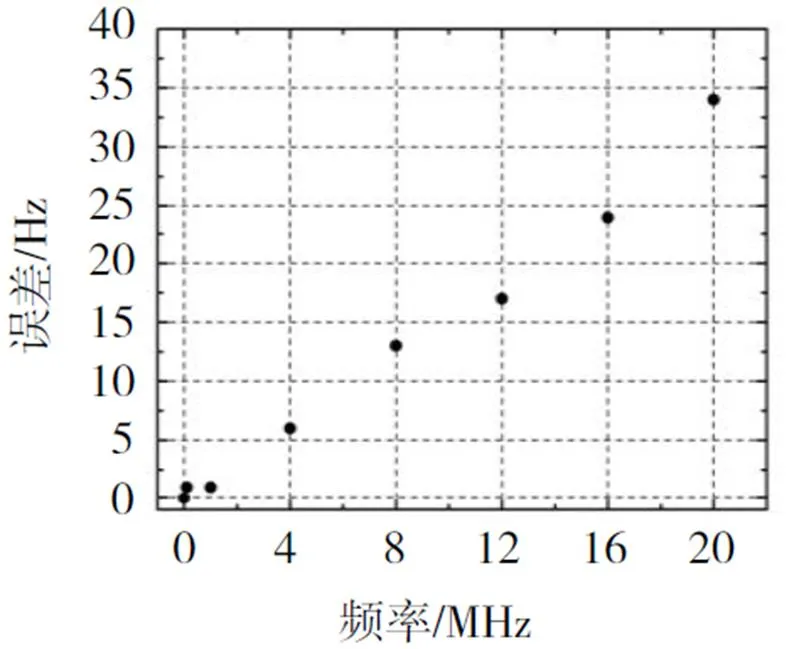

系统要求一级锁定后频差稳定在20kHz/h以内。由于频率漂移本身是随机的,并且受环境温度、震动等影响较大,所以激光系统没有进行锁定时拍频所测的频率差会随机变化,并在较大的时间范围内(24h)上下起伏,频率漂移每小时约几十兆赫兹。本次测量采用商用频率计(Agilent,53230A)实时记录拍频信号的频率。将多功能测频电路的频转压中心频率设定为10.14MHz,即将从激光频与主激光的频率差锁定在10.14MHz。测量分为两组,分别对激光系统未锁定与锁定状态下的频差信号进行1h的记录测量。

首先我们关闭频率计与模拟PID,对未锁定时1h内拍频信号的频率值进行测量记录。测量结果如图9(a)实线所示,频率变化范围在35MHz左右。在这样的频率变化条件下无法进行下一步实验,必须通过一级锁定进行频率漂移抑制。其次开启模拟PID,使用本文设计的多功能测频电路进行一级锁定后,再次对拍频信号频率值进行测量,测量结果如图9(b)所示,其中一个小时内频率漂移了5.7kHz,短期频率抖动小于17 kHz,基本达到了1h内频差<20kHz的设计目标。

注:图(a)中的实线表示激光系统未锁定时的数据,虚线表示激光系统使用频率计锁定时的数据。

4 总结

本文从偏频锁定激光实验的需求出发,设计并实现了一种基于FPGA的多功能测频电路,其参考频率为50 MHz,测频、频转压量程为0~20 MHz。该测频电路采用了一种抗噪性较好的数字正弦转方波电路,在8~20MHz范围内的测频平均误差为0.00156%,具有频率转电压与整数分频等功能。对此多功能测频电路的频率测量功能、频率-电压转换功能以及分频功能分别进行测试,其中测频误差平均0.002%、频压转换线性度0.3%。此测频电路目前已成功应用于偏频锁定激光实验之中,将两台激光器频差从35 MHz/h稳定在17kHz/h以内,基本实现了抑制激光器慢漂的作用。

[1] HUGHES J, FERTIG C. A widely tunable laser frequency offset lock with digital counting[J]. Meeting of the Aps Division of Atomic, 2009, 79(10): 103104-103104-7.

[2] THORPE J I , NUMATA K , LIVAS J. Laser frequency stabilization and control through offset sideband locking to optical cavities[J]. Optics Express, 2008, 16(20): 15980-15990.

[3] 张永瑞, 刘振起, 杨林耀. 电子测量技术基础[M]. 西安: 西安电子科技大学出版社, 2005.

[4] 朱余荣, 黄清用. 短弧焊用无源截波式短路频率计[J]. 焊接, 1981, 4(1): 32-35.

[5] 张汉生. 低频模拟频率计的研究[J]. 大连铁道学院学报, 1990, 11(2): 57-61.

[6] 古天祥. 电子测量原理[M]. 北京: 机械工业出版社, 2004.

[7] 刘娅. 虚拟化差拍频率计的研究与设计[D]. 西安: 中国科学院国家授时中心, 2007.

[8] 薛巨峰, 关子钧, 刘彬. 基于ARM7的高精度频率计的设计[J]. 电子测量技术, 2015, 18(1): 60-63.

[9] 史洪玮, 王紫婷,宁平, 等. 基于DSP的数字复合频率计设计[J]. 计算机与数字工程, 2011, 39(4): 179-181.

[10] 高锐. 基于FPGA的多周期同步频率计设计[D]. 吉林: 吉林大学, 2013.

[11] 毛智德,吕善伟. 基于FPGA的等精度频率计设计[J]. 电子测量技术, 2006, 29(4): 85-86.

[12] 潘松. CPLD/FPGA在电子设计中的应用前景[J]. 电子技术应用, 1999, 7: 6-8.

[13] 白丽娜, 周渭. 一种和DDS结合的高分辨率频率计设计[J]. 西安电子科技大学学报, 2013, 39(4): 126-130.

[14] 任丽棉. 基于全相位FFT的高精度频率计系统研制[D]. 天津: 天津大学, 2009.

[15] 李国立, 刘旭明, 翟力欣. 基于FPGA与单片机的等精度频率计的设计[J]. 电子设计工程, 2013, 21(22): 171-177.

[16] 吴继华, 蔡海宁, 王诚. Altera FPGA/CPLD设计(高级篇) [M]. 2版, 北京: 人民邮电出版社, 2011: 11-25.

[17] RUBIOLA E. High resolution time & frequency counters[R]. FEMTO-ST Institute, CNRS and Université de Franche Comté, 2012.

[18] Texas Instruments. DAC8562 Datasheet-Texas Instruments[OL]//(2011-06-01)[2016-02-03]. http://www.alldatasheet.com/ datasheet-pdf/pdf/419925/TI1/DAC8562.html.

[19] 常兴旺, 李孝辉, 王玉兰, 等. 基于FPGA的小数分频法的研究与设计[C] //第十九届测控、计量、仪器仪表学术年会, 广西: 中国电子学会电子测量与仪器分会委员会, 2009: TN772.

A multi-functional frequency measurement circuit for laser frequency offset locking system

BAI Wei-kai1,2,3,LIU Tao1,2, DONG Rui-fang1,2, ZHANG Shou-gang1,2, LIU Ya1,4,DENG Xue1,2, CHEN Jiu-peng1,2,3, GAO Jing1,2, LIU Jie1,2

(1. National Time Service Center, Chinese Academy of Science, Xi’an 710600, China;2. Key Laboratory of Time and Frequency Primary Standards, National Time Service Center,Chinese Academy of Sciences, Xi’an 710600, China;3. University of Chinese Academy of Sciences, Beijing 100049, China; 4. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center, Chinese Academy of Sciences, Xi’an 710600, China)

According to the requirements of precision frequency measurement, conversion from frequency into voltage, and so on, for laser system with frequency offset locking, this paper demonstrates a multi-functional frequency measuring circuit based on FPGA. By using the low noise digital square wave switching circuit, the average error for the developed frequency meter in the frequency measurement within 8MHz to 20MHz is 0.00156%, and it has the functions of frequency-voltage conversion and integer frequency division. The frequency measuring circuit has been applied to the frequency offset locking laser system, and has reduced the frequency difference between the two lasers from 35MHz/h to 17kHz/h.

frequency measuring; FPGA; conversion from frequency into voltage; frequency offset locking

P127.1+2

A

1674-0637(2017)01-0001-10

10.13875/j.issn.1674-0637.2017-01-0001-10

2016-05-16

国家自然科学基金委重大科研仪器设备研制专项(61127901);国家自然科学基金资助项目(11273024,6102502,11403031);中组部“青年拔尖人才支持计划”项目(组厅字〔2013〕33号);中国科学院科技创新“交叉与合作团队”资助项目(中国科学院人教字〔2012〕119号);中国科学院重点部署资助项目(KJZD-EW-W02)

白巍凯,男,硕士,主要从事光频传递实验中数字电路研究。