基于FPGA的数字化多道脉冲幅度分析器的设计

2017-04-24罗翔岳爱忠王茂林何绪新何子忠林岩栋

罗翔, 岳爱忠, 王茂林, 何绪新, 何子忠, 林岩栋

(1.中国石油集团测井有限公司, 陕西 西安 710077;2.中国石油天然气集团公司测井实验基地, 陕西 西安 710077)

0 引 言

核测井仪器能谱数据探测[1]处理最为关键的多道脉冲幅度分析器,其设计的优劣以及运行效果直接影响最终测试结果。早期的多道脉冲幅度分析器一般采用DSP或者MCU进行设计[2],运行处理速度较慢,并且因其顺序处理机制,会造成能谱漏计数。随着高速模数转换器和集成处理电路的快速发展,能谱测量分析技术也正在进入高速数字化处理阶段。目前,中国也有很多通过高速数字化进行多道分析器的研究,但是因其存在高速处理下配合机制不完善等原因,得到能谱的分辨率、稳定性等方面,与国外处理技术相比还有很大差距。

为了解决上述问题,本文设计了基于FPGA[3]的多道脉冲幅度分析器[4],完整地提出了一种高性能整体设计方案。通过高速ADC对随机快速的核脉冲信号进行采样,将数字化后的核脉冲信号进行捕获、有效信号判断、峰值判断,并进行信号幅度分析、数据通讯等处理,各个处理模块并行运行、交错处理,从而保证获取的能谱数据精准无误、谱形光滑、谱峰明显,分辨率能够接近探测器晶体的最佳分辨率。由于数字信号处理具有很强的抗干扰能力和灵活性,使得基于FPGA的数字化多道脉冲幅度分析器能够很好地应用于测量环境相对恶劣的石油测井行业核测井领域中。

1 核信号特征

在核测井核辐射测量中,需要采用探测器对核辐射射线进行探测,探测器由晶体和光电倍增管组成,晶体一般采用NaI、CsI或者BGO晶体,本文提出的基于FPGA的多道脉冲幅度分析器[5]所应用的自然伽马能谱测井仪器采用CsI晶体。探测器对核辐射射线进行探测,能够输出有效的核脉冲信号,为负脉冲信号,核辐射射线能量的不同,会对应输出幅度不同的核脉冲信号。探测器之后通常需要采用前置放大器对输出的核脉冲信号进行滤波放大,然后需要将信号送入主放大电路进一步滤波放大,并且进行信号反向,以便进行多道脉冲幅度分析器信号采样以及信号处理。在自然伽马能谱测井仪器中,通过电路滤波放大处理后得到的核信号上升时间不到1.6 μs,信号宽度约6 μs的脉冲信号。

2 系统设计原理

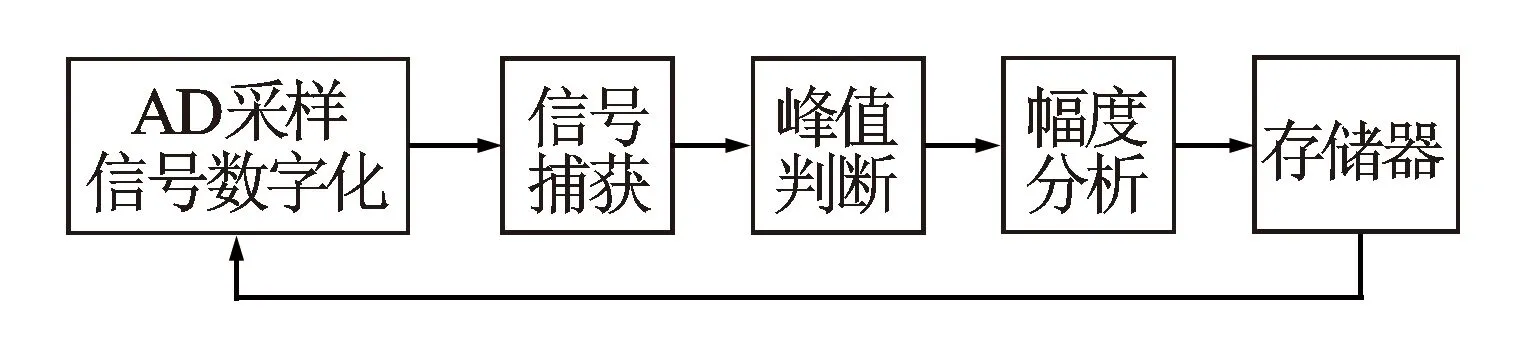

基于上述分析,为了对核探测器输出的宽度过窄的核脉冲信号进行高速、高效地能谱分析处理[6],提出了一种基于FPGA的多道脉冲幅度分析器。图1为多道脉冲幅度分析器的系统设计原理框图。

图1 多道脉冲幅度分析器原理框图

核脉冲信号到达后,通过高速ADC采样将模拟脉冲信号转换为数字信号[7]并即刻对其进行捕获,然后立即进行脉冲信号峰值判断,该多道脉冲幅度分析器对原始脉冲信号进行连续不间断采样,并同时进行信号峰值判断,结果存入缓冲区,并根据每个采样点判断结果更新缓冲区数据,在单次信号采样完成时,即刻得到信号峰值结果数据。对脉冲信号幅度进行分析,在存储器中对当前脉冲幅度分析数据进行记录,这样就完成了对1个脉冲信号的分析处理。

因FPGA其并行处理机制,在上述信号分析处理的同时,继续进行不间断采样,对后续到来的脉冲信号进行同样的脉冲幅度分析。对于不同幅度的脉冲信号,就对应了存储中不同的存储单元,从而对存储器不同存储单元的内容进行处理,实现多道处理。

以存储器的不同地址作为道址,而每个地址单元里的内容就是不同幅度的脉冲信号的计数。以道址作为横坐标,脉冲信号计数作为纵坐标,则可以得到1张能谱,即实现了多道脉冲幅度分析器。

3 硬件电路设计

根据上述系统原理框架,提出了一种基于FPGA的多道脉冲幅度分析器硬件电路设计方案[8],其主要由ADC高速采样电路和FPGA信号分析处理电路组成。

3.1 ADC采样电路

ADC采样电路采用高速模数转换器件AD9235进行电路设计,该器件为12 bit高速ADC芯片,最高可以实现4 096道能谱处理,其采样速度可以达到20 Ms/s,图2给出了ADC采样电路的具体设计。

该ADC采样电路信号输入端设计为单端输入,以匹配核脉冲信号,并且信号输入端加入RC滤波电路,对采样前的脉冲信号再次进行滤波处理,减小信号上的噪声干扰。该采样电路由FPGA提供20 MHz时钟对其进行时序控制,完成高速采样,然后根据控制时钟时序输出12 bit数字信号送至FPGA进行信号分析处理。该电路还可以由FPGA控制其进行掉电处理,在不需要进行信号采样时减小电路功耗。采样电路可以对模拟脉冲信号进行高速采样,分辨率高,可减少信号丢失,提高信号采样的准确性。

图2 ADC采样电路

3.2 FPGA处理电路

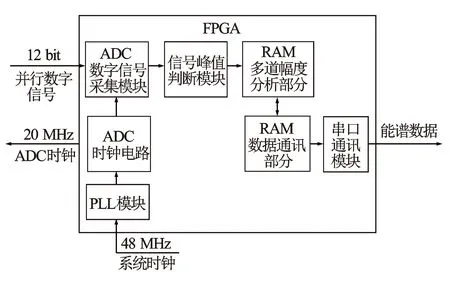

FPGA处理电路为实现多道脉冲幅度分析器最关键的部分,采用现场可编程门阵列器件A3P250进行电路设计,该处理器件内部可运行高速时钟,且内部含有PLL,可方便得到内部各个模块所需要的不同时钟,并且内部有大容量RAM模块,为实现多道脉冲幅度分析器提供基础。

FPGA处理电路由晶振提供48 MHz高速时钟,使其能够对数据进行高速处理,并且由于FPGA的运行机制是并行处理,可以使FPGA内部各个模块在互不干扰的情况下高速并行运行,处理速度更快。

该FPGA处理电路内部设计了多个处理模块用于功能实现,采用A3P250内部PLL模块提供16、20、24 MHz时钟给内部各个功能模块,用于时序控制。通过设置内部深度256、宽度16的双端口RAM模块用于能谱数据的存储,各个模块之间协调处理,完成多道脉冲幅度分析器处理功能的实现。该处理电路内部再设计一个串口模块用于与外部进行通讯,完成能谱数据的传输。

图3 FPGA处理电路内部处理结构框图

图3为FPGA处理电路内部处理结构框图。其内部通过PLL模块提供20 MHz的ADC时钟,对ADC数字信号采集模块进行时序控制,对外部输入的12 bit并行数字信号进行捕获。然后通过信号峰值判断模块获取信号幅度值,随即通过RAM模块的控制完成多道幅度分析。各个功能模块协调处理,同时各自也独立并行运行,而在另一个并行处理的过程中,通过另一个RAM模块的控制获取完成多道脉冲幅度分析后缓存的能谱数据,并且通过串口通讯模块完成能谱数据发送。

4 软件数字化设计

基于上述设计的硬件电路,能够使数字化多道脉冲幅度分析器的主控软件在FPGA主控器件A3P250中进行功能实现。软件设计主体包括信号捕获模块、信号峰值判断模块、有效信号判断模块、脉冲幅度分析模块以及片内RAM存储器模块,并且设计串口模块进行外部串口通讯。

4.1 脉冲信号捕获及判断模块

通过设置FPGA内部PLL模块产生20 MHz时钟,并通过端口配置将20 MHz时钟输出至高速ADC控制其进行核脉冲信号高速采样,然后在内部通过该时钟进行时序控制捕获从外部高速ADC采样后回传的12 bit并行数字信号,完成核脉冲信号数字化捕获。

脉冲信号峰值判断模块中,在脉冲信号时序控制捕获的同时,通过门槛设置判断脉冲信号是否到达,如果信号到达并触发门槛,则即刻对信号幅度变化进行判断,将判断结果存入信号峰值缓冲区,并根据每次采样判断的结果与信号峰值缓冲区数据进行对比,更新缓冲区数据。在一个完整的脉冲信号结束并反向触发门槛后,则在信号峰值缓冲区中能够得到该脉冲信号正确的幅度值。并且在脉冲信号峰值判断的同时,对当前采样脉冲信号宽度进行记录。

该方法直接对原始脉冲信号进行高速数字化采样并进行判断处理,不进行峰值保持或者信号变换,数字化后的信号能够完全还原原始脉冲信号特征信息,从而获取到真实的脉冲信号峰值等信息,不会因为信号变换可能造成信号畸变失真,而造成获取到的信号特征信息异常。

在模块协调处理获取到脉冲信号峰值后,立即通过信号宽度以及幅度特征进行有效信号的判断;如果判断为干扰信号,则放弃该脉冲信号峰值数据,继续进行后续脉冲信号采样以及判断;如果判断为有效信号,则进行脉冲幅度分析。

4.2 多道脉冲幅度分析及RAM存储器模块

为了成功实现数字化多道脉冲幅度分析器,需要在FPGA内部设置关键的RAM存储器模块。该RAM设置为双端口RAM,深度设置为256,数据宽度设置为16。双端口RAM分为A、B端口,都可对该RAM进行读写操作,A端口设置为时钟上升沿触发,用于RAM写操作,B端口设置为时钟下降沿触发,用于RAM读操作。在脉冲幅度分析处理模块中,将该双端口RAM实例化为2个RAM模块,一个用于脉冲幅度分析256道能谱数据存储,而另一个则用于缓冲完成的能谱数据的发送操作。

当脉冲信号捕获及判断模块成功获取到脉冲信号幅度值并且信号有效,则触发脉冲幅度分析模块进行数据处理,通过内部时钟对2个RAM模块中当前用于脉冲幅度分析的RAM模块进行控制,在时钟下降沿时通过B端口触发该RAM模块,查找RAM存储器中脉冲幅度对应地址,读取存储单元数据并进行脉冲计数累加,然后在时钟上升沿时通过A端口触发该RAM模块,在RAM存储器中相同地址处将累加的数据重新存入存储单元,从而完成脉冲幅度分析。在一定时间后,RAM存储器模块中就能够得到256道能谱数据。图4为脉冲幅度分析处理流程。

图4 脉冲幅度分析处理流程图

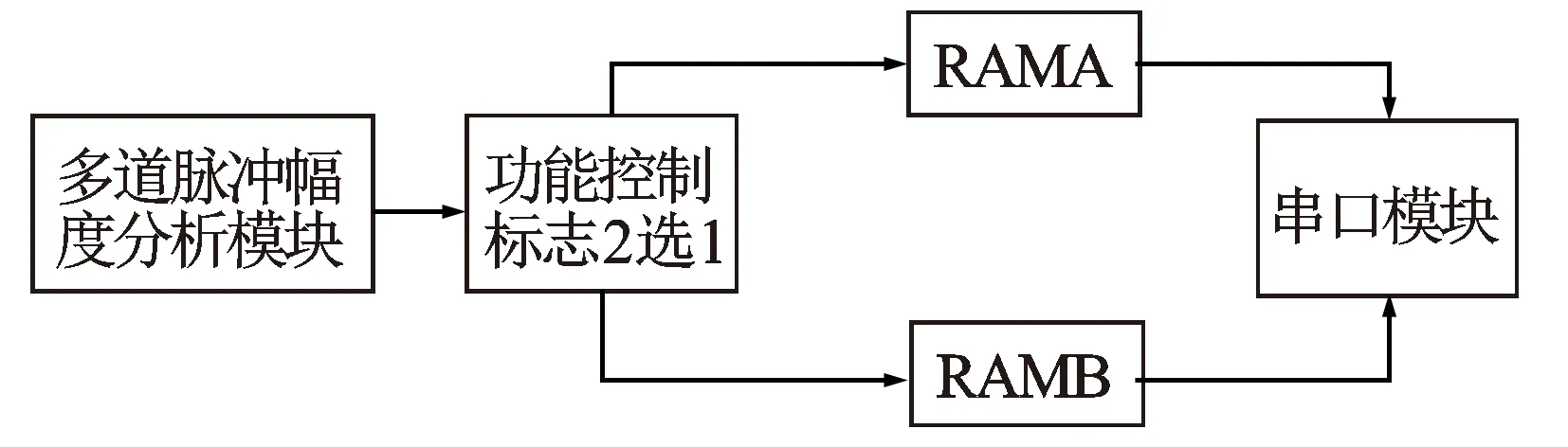

4.3 串口模块

对于上述分析的脉冲幅度分析模块,其处理得到的能谱数据需要传输至外部其他控制处理电路,因此在FPGA软件中设计串口模块,通过时序控制将脉冲幅度分析缓冲于RAM存储器模块中的能谱数据通过串口通讯发送至外部。根据图5中RAM存储器的设置,通过时钟对2个实例化的RAM模块中另一个用于数据通讯的RAM模块进行控制,在时钟下降沿时通过B端口触发该RAM模块,读取存储器中缓冲的能谱数据,并在时钟上升沿时通过串口模块内部控制过程完成能谱数据发送。

该串口模块以及其控制使用的RAM模块与上述多道脉冲幅度分析所控制的RAM模块交错并行处理,该方法可实现多道脉冲幅度分析处理过程与数据通讯过程互不影响,实现脉冲幅度分析无漏计数。

图5 交错并行处理原理框图

图5为串口模块与多道脉冲幅度分析模块交错并行处理的原理框图。通过功能控制标志选择,当多道脉冲幅度分析模块控制RAMA模块进行分析处理时,串口模块则控制RAMB模块进行完成缓冲的能谱数据的发送。反之,则通过功能控制标志进行交换控制,实现控制处理模块之间的交错并行处理。

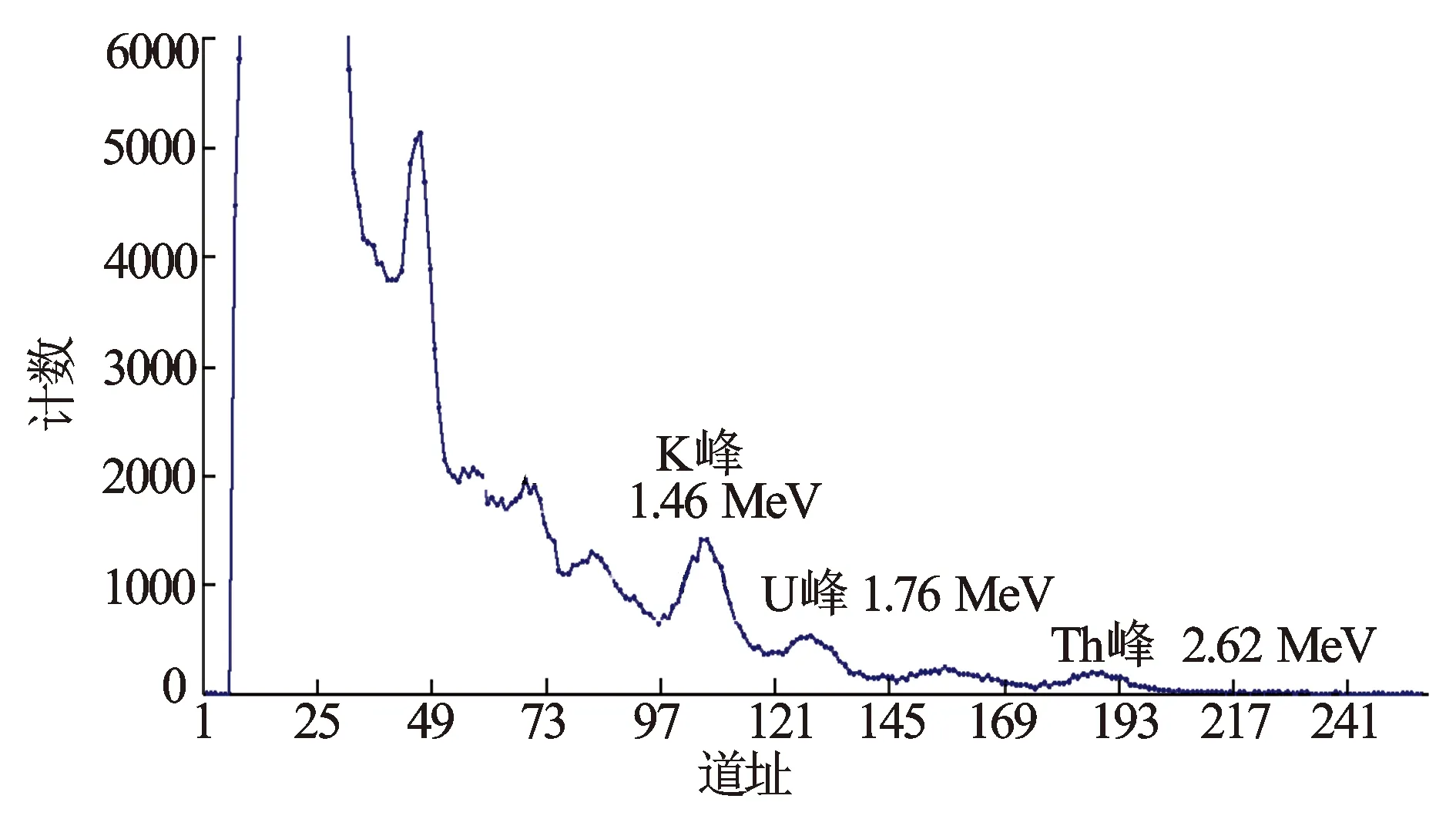

图6 自然伽马能谱测井仪器刻度器测试能谱图

5 应用效果

本文设计的多道脉冲幅度分析器成功应用于自然伽马能谱测井仪器等核测井仪器中,将探测器输出的核脉冲信号高速、高效地进行幅度分析并转换为能谱数据上传至地面分析,得到的能谱数据效果完全满足仪器要求,图6为自然伽马能谱测井仪器使用刻度器测试得到的能谱图。

(1) 得到的能谱谱形光滑,其中自然伽马能谱所需要的特征峰K峰(1.46 MeV)、U峰(1.76 MeV)以及Th峰(2.62 MeV)明显,计数率也相应提高;

(2) 整体能谱中各个谱峰分布正确,能量线性准确,K峰(1.46 MeV)保持在105道,U峰(1.76 MeV)对应保持在127道,而Th峰(2.62 MeV)对应保持在188道;

(3) 能谱分辨率也相应提高,K峰(1.46 MeV)分辨率可以达到9.5%。

6 结 论

(1) 设计了基于FPGA的数字化多道脉冲幅度分析器,在FPGA中进行软件数字化设计实现脉冲信号捕获、判断以及脉冲幅度分析与能谱存储,同时设计了串口模块进行外部通讯。并且在时序设计上采用交错并行处理,实现能谱分析无漏计数。

(2) 该数字化多道脉冲幅度分析器采用ADC+FPGA架构,电路设计简单,可靠性更高, 并且其尺寸可以满足小直径核测井仪器要求。其数据处理灵活,可以通过高速时钟控制完成高速并行处理,得到满足要求的能谱数据。该多道脉冲幅度分析器主要由数字电路组成,抗干扰能力强,能够很好地适应石油测井的恶劣环境。

参考文献:

[1] 张软玉. 数字化核能谱获取系统的研究 [D]. 成都: 四川大学, 2006.

[2] 敖奇, 魏义祥, 文向阳. 基于DSP的数字化多道脉冲幅度分析器设计 [J]. 核技术, 2007, 30(6): 532-536.

[3] 周立功. Actel FPGA原理与应用 [Z]. 广州: 广州致远电子有限公司, 2010.

[4] 刘洪斌, 梁福田, 李锋, 等. 基于无线局域网的多道脉冲幅度分析器 [J]. 核电子学与探测技术, 2014(4): 429-432.

[5] 王彦, 贺康政, 黄松. 基于FPGA的多道脉冲幅度分析器的设计 [J]. 核电子学与探测技术, 2005(4): 416-419.

[6] LIMA J, HERMAN P, GUEDES, et al. A Fast Multichannel-analyzer for Radiation Detection Applications [J]. IEEE Transactions on Instrumentation and Measurement, 2004, 53(2): 378-383.

[7] ROBERT GRZYWACZ. Applications of Digital Pulse Processing in Nuclear Spectroscopy [J]. Nuclear Inst. and Methods in Physics Research, B, 2003, 204(1): 649-659.

[8] 蔡顺燕. 数字多道脉冲幅度分析器的硬件电路设计 [J]. 核电子学与探测技术, 2010(3): 354-356, 421.