多核DSP和FPGA之间的高速SRIO通信

2017-04-19汪安民韩道文徐焱

汪安民,韩道文,徐焱

(1.同方电子科技有限公司研究所,九江 332009;2.电子工程学院;3.哈尔滨工业大学)

多核DSP和FPGA之间的高速SRIO通信

汪安民1,韩道文2,徐焱3

(1.同方电子科技有限公司研究所,九江 332009;2.电子工程学院;3.哈尔滨工业大学)

在高速采样系统中,大量数据需要实时传输到处理器。尤其是系统中存在多个处理器协同工作,就需要高速的总线来交换数据。SRIO总线由于存在连线少、传输速度高等优点,使用较为广泛。本文介绍了多核DSP和FPGA之间使用SRIO进行数据交换的软硬件设计方法,在不同数据需求下,介绍了FPGA将数据直接传输到DSP的DDR3、片内RAM或者多核的共享RAM中。本文研制了硬件系统,给出了各种方式的软件操作方法和实际硬件平台验证,SRIO传输速率达到4 Gbps。

多核处理器;SRIO;共享RAM

引 言

大规模集成电路的高速发展,使得处理器的能力越来越强,进而处理的事件增多;大数据的应用,使得高速宽带采样成为必然,高速采样每秒采集到的信息量远远大于低速采样。高速采集、高速存储和高速处理成为发展的必然。这其中,高速传输通道是芯片间的数据桥梁,一般要求10 Gbps以上的处理速度,实时传输至少要达到几Gbps。在设备之间,采用万兆网、USB3.0、光纤通信等;在板间,采用PCIe、VPX等;而在芯片间,采用SRIO(也称RapidIO)总线是常用方法。

多核处理器片内集成多个处理器,目前得到大规模使用;同时多核处理器的强处理能力,也丰富了产品的功能。为了支撑功能使用,一般多核处理器都会配置大容量DDR2或DDR3,运行程序和存储数据,还配置共享RAM空间用于多个核之间的通信,每个核还有自己的私有RAM。一旦其他芯片和多核处理器进行数据交互,可能会和这3个RAM空间进行高速通信。传统的单处理器交换一定需要CPU参与,CPU读取数据,然后存储到芯片的DDR、片内RAM或者片外Flash空间。但这样,每个数据交互都需要CPU参与,严重影响了运行效益。而多核处理器,数据交互远比单核处理器频繁,而且要求交互速率也非常高,这就需要数据总线直接进行交互,而不用CPU参与[2]。

本文以8核DSP芯片TMS320C6678(以下简称C6678)和xck7325t芯片为例,通过4线SRIO实现FPGA将数据直接传输到DSP的DDR3、共享片内RAM的方法。笔者给出了软硬件设计方法,研究了硬件平台,实际数据传输验证,该方法可以实现4 Gbps的高速传输。

1 多核DSP的RAM结构

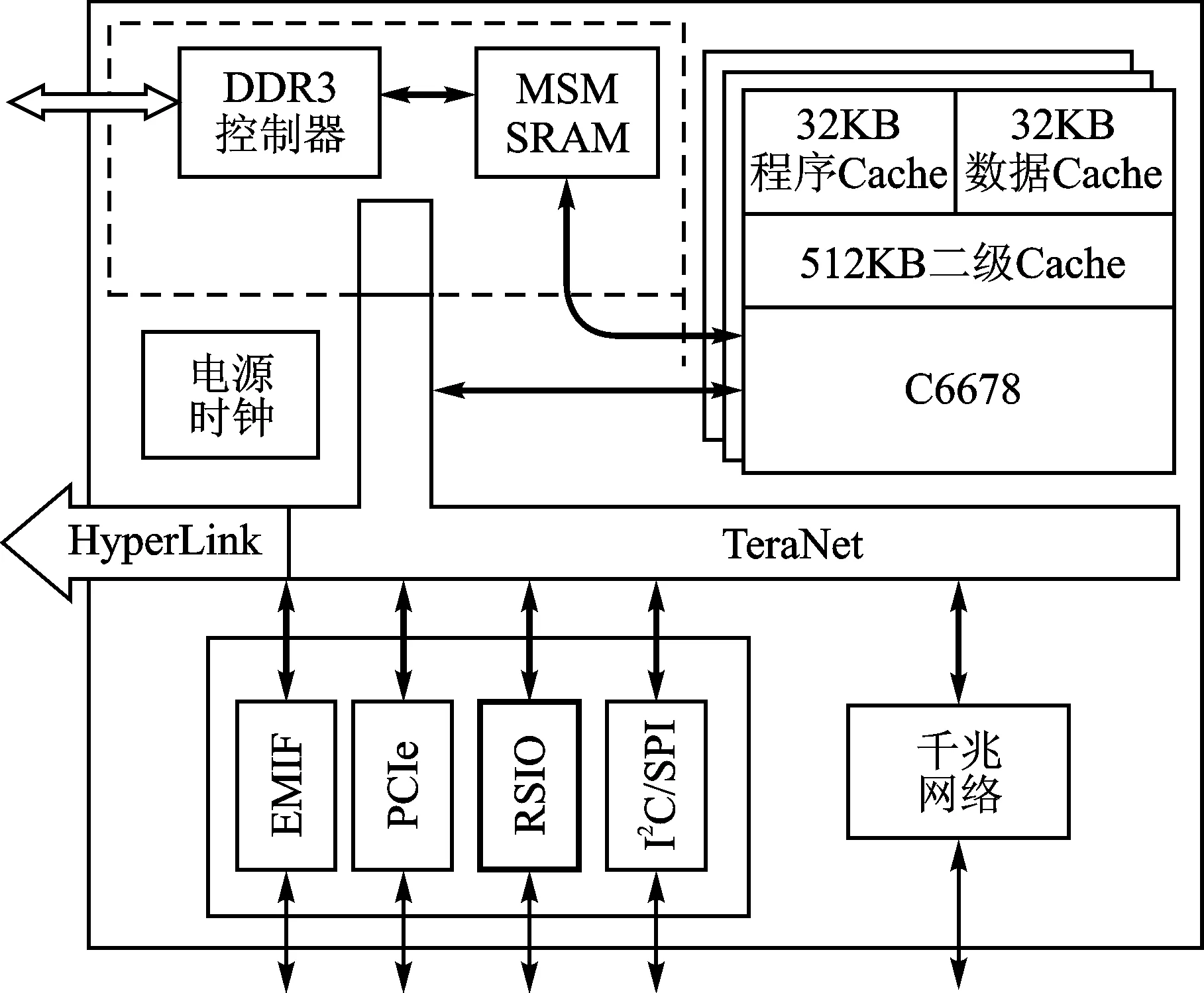

C6678是TI公司多核处理器中的一款8核浮点型DSP,最高工作频率达到1.25 GHz,单个核具备40 GMAC定点计算或20 GFLOP浮点计算能力,单芯片具备320 GMAC或160 GFLOP的计算能力[3]。C6678的部分片内结构如图1所示。

图1 C6678内部结构图

图1主要列出了C6678和RAM相关的片内模块,其他部分未列出。从图中可以看出,一个超高速的TeraNet(兆兆网络)总线将大部分模块连接在一起,数据通过TeraNet总线进行交互。核访问共享RAM(图中的MSM SRAM)的速度最快,它们之间不通过TeraNet,而是有专用的数据总线,不会和其他外设产生冲突,核访问共享RAM的速率大概在50 Gbps。核访问DDR3的速度仅次于共享RAM,因为DDR3的数据需要通过共享RAM过渡,其读写访问速度有所差别,读速率至少可以达到10 Gbps,写速率可以达到20 Gbps。核访问其他片内和片外设备都要经过TeraNet,可能存在总线仲裁,但这些外设一般不会长时间占据TeraNet总线。

本文关注的SRIO是直接挂在TeraNet总线上的,而C6678的DDR3控制器、共享RAM、512 KB的二级Cache都是连接在TeraNet总线上,所以,SRIO可以直接和这3个RAM进行通信,但需要一定的时序控制,否则会造成RAM的互锁,增大仲裁开销,甚至程序死机。具体表现在:

① 和DDR3进行通信。因为DDR3一般会运行主核程序,尤其是需要使用网络接口,TI提供的NDK程序代码很大,必须在DDR3中运行。这样程序运行的DDR3地址,SRIO不能盲目进行读写,尤其是写操作,此外如果SRIO和程序需要同时读某一地址,就会造成总线冲突。

② 和共享RAM进行通信。共享RAM是用于多个核之间的数据交互,几个核对共享RAM的某个地址进行操作,一定需要一个控制权抢占,谁抢占到控制权谁就可以操作,其他核只能等待,这样就避免了多个核同时访问共享RAM的问题。如果SRIO对共享RAM进行操作,一定需要将SRIO加入核之间的控制权抢占以及释放。

③ 和每个核私有RAM进行通信。理论上,SRIO可以和每个核的L1数据空间、L1程序空间、L2空间进行通信。但一般程序会将L1的全部数据和程序空间、L2的部分空间定义为Cache,用于存储程序运行的中间结果,例如局部变量。程序在调试过程中的打印输出等也需要较大的堆栈来处理,这些堆栈空间都在私有RAM中由SYS/BIOS自动开辟。如果SRIO将数据写入到这些空间,将很可能造成地址的同时读写,所以建议SRIO不对这些空间进行操作。

2 SRIO的硬件连接

FPGA和DSP的SRIO硬件连接如图2所示。SRIO总线由收发各4对差分线(一共16根线)组成。DSP的RIORXp0~3为4根收数据的正端,RIORXn0~3为一一对应的4根收数据的负端,它们和FPGA相应的8根发数据连接,形成一个FPGA发、DSP收的回路。另外8根线形成一个DSP发、FPGA收的回路。所以,在物理层,SRIO的收发是完全独立的,可以做到收发全双工。为了提高SRIO传输可靠性,在靠近收方的总线上,需要采用隔离电容,将信号直流隔掉,使得差分信号更加可靠。SRIO的时钟由各自的处理器单独设置,不要求DSP和FPGA共用SRIO时钟。SRIO的传输时钟是叠加在传输数据上的,由SRIO处理器从数据总线提取出时钟信号,用于数据位的对齐。这些处理工作,均由各自芯片的SRIO模块完成,不需要用户设置[4]。

图2 硬件连接图

图2中,DSP外挂了5片DDR3,每片DDR3为16位数据宽度,4片组成64位数据宽度,直接连接到DSP。第5片连接到DSP的数据校验位,每个64位的数据通过BCH编码生成一个8位的校验码同时存放到第5片DDR3中,DSP读取DDR3数据时,也同时把这个校验码读出,进行BCH译码。如果译码正确,则表示数据可靠,否则会尝试重读或多次失败后丢弃数据。此外BCH码具有一定的数据纠错能力,也可以提高DDR3数据的读写可靠性。经过实际验证,由DSP直接读速度达到10 Gbps,写速度达到20 Gbps。

由于DSP有多个外设,这些外设需要一个基准时钟,这样就方便时序和同步控制,图中采用CDCM62005对输入的125 MHz时钟进行分频,输出多路CLK信号,分别提供到SRIO、DDD3模块,以及DSP的运行主时钟。实际上还可以提供给DSP的网络模块、PCIe等模块。

3 软件设计

软件设计主要包括各个模块的初始化、数据读写、中断响应和任务控制等。

3.1 DDR3的软件设计

DDR3的软件设计包括初始化、读/写数据和刷新控制等。由于DDR3是依靠电容的充放电状态来存储信息,就需要定时刷新来维持电容的状态。定时刷新由处理器的片内模块自动完成,用户不需要参与。DDR3的初始化顺序为:

① 配置DDR3的PLL,通过设置PLL寄存器中的clkr、clkf、clkmod以及bwadj位来确定DDR3的工作时钟。

② 延迟一段时间,等待PLL设置有效。

③ 清除RESET,使得PLL进入工作状态,查询PLL锁定标志。锁定标志有效,表示初始化过程结束。如果DDR3芯片及其周边电路存在问题,PLL就会无法锁定。这些问题可能包括:电源不稳定、时钟抖动大以及硬件错误等。

3.2 SRIO的软件设计

SRIO的软件设计包括初始化、数据读写和中断响应等。SRIO的软件设计包括了FPGA和DSP两个芯片,所以两个芯片的大部分参数设置需要保持一致。此外,一旦SRIO的数据链路建立好后,一方不能自行单独复位SRIO模块,否则将出现双方不能同步现象,SRIO数据不能正常通信。所以,一旦一方要求复位,必须通知对方。在程序中,建议在SRIO链路建立后,不进行复位操作。SRIO的初始化顺序为:

① 配置SRIO的工作时钟,SRIO需要从低速时钟倍频到高速时钟,最低到1.25 Gbps,最高支持5 Gbps。一般电路板设计和制造后可以达到2.5 Gbps或者3.125 Gbps的时钟速率。如果再采用4线制传输,传输数据速率可以轻松达到10 Gbps或者12.5 Gbps。

② 等到SRIO时钟设置好后,按照先使能接收器,再使能发送器的顺序复位自身的模块,如果另外一方也设置好后,会看到连接寄存器的状态位变化,表示双方链路已经建立;如果状态位没有变化,则说明存在硬件或者设置上的问题。

③ 设置数据收发中断,可以以SRIO自身中断,也可以以GPIO触发另外中断的方式。

3.3 SRIO传输数据到DDR3

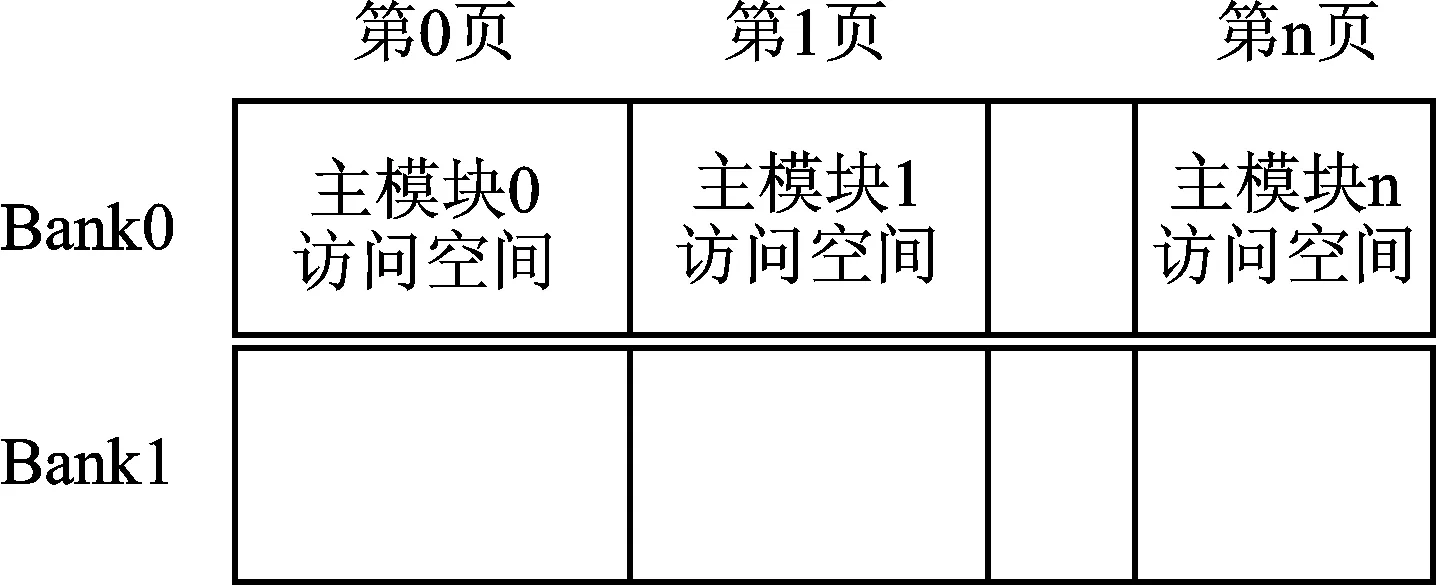

多核DSP的程序代码一般在DDR3中运行,一旦SRIO也对DDR3进行操作,就存在多个主模块共享DDR3的问题。DDR3控制器只有一组总线与DDR3连接,一旦出现多个主模块同时访问DDR3时,必须要根据优先级进行总线仲裁。DDR3的访问以页为基础,一个主模块访问某个页之前,必须要打开该页。DDR3最高具有8个bank,每个bank可以打开一页,最多同时打开8页。但如果想同时访问一个bank中的2页是不可能的,只有关闭掉其中一页,才能访问另外一页,这就存在页切换的问题。

图3是多个主模块访问同一bank下的不同页,这是切换最频繁的情况,每次访问都要进行页切换,导致传输效率大大降低。如果SRIO将数据传输到这些页,存在很大的风险。虽然DDR3控制器可以进行总线仲裁,但对于SRIO的传输端FPGA,不清楚总线是否被占用,仍然传输数据,将会导致数据丢失,所以不建议SRIO用这种情况访问DDR3。

图3 多个模块访问同一bank的页

图4是多个主模块访问不同bank不同页的情况,这是最简单的情况,因为每个主模块访问的bank和页均不同,所以不存在任何页切换情况,总线传输很快。但图中的空白页将无法访问,一旦访问,将回到图3所示的情况,导致大量DDR3空间不能使用,所以不建议SRIO用这种情况访问DDR3。

图4 多个模块访问不同bank的不同页

图5是图4的简化访问方式,这种方式只存在

High-speed Communication Between Multicore DSP and FGPA Based on SRIO

Wang Anmin1,Han Daowen2,Xu Yan3

(1.Research of Tongfang Science and Technology Ltd.,Jiujiang 332009,China;2.Electronic Engineering Institute 3.Harbin Institute of Techonlogy)

High speed data communication between the different processors is needed in the high sampling system.The SRIO bus is used widely because it’s high efficiency and low latency.In this paper,the design method of SRIO bus between FPGA and DSP is studied.The data translation is realized from FPGA to DDR3,shared RAM or private RAM of DSP.In this paper,the hardware system is developed,and the operation method of the software and the verification of the actual hardware platform are given.The result of data throughput is up to 4 Gbps by the SRIO bus in the real system.

multicore processor;SRIO;shared RAM

TP336

A